- 1jupyter服务器搭建及多用户同时使用方法_jupyter notebook 多用户同时使用

- 2YOLOv7-Pose 姿态估计-环境搭建和推理

- 3最强鸿蒙系统txt_华为鸿蒙不是要和谷歌、微软瓜分市场,而是想取代安卓、windows...

- 4Android Studio 单独编译WebRTC的 vad 模块_execinfo.h' file not found

- 5鸿蒙快速入门--初识HarmonyOS

- 6Django Cache缓存系统介绍及Memcached使用_django cache_control()

- 7SSM整合项目(校验)

- 8JavaScript 变量的概念、变量的使用、数据类型_js变量的概念

- 9一文看懂Android.bp和Androd.mk区别以及宏变量对应关系_android.bp 宏

- 10第一个Swift程序 - Helloworld_swift helloworld

Vitis AI修炼秘籍2. 熟悉Vitis软件的使用之LED驱动_zynq7020运行vitis ai

赞

踩

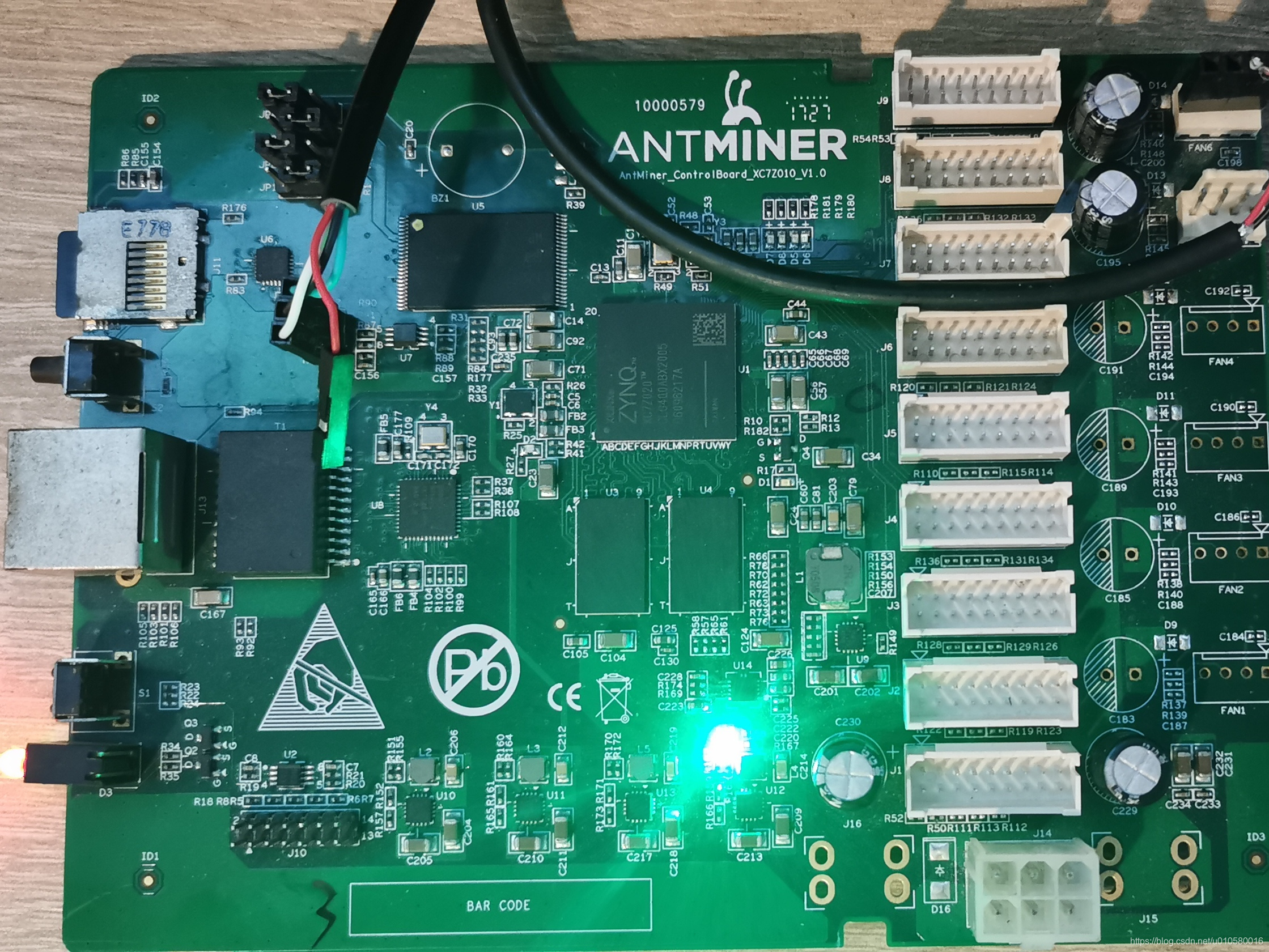

深度学习DPU IP最低配置下,至少需要38457 LUT,而ZYNQ 7010只有35500 LUT,本来笔者是有一块7Z010的开发板,奈何资源不够,无法使用Vitis的核心功能。由于笔者比较穷,买不起ZED Board这样的贵的开发板,因此,笔者花了180RMB在某鱼上淘了一块矿机上使用的ZYNQ控制板,板子上的芯片正好是ZYNQ 7020 (XC7Z020CLG400)。

为了Bring up这块暂且称之为开发板的板子,取名为ANT开发板,本篇笔记以点亮图中所有的LED为目的,回顾下Vivado的使用,并且开始了解Vitis的开发流程(原来开发环境为SDK)。

开发环境

- Windows 10 64 bit

- Vivado 2020.2 & Vitis 2020.2 64 bit

- XC7Z020-1-CLG400

一. 构建硬件环境

1.1 创建Vivado工程

1.1.1 创建空白的工程

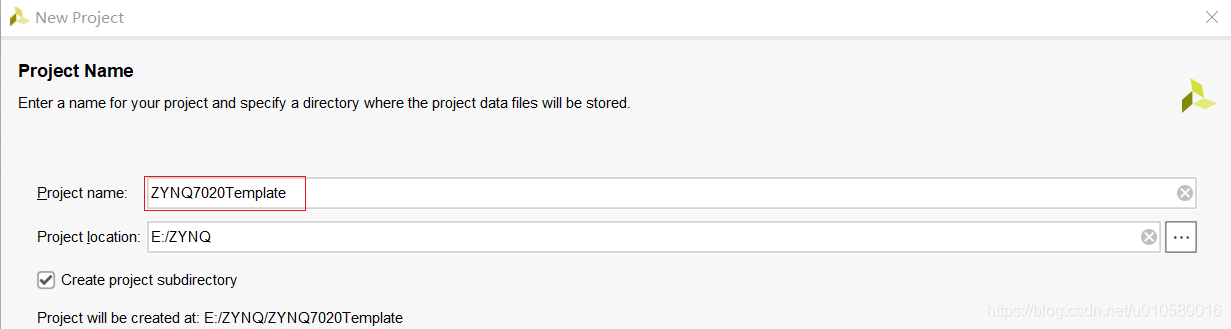

打开Vivado软件,File -> Project -> New创建一个空白的Vivado工程,工程名取名为ZYNQ7020Template,因为以后要用的工程以这个工程为模板进行添加新的硬件。

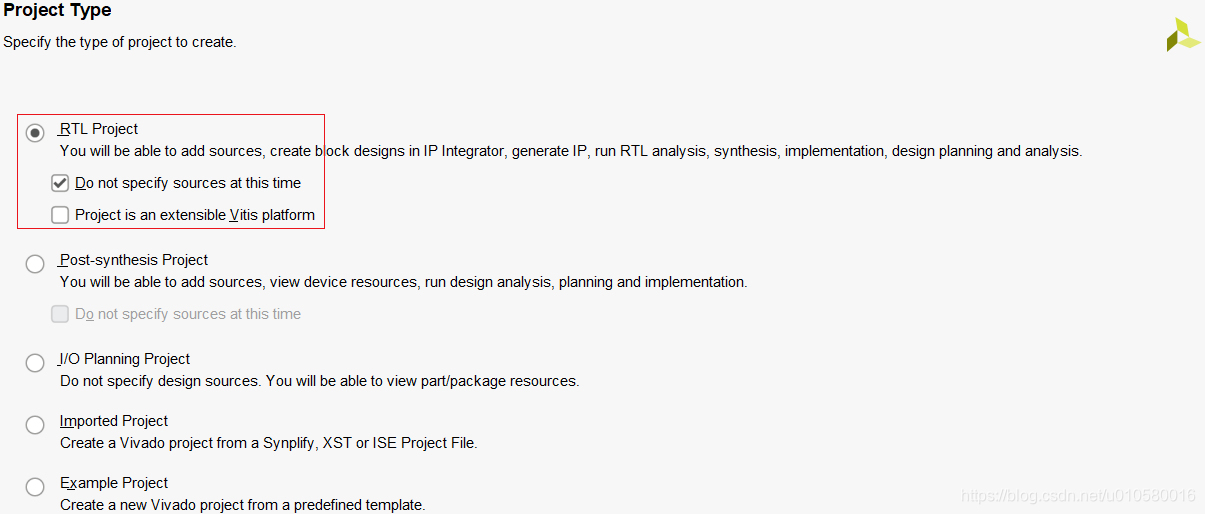

点击 Next >,选择RTL Project

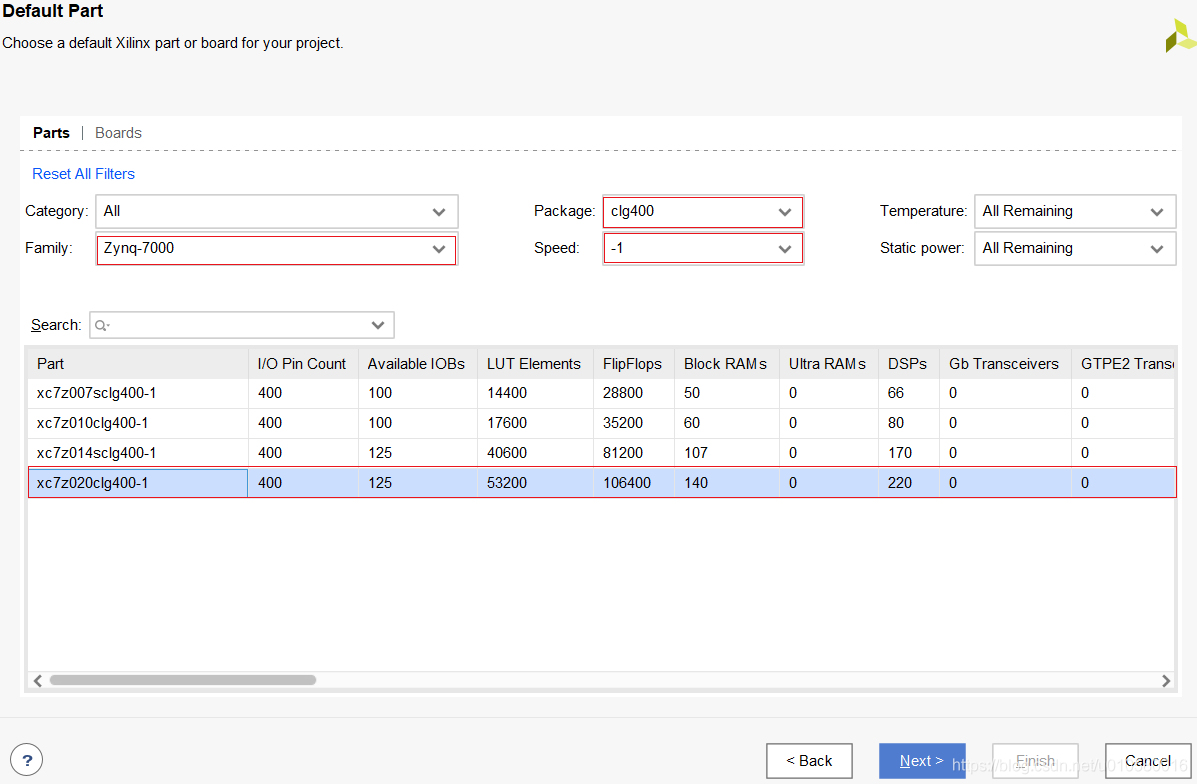

点击 Next >, Family选择Zynq-7000, Package选择clg400, Speed选择-1,在筛选出来的列表中选择xc7z020clg400-1。

点击 Next >,在点Finish即可完成空白工程的创建。

1.1.2 添加ZYNQ IP核

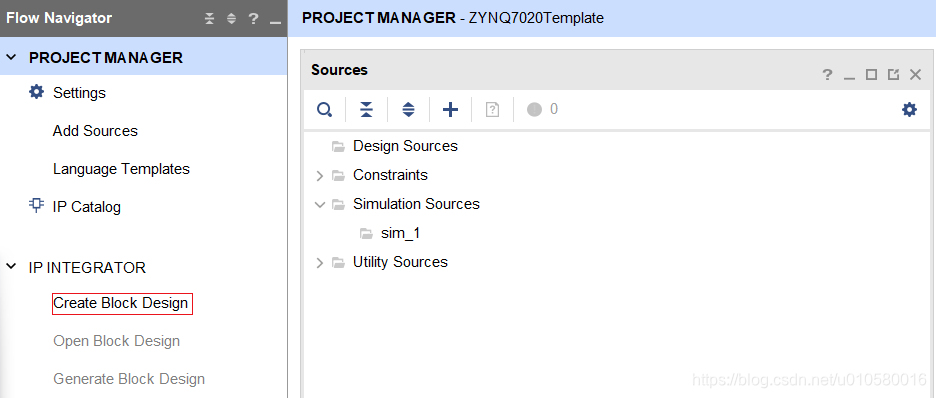

在PROJECT MANAGER的IP INTEGRATOR中点击Create Block Design,创建一个硬件原理图文件。

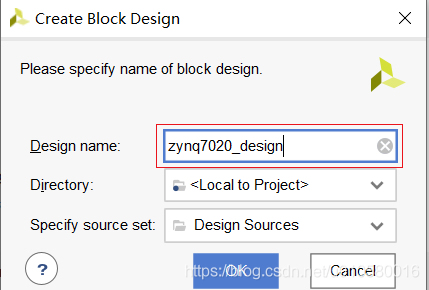

原理图取名为zynq7020_design,点击OK。

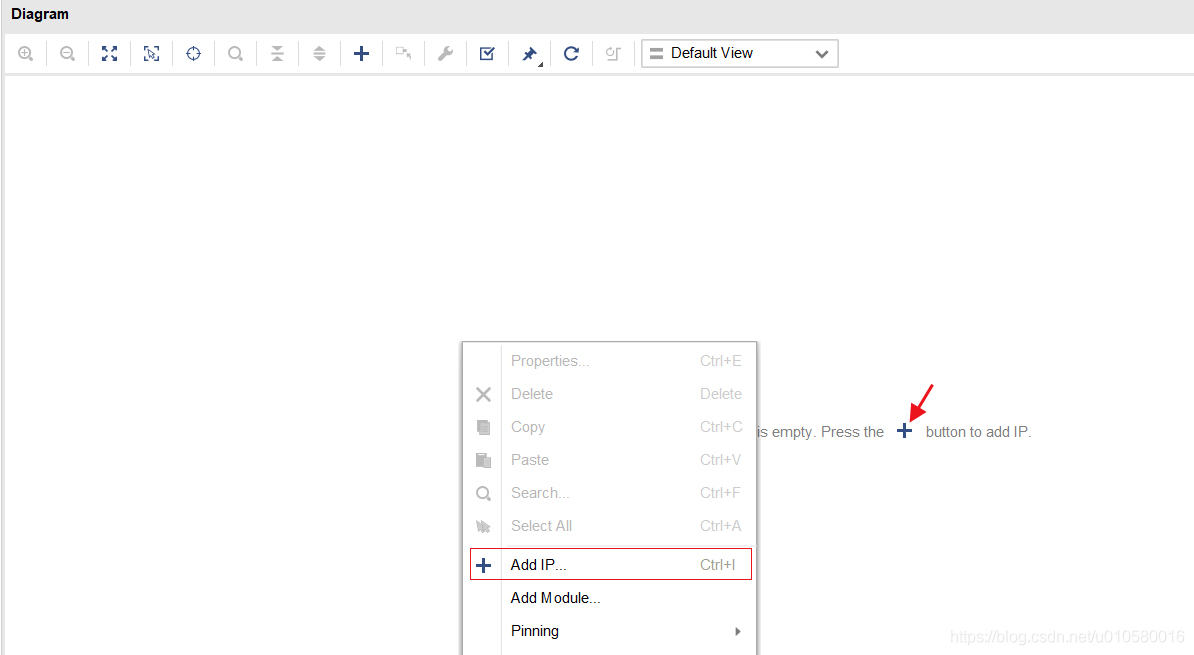

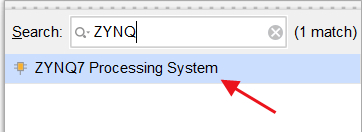

在Diagram中点击+号图标或者在空白处右键单击,选择弹出菜单中的Add Ip...选项。

输入ZYNQ

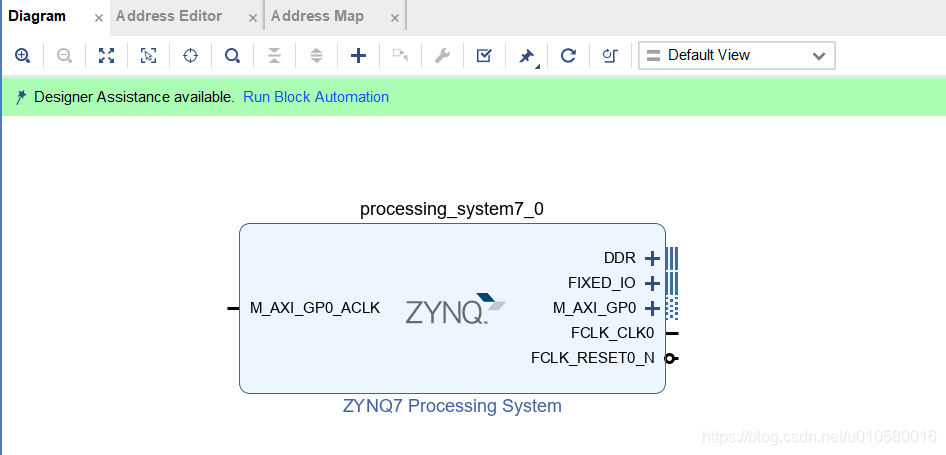

双击筛选出来的ZYNQ7 Processing System,则ZYNQ处理器IP添加到原理图中。

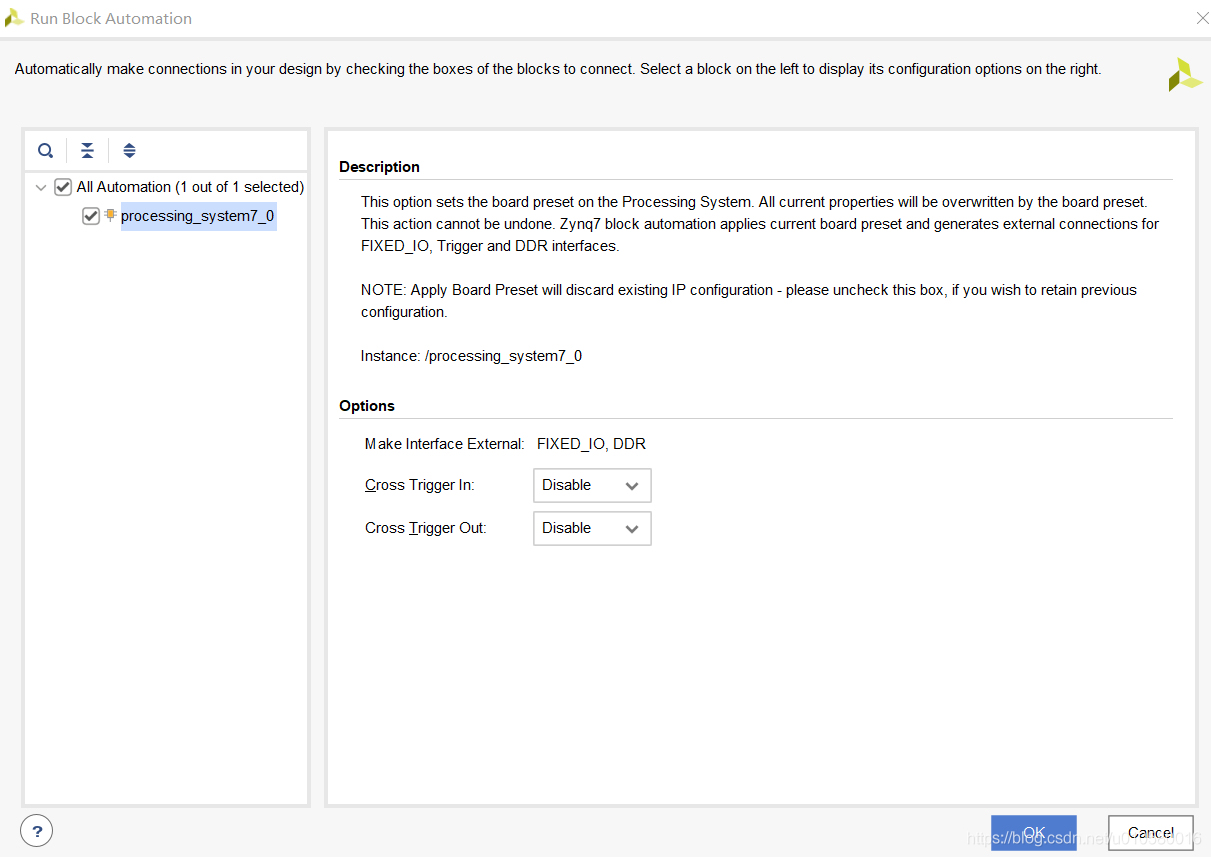

点击弹出的Run Block Automation链接

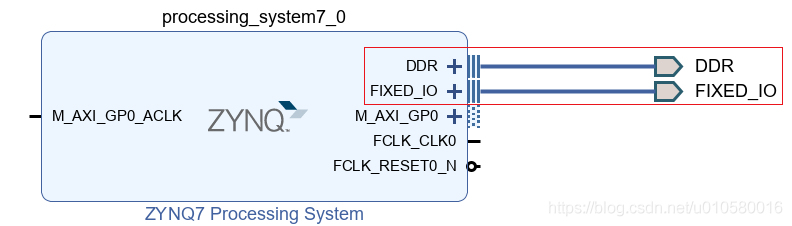

直接点OK即可,这一步操作是为了添加DDR端口的硬件以及一些其它固定的IO,如下图所示。

1.2 配置外设

由于这个开发板是自己淘的,没有官方标准的模板工程,相关的硬件配置都必须自己根据电路原理图进行设置。最基本的外设需要设置的有DDR,UART,LED,SD Card,其它外设例如Ethernet, Nandflash,Switch等在后续逐步添加完善。本文只只需要设置前面的四种外设即可点亮LED,输出打印信息。

1.2.1 配置 DDR

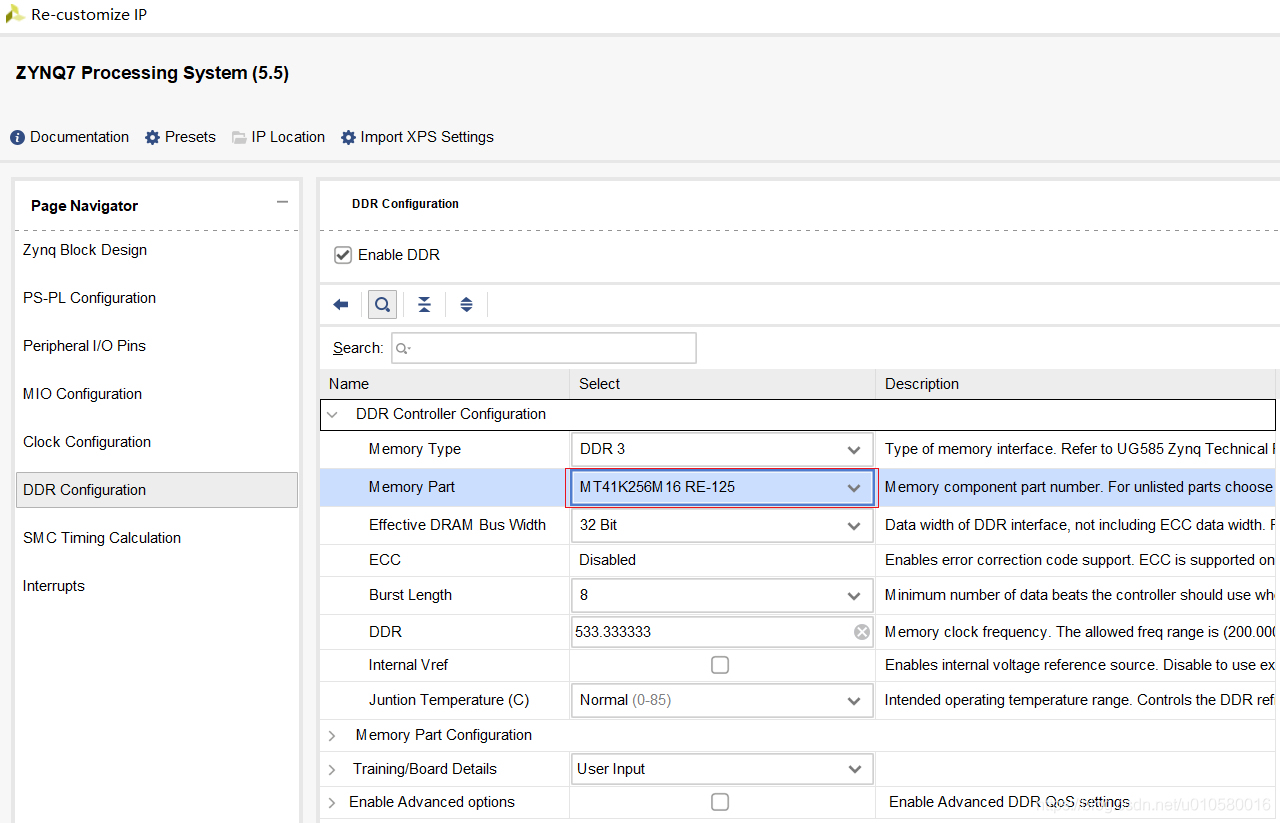

开发板上的DDR为两片16 bit数据位的MT41K256M16HA-125:E芯片。

双击ZYNQ7 IP核,在弹出的Re-Customize IP界面选择DDR Configuration->DDR Controller Configuration -> Memory Part

发现没有完全匹配的,那么选择最相似的MT41K256M16 RE-125。

1.2.2 配置UART

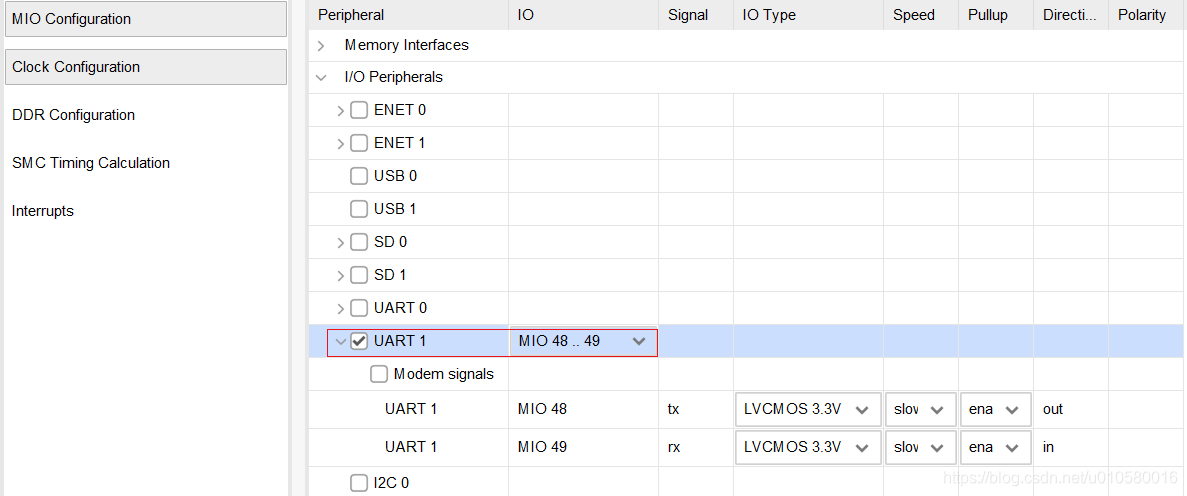

开发板上的串口接在了PS MIO 48和PS MIO 49引脚上,因此配置输出串口为UART1.

选择MIO Configuration->I/O Peripheral,勾选UART 1,MIO引脚选择48,49.

1.2.3 配置SD Card

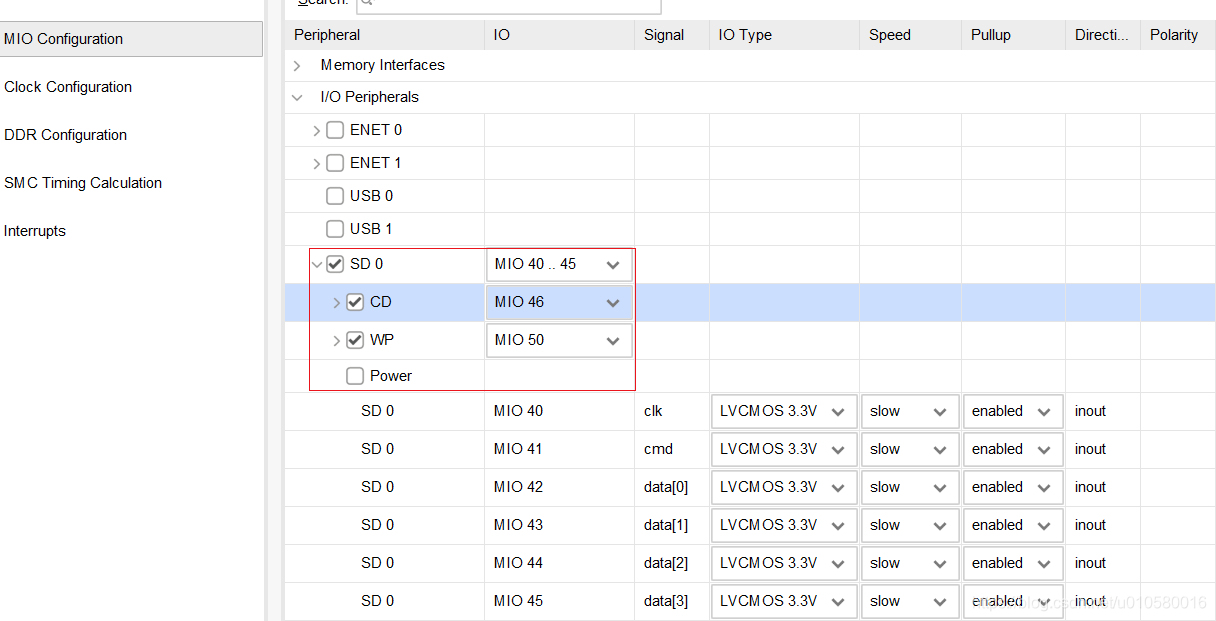

根据开发板上的SD卡连线,配置SD Card的引脚。

选择MIO Configuratiion->I/O Peripherals,勾选SD0,MIO引脚选择MIO 40~45, CD引脚选择MIO 46, WP选择MIO 50, Power引脚无需选择。

1.2.4 配置LED

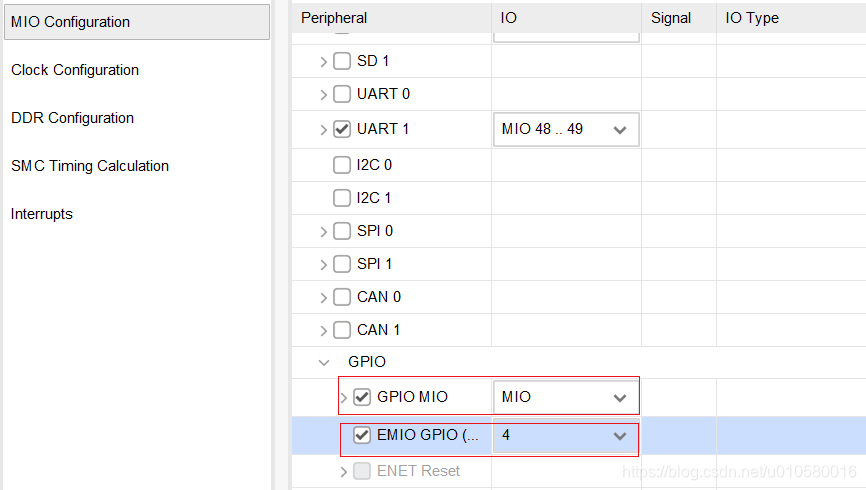

ANT开发板上有7个可以用IO进行控制的LED,对应的引脚如下表所示:

| LED_R | LED_G | D2 | D5 | D6 | D7 | D8 |

| MIO37 | MIO38 | MIO15 | L7P | L8P | L6P | L9P |

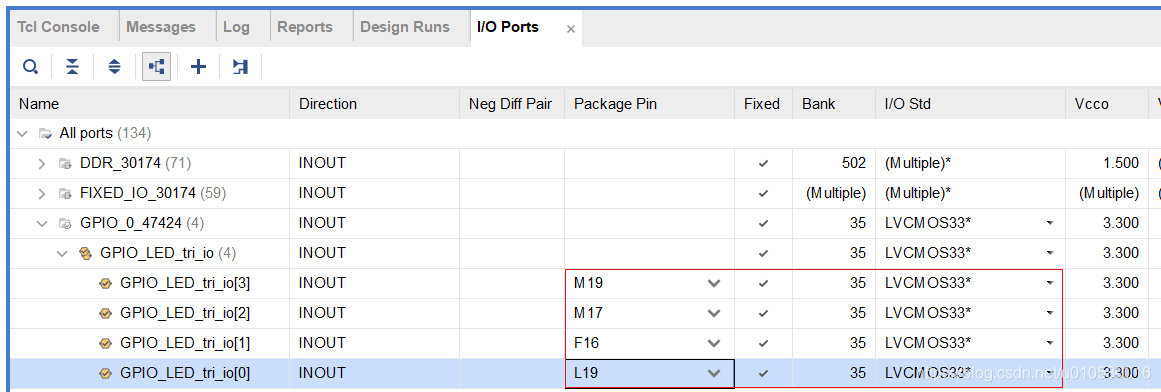

| M19 | M17 | F16 | L19 |

前三个LED使用的MIO,勾选GPIO MIO,后四个为PL的引脚,因此选择EMIO GPIO,width选择4,如下图所示:

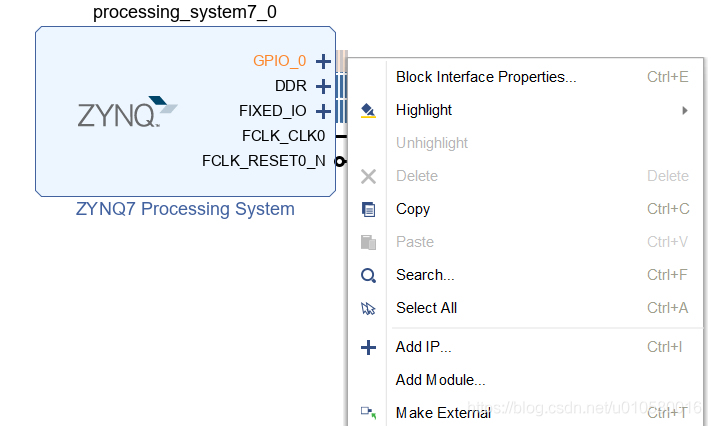

配置了EMIO后,ZYNQ7 Processing System IP中多出了一个名为GPIO_O的端口,此时为这个端口引出IO,右键选择这个端口,选择Make External。

添加IO引脚之后如下图所示:

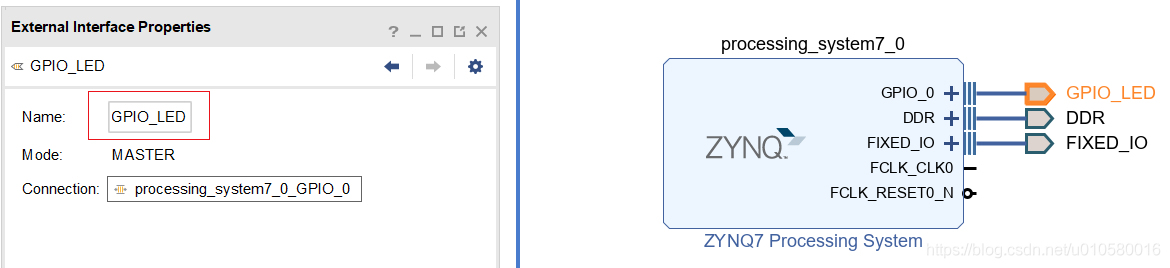

可以考虑在左侧的属性栏度这些IO进行重命名,例如命名为GPIO_LED:

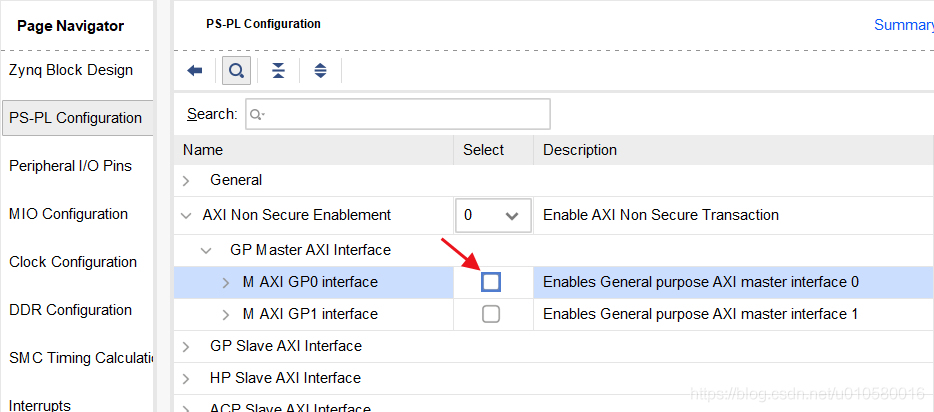

由于目前没有使用到GP0端口,暂时先关掉。

1.3 编译Vivado

1.3.1 编译综合

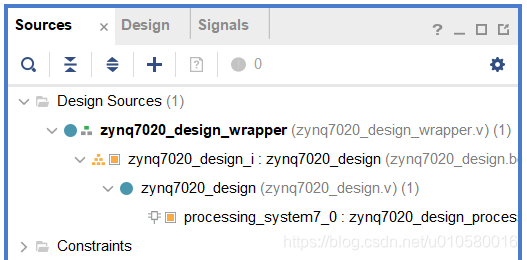

第一次创建的原理图文件需要生成HDL文件,然后进行综合。右键选择zynq7020_design.bd文件,选择Create HDL Wrapper...,

生成完成后如下图:

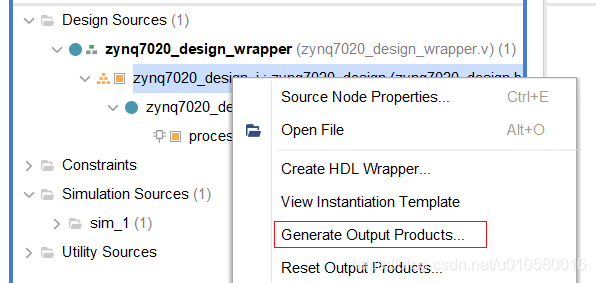

再右键选择zynq7020_design.bd文件,选择Generate Output Products...

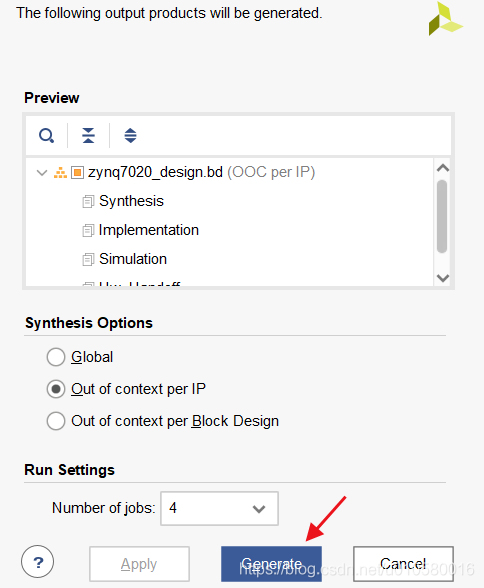

直接点击Generate,等待片刻。

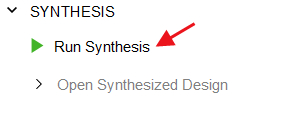

点击综合

1.3.2 分配引脚

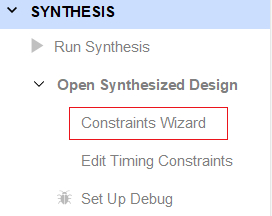

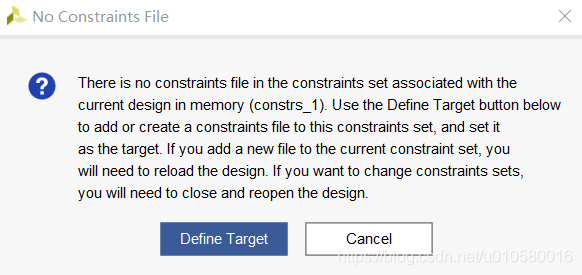

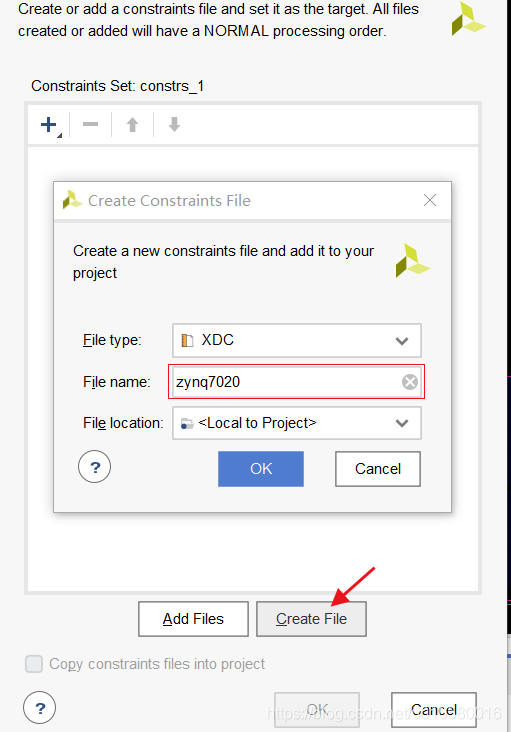

由于LED5~LED8使用了EMIO,需要为其指定IO引脚。点击Open Synthesized Design下的Constraints Wizard。

为目标平台添加并设置约束文件。

创建一个名为zynq7020.xdc的约束文件。

选择自己创建的文件,并点击OK。

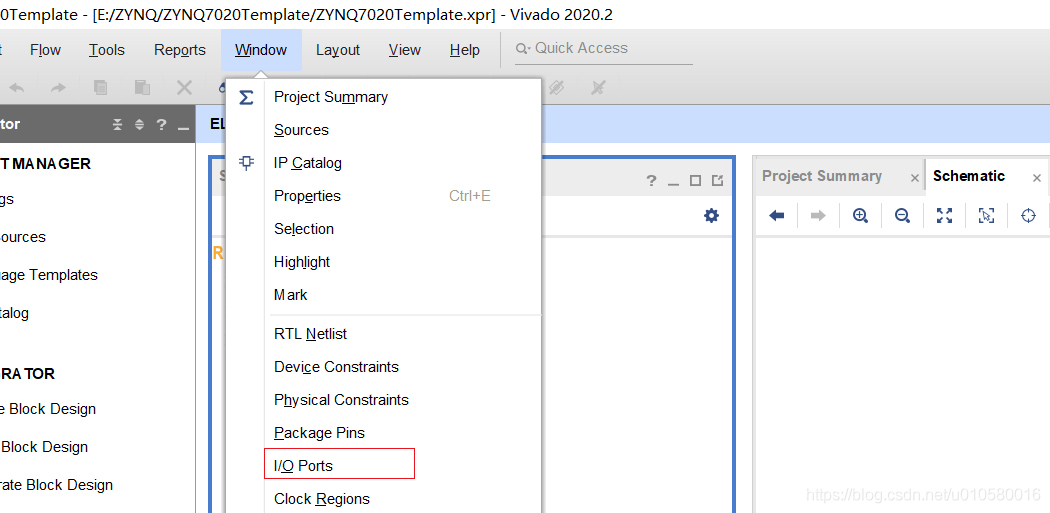

在菜单栏选择Window-> I/O Ports,

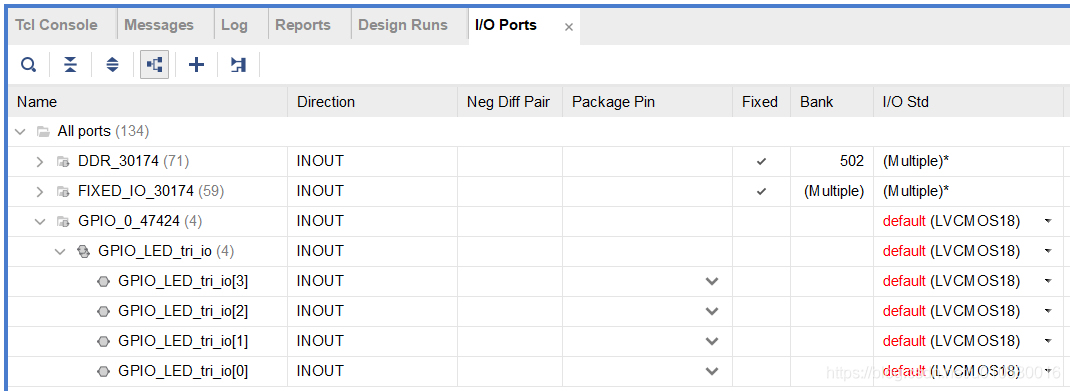

未分配的如下图所示:

在下方的I/O Ports中对GPIO分配引脚。注意,LED GPIO的引脚点平修改为3.3V。

1.4 生成bit流并导出

先点击Run Implementation,成功之后,再点击Generate Bitstream。

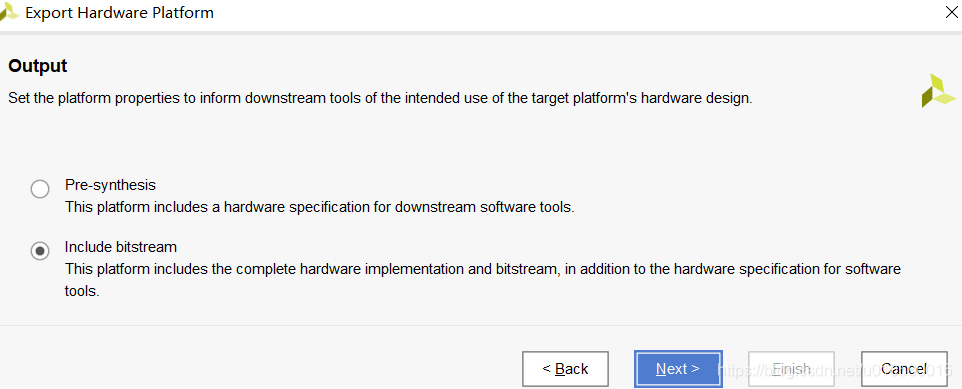

导出XSA文件,File->Export->Export Hardware...,Next,输出类型选择Include bitstream,点击Next。

此处切记,即使只使用了EMIO的引脚,也要包好bitstream,笔者在这里掉坑里了,因为没有勾选这个使用了EMIO的LED一直无法点亮,尝试过电压表测量电压,反复检查原理图等...

路径使用默认文件名即可,点击Next,完成导出。

二. 构建Vitis软件

2.1 创建Platform工程

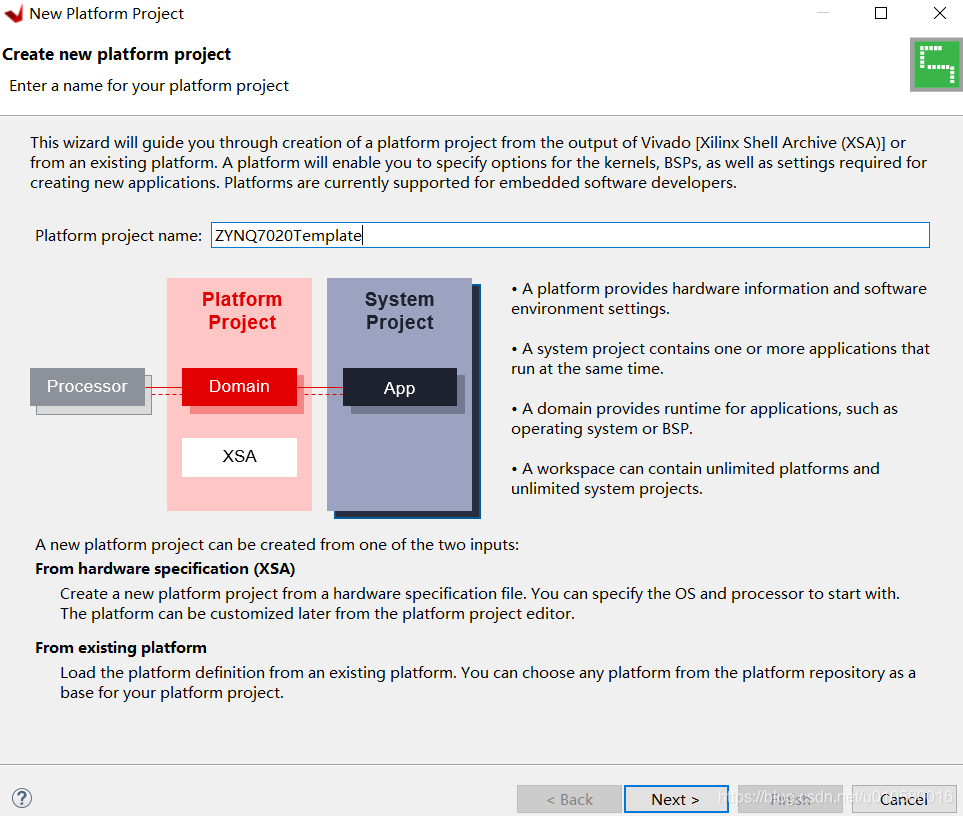

Vitis菜单栏File->New->Platform Project,输入自定义的Platform名称,下一步。

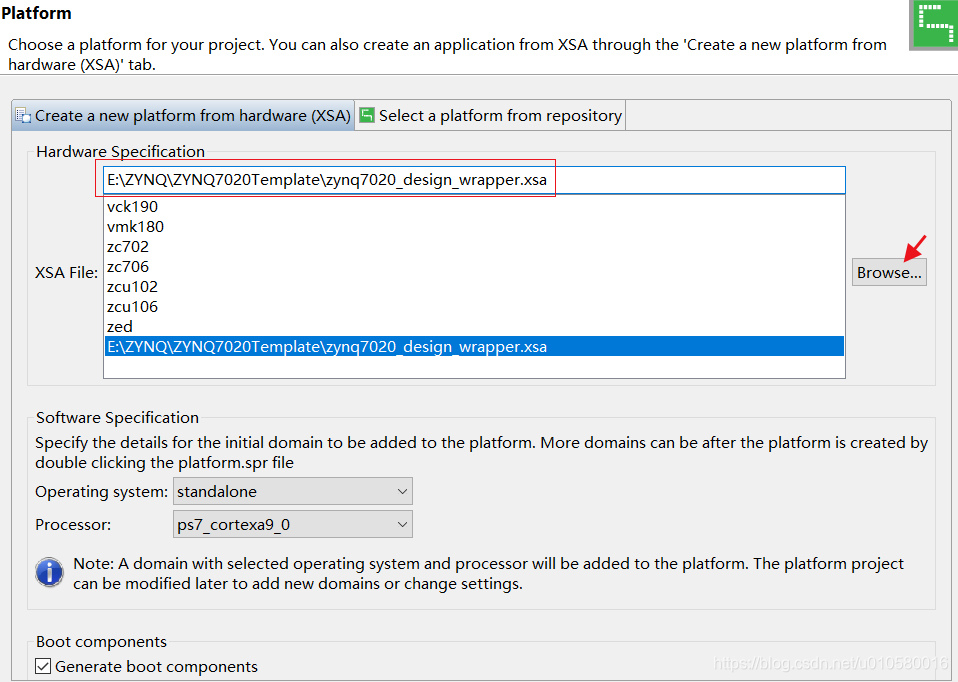

选择Create a new platform from hardware(XSA),选择上一节从vivado导出的zynq7020_design_wrapper.xsa,其它默认。

2.2 创建应用程序

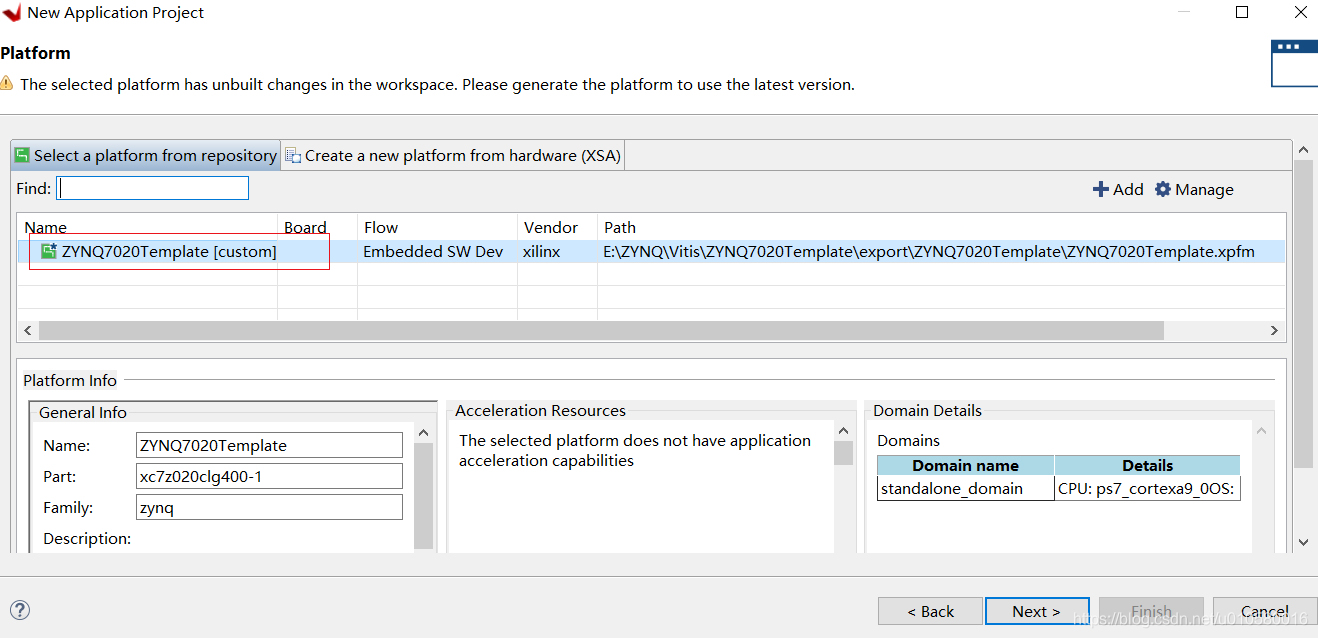

Vitis菜单栏File->New->Application Project,选择从刚才导入的ZYNQ7020Template [custom]为平台创建应用程序。

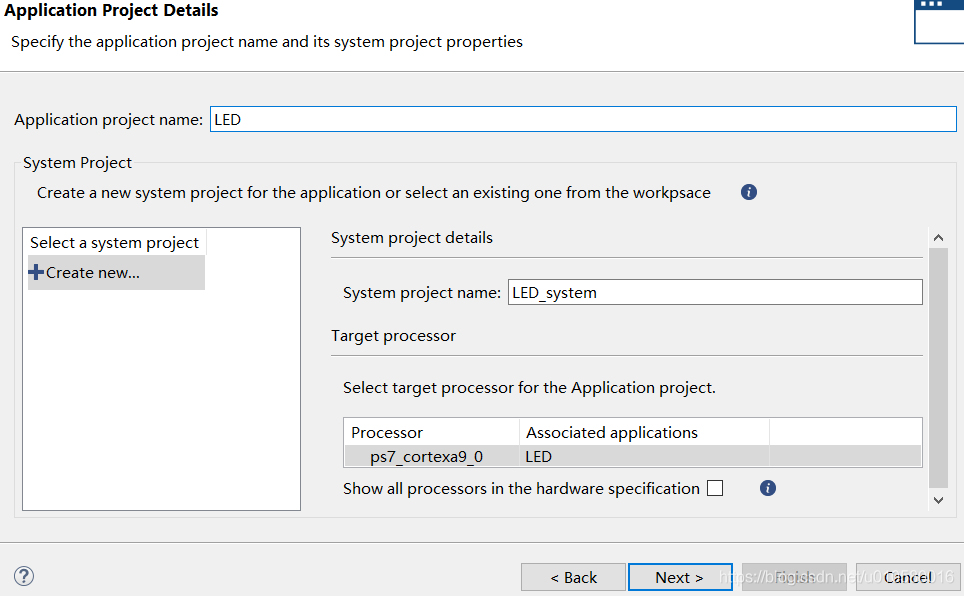

下一步,输入工程名,LED。

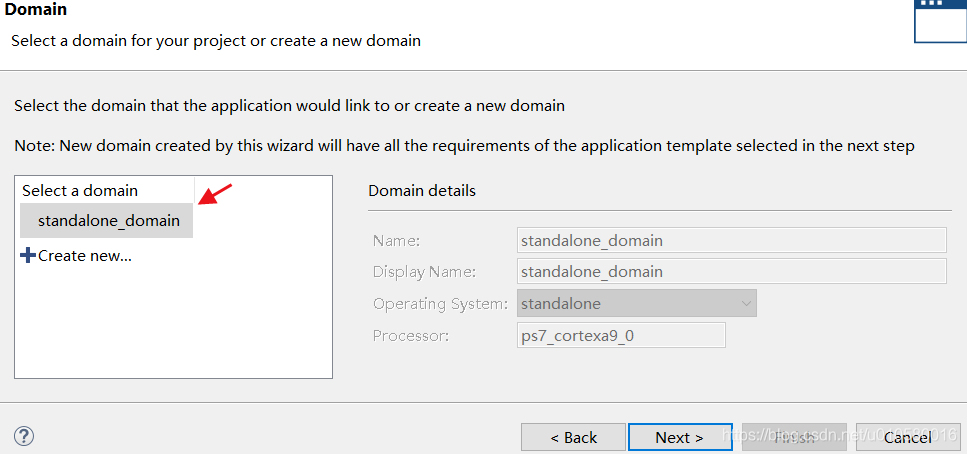

操作系统选择裸机系统:

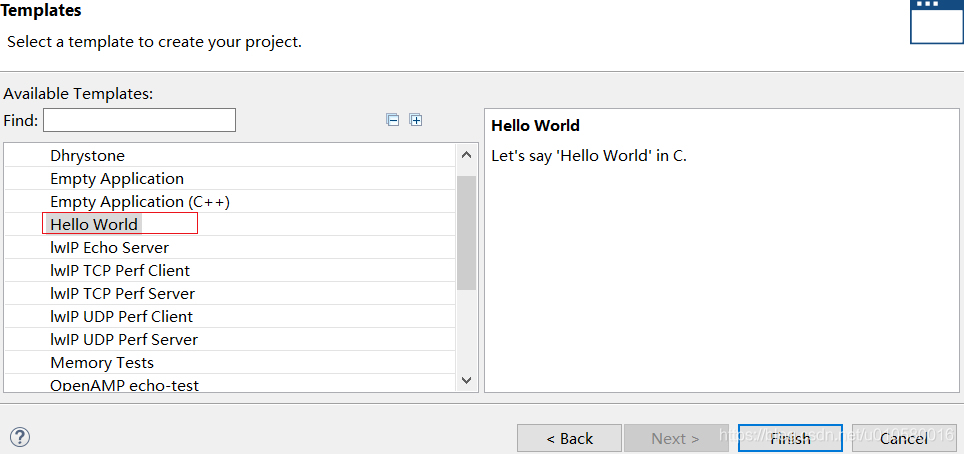

然后从Hello World模板工程创建应用程序,点击Finish完成。

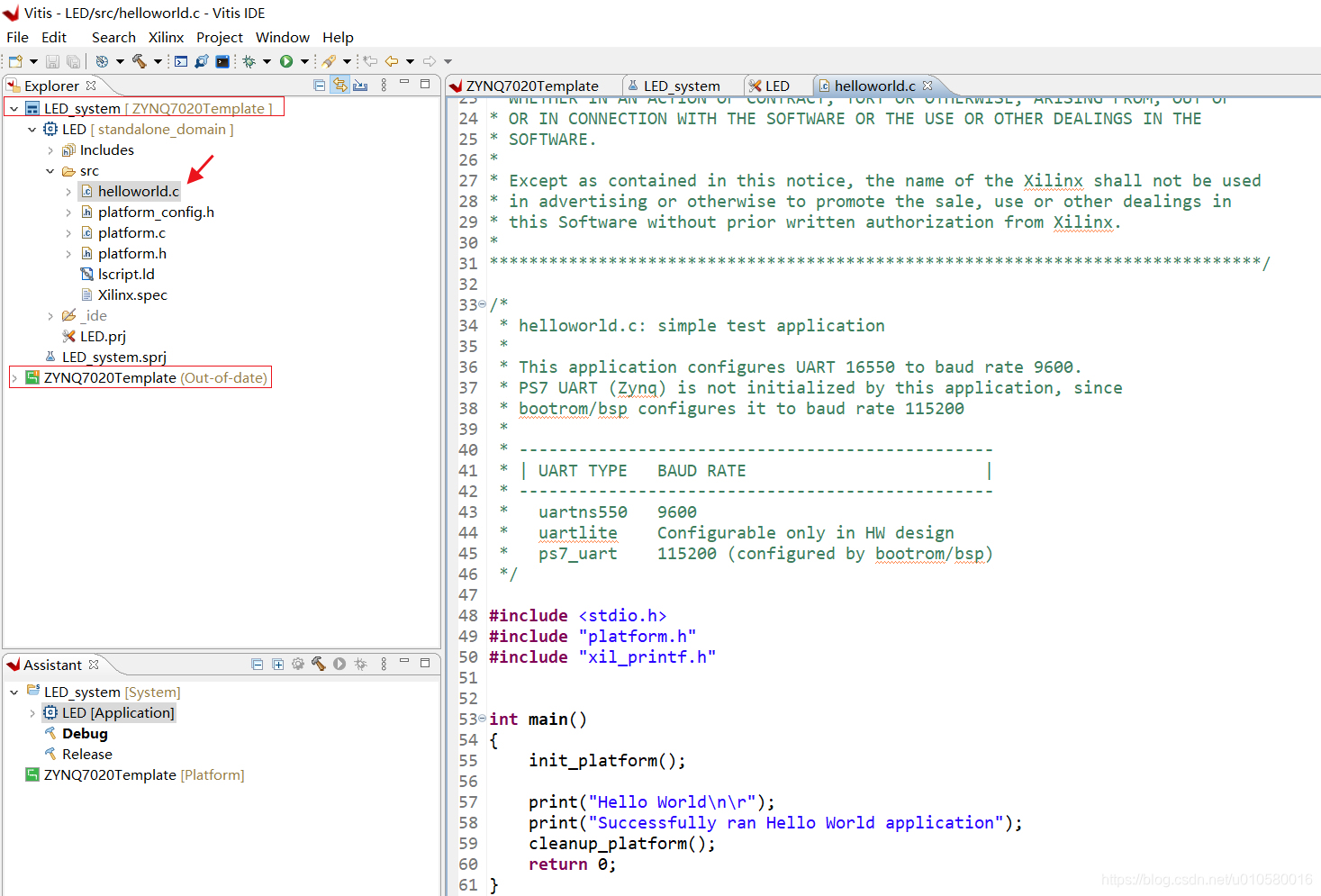

创建完成之后如下图所示。

至此,基本的硬件与软件工程都以经创建完毕,剩下的就是自己的代码逻辑了。可以看出来,与Vivado2019版本之前的工程的使用上有些许的差异,这些差异列举如下:

1) 不在是从vivado启动SDK,已集成到Vitis IDE

2) 需要自己创建platform,之前的SDK会自动创建

2.3 编写LED程序

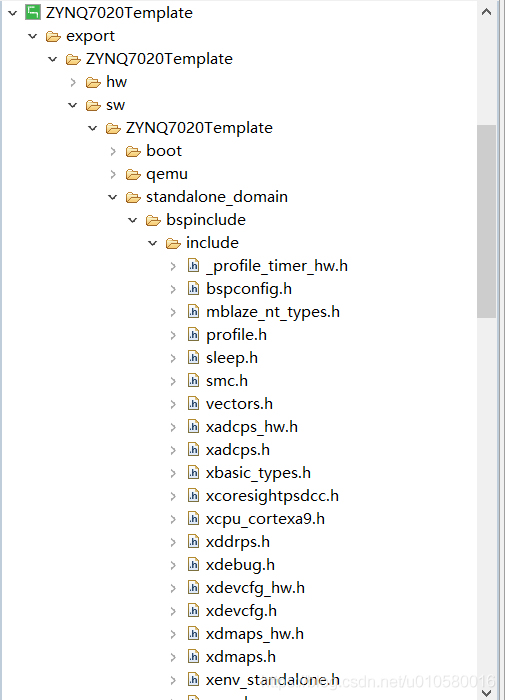

首先编译下Platform工程,这样Vitis IDE会生成bsp库。其中GPIO库为xgpiops.h

三. 调试运行

编译工程,编译完成之后在工程文件夹的Debug/sd_card目录下生成了BOOT.BIN的启动文件。可以让板子启动运行程序有两种方法,一中是SD卡启动,一种是仿真器运行。当然还可以从其他存储器启动,在此不做介绍。

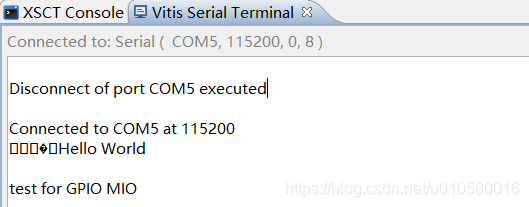

启动串口终端,先监听者开发板的串口输出。

串口终端可以使用第三方的软件,也可以使用Vitis自带的串口终端,打开方式如下:Window->Show View...->Xilinx->Vitis Serial Terminal。

3.1 SD开启动

将BOOT.BIN放在FAT32格式的SD卡根目录下,插入到板子上复位板子即可。

效果是终端打印出"test for GPIO MIO"字符串,并且LED每隔1秒闪烁以下

3.2 JTAG启动

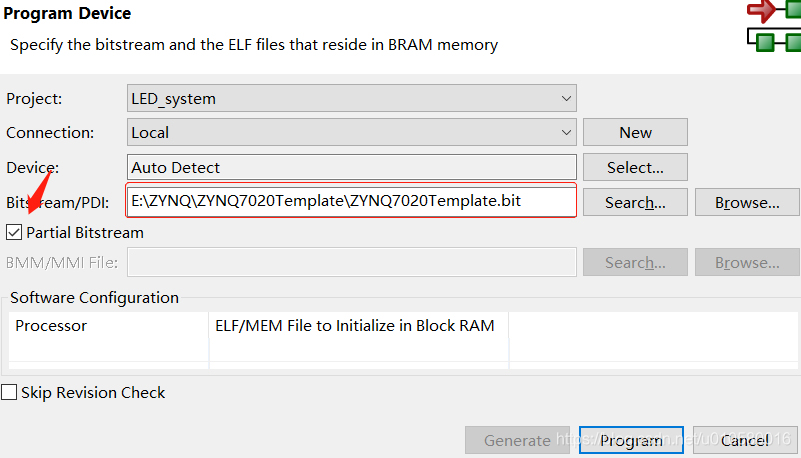

右键选择工程,点击Program Device,注意要勾选Partial Bitstream。

然后点击Run As->Luanch Hardware。