- 1夸克网盘,下载一会儿停一会儿,steam跑不满速度解决方法_夸克下载断断续续

- 2torch 封装文本数据预处理、训练、评估、预测过程_torch forecast lib下载

- 3创建Git本地仓库_创建本地git

- 4排序——堆排序和TopK_top k堆排序

- 5【无人机对抗】无人机红蓝对抗仿真【含Matlab源码 4436期】_无人机对抗建模

- 62024年安卓最全Android Root原理初探,2024Android开发面试解答

- 7Navicat Premium12 for Mac安装_navicate12 mac安装包

- 8PTA_C部分答案参考_pta平台答案题库答案公众号

- 9十、C++中的类 class与struct的区别_c++class和struct的区别

- 10kMeans 聚类_k-means聚类

以太网介绍及硬件设计_以太网芯片选型

赞

踩

1. 以太网MAC和PHY

1.1 MAC介绍

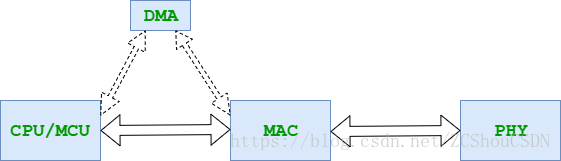

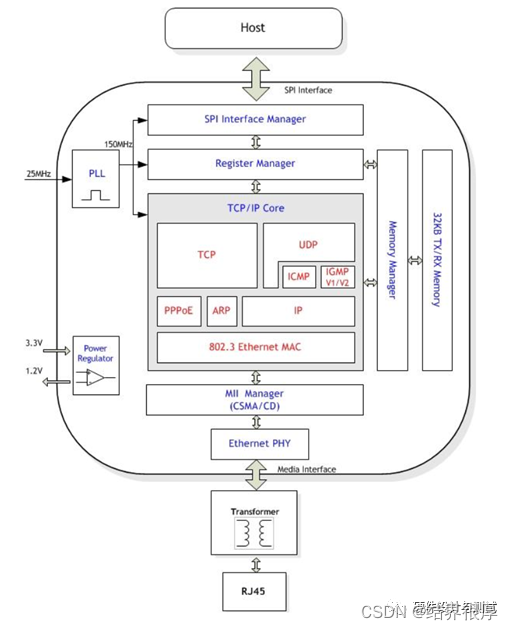

MAC(Media Access Control) 即媒体访问控制层协议。MAC由硬件控制器及MAC通信协议构成。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。MAC硬件框图如下图所示:

在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;

在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC(逻辑链路控制)层。

该层协议是以太网MAC由IEEE-802. 3以太网标准定义。一般以太网MAC芯片的一端连接PCI总线,另一端连接PHY芯片上通过MII接口连接。

1.2 PHY介绍

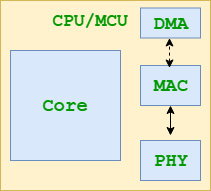

PHY(Physical Layer)是IEEE802.3中定义的一个标准模块,STA(Station Management Entity,管理实体,一般为MAC或CPU)通过MIIM(MII Manage Interface)对PHY的行为、状态进行管理和控制,而具体管理和控制动作是通过读写PHY内部的寄存器实现的。PHY的基本结构如下图:

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据)然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去,收数据时的流程反之。

PHY还有个重要的功能就是实现CSMA/CD的部分功能,它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去.如果两个碰巧同时送出了数据,那样必将造成冲突,这时候冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据

1.3 MAC与PHY关系

从硬件的角度看,以太网接口电路主要由MAC(Media Access Control)控制器和物理层接口PHY(Physical Layer,PHY)两大部分构成。如下图所示

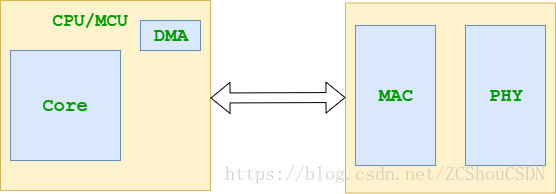

但是,在实际的设计中,以上三部分并不一定独立分开的。 由于,PHY整合了大量模拟硬件,而MAC是典型的全数字器件。考虑到芯片面积及模拟/数字混合架构的原因,通常,将MAC集成进微控制器而将PHY留在片外。更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合。可分为下列几种类型:

CPU集成MAC与PHY。目前来说并不多见

CPU集成MAC,PHY采用独立芯片。比较常见

MAC及PHY工作在OSI七层模型的数据链路层和物理层。具体如下

2. MII/RMII/GMII/RGMII基本介绍

2.1 MII

MII(Media Independent interface)即介质无关接口,它是IEEE-802.3定义的行业标准,是MAC与PHY之间的接口。MII数据接口包含16个信号和2个管理接口信号,如下图所示:

信号定义如下:

MAC 通过MII 接口读取PHY 状态寄存器以得知目前PHY 的状态。例如连接速度、双工的能力等。

也可以通过 MII设置PHY的寄存器达到控制的目的。例如流控的打开关闭、自协商模式还是强制模式等。

MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。当时钟频率为2.5MHz时,对应速率为10Mb/s。

MII接口虽然很灵活但由于信号线太多限制多接口网口的发展,后续又衍生出RMII,SMII等。

2.2 RMII

RMII(Reduced Media Independant Interface),精简MII接口,节省了一半的数据线。RMII收发使用2位数据进行传输,收发时钟均采用50MHz时钟源。信号定义如下:

其中CRS_DV是MII中RX_DV和CRS两个信号的合并,当物理层接收到载波信号后CRS_DV变得有效,将数据发送给RXD。当载波信号消失后,CRS_DV会变为无效。在100M以太网速率中,MAC层每个时钟采样一次RXD[1:0]上的数据,在10M以太网速率中,MAC层每10个时钟采样一次RXD[1:0]上的数据,此时物理层接收的每个数据会在RXD[1:0]保留10个时钟。

2.3 SMII

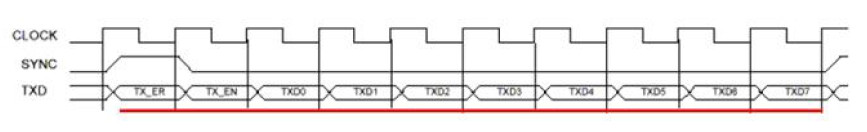

SMII(Serial Media Independant Interface),串行MII接口。它包括TXD,RXD,SYNC三个信号线,共用一个时钟信号,此时钟信号是125MHz,信号线与此时钟同步。信号定义如下:

SYNC是数据收发的同步信号,每10个时钟同步置高一次电平,表示同步。TXD和RXD上的数据和控制信息,以10bit为一组。发送部分波形如下:

从波形可以看出,SYNC变高后的10个时钟周期内,TXD依次输出一组10bit的数据即TX_ER,TX_EN,TXD[0:7],这些控制信息和MII接口含义相同。在100M速率中,每一组的内容都是变换的,在10M速率中,每一组数据需要重复10次,采样任一一组都可以

2.4 GMII

GMII(Gigabit Media Independant Interface),千兆MII接口。GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。GMII接口数据结构符合IEEE以太网标准,该接口定义见IEEE 802.3-2000。信号定义如下:

2.5 RGMII

RGMII(Reduced Gigabit Media Independant Interface),精简GMII接口。相对于GMII相比,RGMII具有如下特征:

发送/接收数据线由8条改为4条

TX_ER和TX_EN复用,通过TX_CTL传送

RX_ER与RX_DV复用,通过RX_CTL传送

1 Gbit/s速率下,时钟频率为125MHz

100 Mbit/s速率下,时钟频率为25MHz

10 Mbit/s速率下,时钟频率为2.5MHz

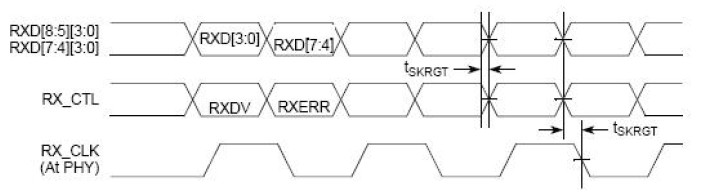

虽然RGMII信号线减半,但TXC/RXC时钟仍为125Mhz,为了达到1000Mbit的传输速率,TXD/RXD信号线在时钟上升沿发送接收GMII接口中的TXD[3:0]/RXD[3:0],在时钟下降沿发送接收TXD[7:4]/RXD[7:4],并且信号TX_CTL反应了TX_EN和TX_ER状态,即在TXC上升沿发送TX_EN,下降沿发送TX_ER,同样的道理试用于RX_CTL,下图为发送接收的时序:

3. 以太网接口类型

3.1 以太网物理层标准

3.2 光口

光口是光纤接口的简称

目前以太网光模块封装有 GBIC 、 SFF 、 SFP ,公司目前推荐使用的是 GBIC

和 SFP 两种可热插拔的光模块,有 850nm 、 1310nm 、 1550nm 波长。

光纤有单模、多模之分,区别在于:

1) 单模光纤芯径小(10m m左右),仅允许一个模式传输,色散小,工作在长波长(1310nm和1550nm),与光器件的耦合相对困难。

2)多模光纤芯径大(62.5m m或50m m),允许上百个模式传输,色散大,工作在850nm或1310nm。与光器件的耦合相对容易。

光模块

GBIC(Gigabit Interface Converter的缩写),是将千兆位电信号转换为光信号的接口器件。GBIC设计上可以为热插拔使用。GBIC是一种符合国际标准的可互换产品。采用GBIC接口设计的千兆位交换机由于互换灵活,在市场上占有较大的市场份额。

SFP (Small Form-factor Pluggable)可以简单的理解为GBIC的升级版本。

3.3 电口

电口是相对光口来讲的,主要指铜缆,是处理的电信号。目前使用普遍的网络接口有百兆电口和千兆电口等。

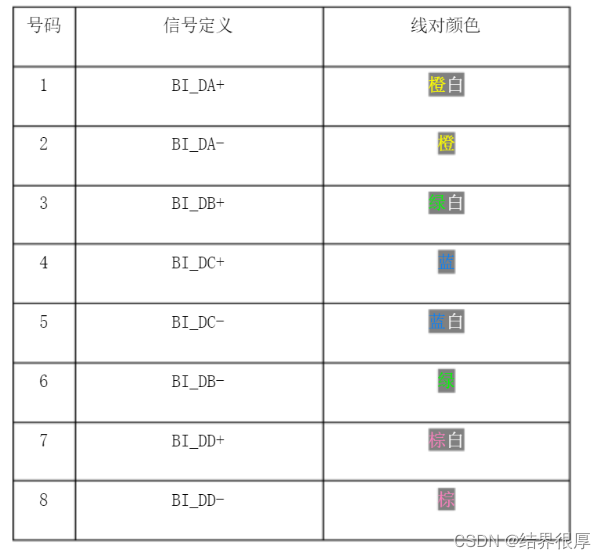

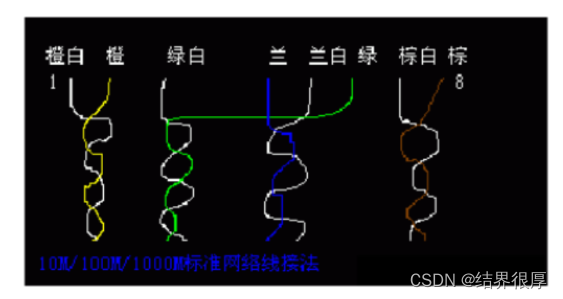

RJ45接口通常用于数据传输,最常见的应用为网卡接口。RJ45头根据线的排序不同的法有两种,一种是橙白、橙、绿白、蓝、蓝白、绿、棕白、棕;另一种是绿白、绿、橙白、蓝、蓝白、橙、棕白、棕;因此使用RJ45接头的线也有两种即:直通线、交叉线。

RJ45型网卡接口:

10 100base tx RJ45接口是常用的以太网接口,支持10兆和100兆自适应的网络连接速度,常见的RJ45接口有两类:用于以太网网卡、路由器以太网接口等的DTE类型,还有用于交换机等的DCE类型。 DTE我们可以称做"数据终端设备”,DCE我们可以称做“数据通信设备”。从某种意义来说,DTE设备称为“主动通信设备”,DCE设备称为“被动通信设备”。当两个类型一样的设备使用RJ45接口连接通信时,必须使用交叉线连接。

RJ45 型网线插头又称水晶头,共有八芯做成,广泛应用于局域网和 ADSL 宽带上网用户的网络设备间网线(称作五类线或双绞线)的连接。

RJ-45 插座可以分为屏蔽式和非屏蔽式、 直插式和侧插式、 带 LED 灯和不带 LED 灯, 有单端口、两端口、 单排四端口、 单排 6 端口、 单排 8 端口、 双排 8 端口、 双排 12 端口、双排 16 端口等,有 8PIN、 6PIN 和 4PIN 。图 3 所示是常用的屏蔽式、侧插、

带 LED 指示灯、单排四端口的 RJ-45 插座。其中 LED 指示灯是绿色和黄色,可以分别表示 LINK (链路完整)和 ACT (有收发活动)等。

3.4 100M 接口

RJ接头引脚与信号对应关系

线材要求CAT-5(5类线)

3.5 1000M 接口定义

千兆PHY通过网络变压器连接到RJ45接口,一共有4对差分线MDI[0…3]+/-。一般的接法是:

RJ45[1…8]连接器的线序与水晶头的压接顺序一致。

线材要求CAT-5e(5类增强线,俗称超五类),接头接法与10M/100M 完全兼容。

4. 以太网接口电路PCB设计

从硬件的角度看,以太网接口电路主要由MAC(Media Access Controlleroler)控制和物理层接口(Physical Layer,PHY)两大部分构成。大部分处理器内部包含了以太网MAC控制,但并不提供物理层接口,故需外接一片物理芯片以提供以太网的接入通道。

下图是以太网的典型应用。我们的PCB设计基本是按照这个框图来布局布线,下面我们就以这个框图详解以太网有关的布局布线要点。

4.1 布局布线注意事项

下图是网口变压器没有集成在网口连接器里的参考电路PCB布局、布线图。

a) RJ45和变压器之间的距离尽可能的短,晶振远离接口、PCB边缘和其他的高频设备、走线或磁性元件周围,PHY层芯片和变压器之间的距离尽可能短,但有时为了顾全整体布局,这一点可能比较难满足,但他们之间的距离最大约10~12cm,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;

b) PHY层芯片的电源滤波按照芯片要求设计,通常每个电源端都需放置一个退耦电容,他们可以为信号提供一个低阻抗通路,减小电源和地平面间的谐振,为了让电容起到去耦和旁路的作用,故要保证退耦和旁路电容由电容、走线、过孔、焊盘组成的环路面积尽量小,保证引线电感尽量小;

c) 网口变压器PHY层芯片侧中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小;

d) 网口变压器接口侧的共模电阻和高压电容靠近中心抽头放置,走线短而粗(≥15mil);

e) 变压器的两边需要割地:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。这样做分割处理,就是为了达到初、次级的隔离,控制源端的干扰通过参考平面耦合到次级;

f) 指示灯的电源线和驱动信号线相邻走线,尽量减小环路面积。指示灯和差分线要进行必要的隔离,两者要保证足够的距离,如有空间可用GND隔开;

g) 用于连接GND和PGND的电阻及电容需放置地分割区域。

- 以太网的信号线是以差分对(Rx±、Tx±)的形式存在,差分线具有很强共模抑制能力,抗干扰能力强,但是如果布线不当,将会带来严重的信号完整性问题。下面我们来一一介绍差分线的处理要点:

a) 优先绘制Rx±、Tx±差分对,尽量保持差分对平行、等长、短距,避免过孔、交叉。由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里;

b) 当速度要求高时需对Rx±、Tx±差分对进行阻抗控制,通常阻抗控制在100Ω±10%;

c) 差分信号终端电阻(49.9Ω,有的PHY层芯片可能没有)必须靠近PHY层芯片的Rx±、Tx±管脚放置,这样能更好的消除通信电缆中的信号反射;

d) 差分线对上的滤波电容必须对称放置,否则差模可能转成共模,带来共模噪声,且其走线时不能有stub ,这样才能对高频噪声有良好的抑制能力。

变压器集成在连接器的以太网电路的PCB布局、布线较不集成的相对简单很多,下图 3是采用一体化连接器的网口电路的PCB布局、布线参考图:

从上图可以看出,图 3和图 1的不同之处在于少了网口变压器,其它大体相同。不同之处主要体现在网口变压器已集成至连接器里,所以地平面无需进行分割处理,但我们依然需要将一体化连机器的外壳连接到连续的地平面上。(或者划分接口地,外壳连接到接口地)

以下内容转自---------专治pcb疑难杂症

4.2 网口布局

依照上面大致的布局图我们可以得出以下注意事项(整个布局思路从RJ45连接器到MAC,按顺序说明,大家布局时可参考):

-

1,首先看RJ45,一般都是定位器件, 靠近板边放置。这个是常规布局,根据结构要求来放置即可。

-

2,RJ45和变压器之间的距离尽可能的短,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;建议长度小于1000mil。

-

3,网口变压器的放置方向位置初次级需要完全隔离开来。

-

4,变压器初级端由电容电阻组成的电路是专用的bob smith电路,需要靠近放置。

bob smith电路作用:

通过一个网络变压器+Bob Smith匹配,其作用网络变压器主要有信号传输、阻抗匹配、网络变压器主要有信号传输、阻抗匹配、波形修复、信号杂波抑制和高电压隔离等作用。而Bob Smith 电路的作用是为了改善端口EMC的差模,共模阻抗匹配的端接处理方式。这种电路能有效的滤除共模干扰,该电路可以降低10dB左右的EMI衰减。

-

5,变压器次级端中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小;

-

6,PHY芯片模块的方向最好正对着变压器,尽可能靠近的放置,以保持接口芯片固有的A/D隔离,另外路径的最短话可以做到平衡走线,减少干扰信号向板内耦合。

-

7,Phy芯片中的晶振远离接口、PCB边缘和其他的高频设备、走线或磁性元件周围。

4.3 网口布线

接着我们来看看布线上的问题:

- 1,关于网口变压器两端的GND处理,常规是净空,即网口部分所有层挖空,变压器下方挖空。

业界还有一种情况:

变压器的两边做割地处理:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。

反正核心原理就是:做好隔离,避免耦合!毕竟外来的还是不干净的。

- 2,另外一个最优先处理的信号:差分信号。

其一,以太网的信号线是以差分对(Rx±、Tx±)的形式存在,差分线具有很强共模抑制能力,抗干扰能力强;尽量保持差分对平行、等长、短距,避免过孔、交叉。

其二,初级的网口差分信号可适当加粗抗干扰,无需控制阻抗。但次级端需要需对Rx±、Tx±差分对进行阻抗控制,通常阻抗控制在100Ω±10%。

其三,做对内等长,由于管脚分布、过孔、以及走线空间等因素存在使得差分线长度不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里;

其四, 附近不要有其他高速信号线,做好间距要求,提高抗干扰能力。

-

3,PHY芯片到MAC芯片的信号做组间等长处理,参考时钟,控制范围可在±50mil。 具体哪些信号需要控等长,请参考之前疑难杂症。点击进入:这组Bus到底要不要绕等长?

-

4,其他如电容放置fanout,晶振电路设计,灯信号处理等等,按常规要求处理好。

4.4 其他一些相关问题答疑:

1、中间抽头为什么有些接电源?有些接地?

这个主要是与使用的PHY芯片UTP口驱动类型决定的,这种驱动类型有两种,电压驱动和电流驱动。电流驱动的就要接电源;电压驱动的就直接接个电容到地即可!所以对于不同的芯片,中心抽头的接法,与PHY是有密切关系的,具体还要参看芯片的datasheet和参考设计了。为什么接电源时,又接不同的电压呢?这个也是所使用的PHY芯片资料里规定的UTP端口电平决定的。决定的什么电平,就得接相应的电压了。即如果是2.5v的就上拉到2.5v,如果是3.3v的就上拉到3.3v。

如果网络变压器的中心抽头需要提供一个VCC(3.3V、2.5V等等,下同)电源的就是电流驱动,

如果是直接加一个对地电容就可以的就是电压驱动。

2,空间不足,变压器是否可以不接?接了为什么要掏空?

从理论上来说,是可以不需要接变压器,直接接到RJ45上,也许能正常工作的。但是传输距离就很受限制,而且当接到不同电平网口时,也会有影响。而且外部对芯片的干扰也很大。当接了网络变压器后,它主要用于信号电平耦合。其一,可以增强信号,使其传输距离更远;其二,使芯片端与外部隔离,抗干扰能力大大增强,而且对芯片增加了很大的保护作用(如雷击);其三,当接到不同电平(如有的PHY芯片是2.5V,有的PHY芯片是3.3V)的网口时,不会对彼此设备造成影响。至于掏空的原因是为了防止变压器转换的时候影响下面的电源和地。

5. 以太网接口实现方式

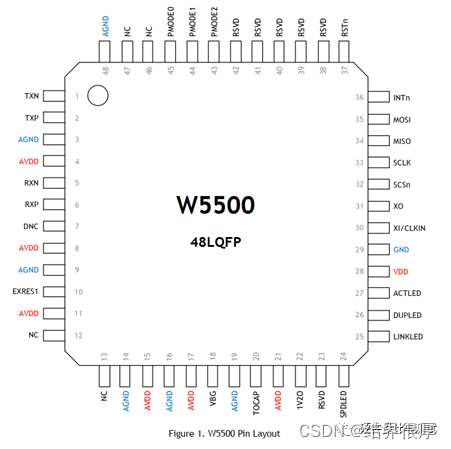

5.1 SPI转网口

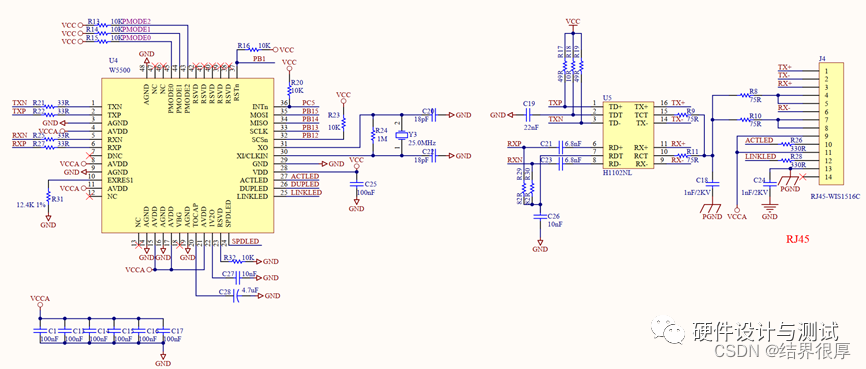

CPU(具有SPI接口)+MAC和PHY一体芯片(集成TCP/IP协议)+ RJ45(集成网络变压器)

两者通过SPI接口进行通信

5.2 UART 转网口

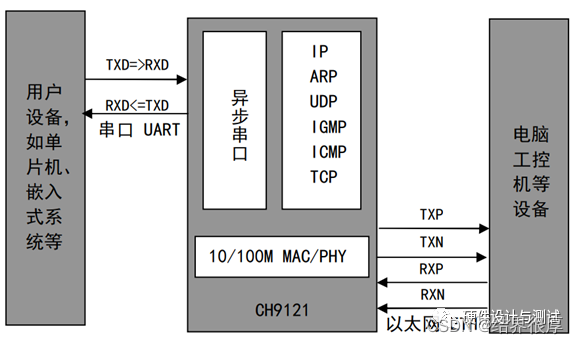

CPU(具有UART接口)+MAC和PHY一体芯片(集成TCP/IP协议)+ RJ45(集成网络变压器),两者通过UART接口进行通信

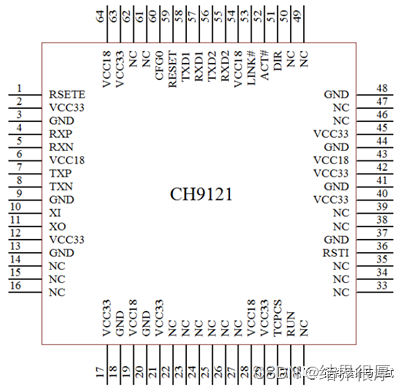

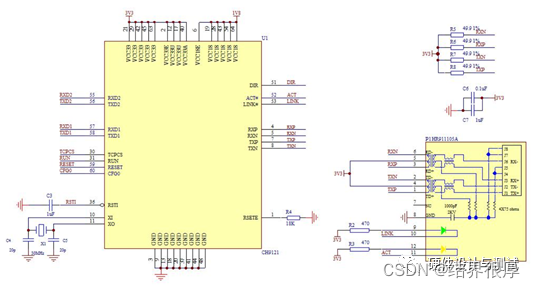

CH9121

CH9121 为网络串口透传芯片,可实现串口数据与网络数据的双向透明传输,支持 TCP CLEINT/SERVER,UDP CLIENT/SERVER 4 种工作模式,串口波特率支持范围为 300bps~921600bps,使用前需通过上位机软件 NetModuleConfig.exe 或者串口命令配置芯片的网络参数和串口参数,配置完成后,CH9121 将配置参数保存至内部存储空间,芯片复位后,CH9121 将按保存的配置值工作。

5.3 MAC网口

网络设计中最常见的是CPU(集成MAC层)+PHY+网络变压器+RJ45结构

以太网PHY芯片与CPU有2种常见连接方式,一种是RGMII,另外一种是SGMII。

SGMII接口对应的数据线比较少,包括差分信号线TXD、RXD和RXCLK,使用了SerDes技术的GMII接口,需要PCS实现8b/10b编码,串行化之后高速串行总线传输。

RGMII接口对应的数据线比较多,包括4个接收数据线、4个发送数据线、接收数据时钟、发送数据时钟等。

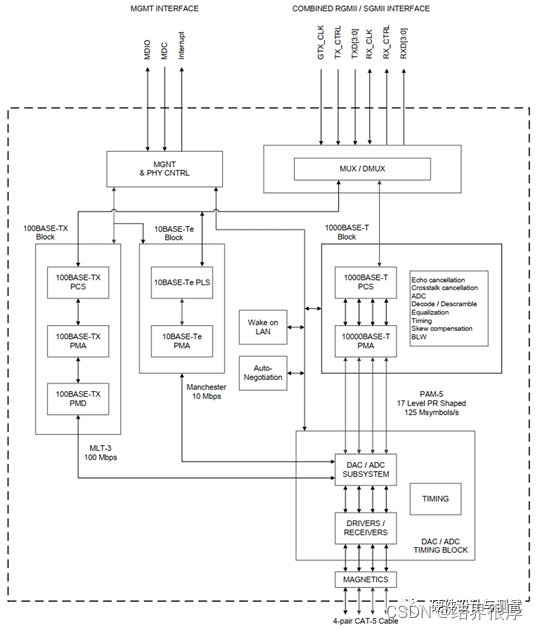

列举三种千兆以太网PHY架构

88E1111

88E1512

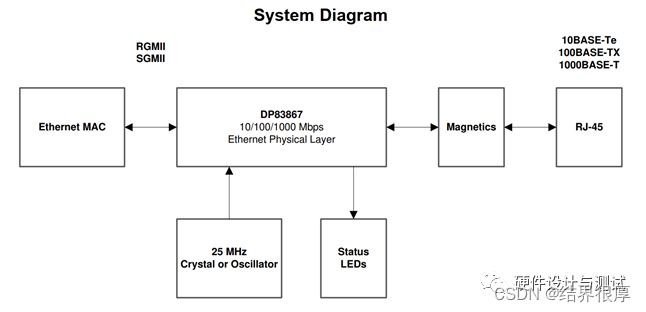

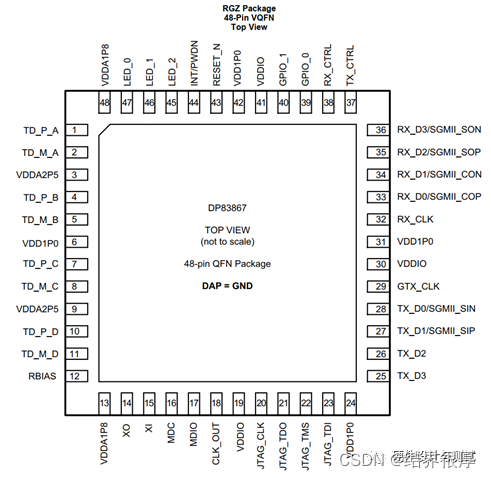

DP83867

5.4 常用以太网PHY芯片选型

6. 1000M以太网接口参考设计(裕太微YT8521S)

T8521S 是一款高度集成的以太网收发器,符合 10BASE Te、100BASE-TX 和 1000BASE-T IEEE 802.3 标准。它提供了传输和接收所需的物理层功能以太网上的数据包经由 CAT5E UTP 电缆。

YT8521S 采用先进的 DSP 技术和模拟前端(AFE)实现高速数据传输通过 UTP 电缆进行传输和接收。交叉检测和自动校正、极性等功能校正、自适应均衡、串扰消除、回声消除、定时恢复和纠错在 YT8521S 中实现,以 10Mbps、100Mbps或 1000Mbps。MAC和 PHY 之间的数据传输通过精简的千兆媒体独立接口(RGMII)或串行的千兆媒体独立接口(SGMII)接口进行用于 1000BASE-T、100BASE-TX 和 10BASE-Te。

YT8521S 支持各种 RGMII 信号电压,包括 3.3V、2.5V和 1.8V。YT8521S 还支持可配置为 SGMII、1000BASE-X 或100BASE-FX 的 SerDes 接口。YT8521S 具有名为 LRE100-4 的专有功能,该功能使设备能够在长达 400 米的扩展电缆延伸应用中,与符合 LRE100-4 的链路伙伴进行自动协商和连接。

商业级型号:YT8521SC

工业级型号:YT8521SH

科普:MDI是正常的 UTP 或 STP 连接,而 MDIX 连接器的发送和接收对是在内部反接的,这就使得不同的设备可以利用常规的UTP(Unshielded Twisted Paired非屏蔽双绞线)或STP(shielded Twisted Paired)电缆实现背靠背的级联。端口自动翻转(Auto MDI/MDIX)能让网络设备自动识别交叉线或者直连线,并能进行线序跳转,达到无视物理线序,能在不同设备间传输信号。

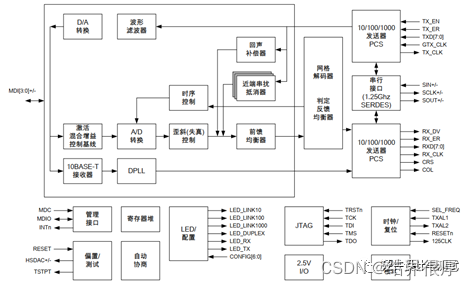

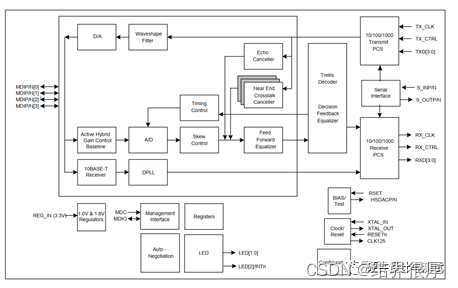

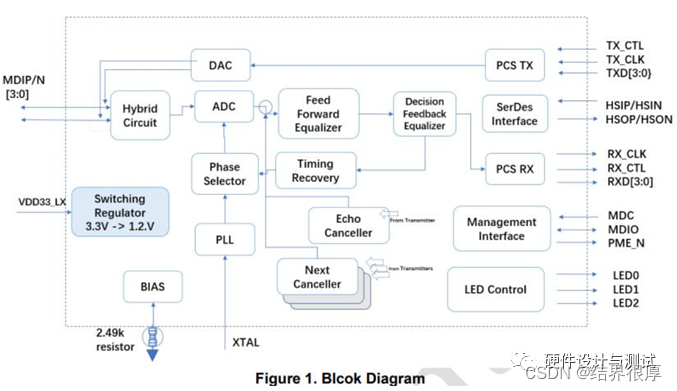

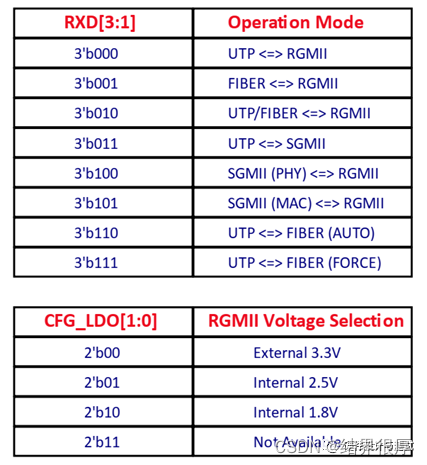

芯片框图

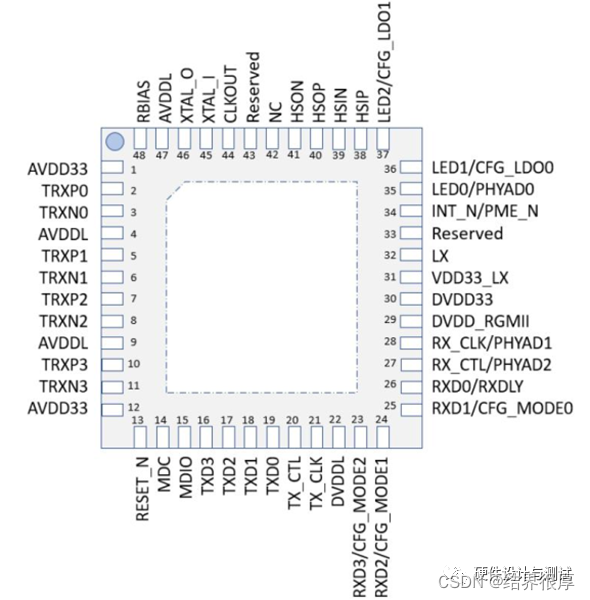

引脚定义

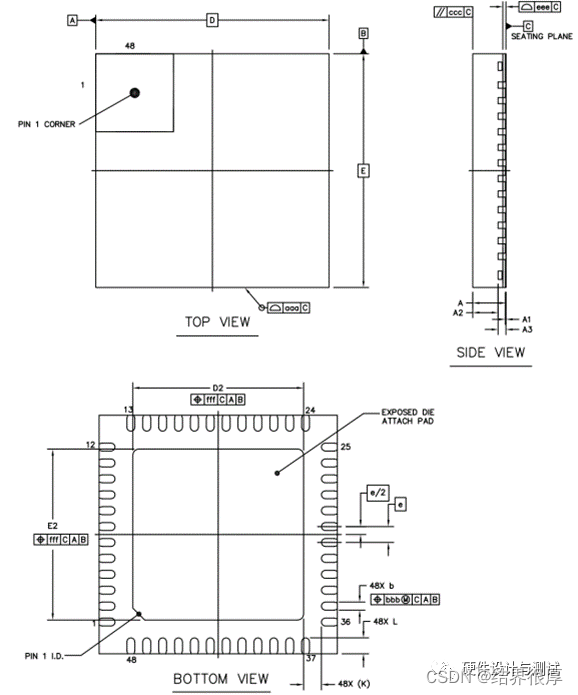

机械尺寸

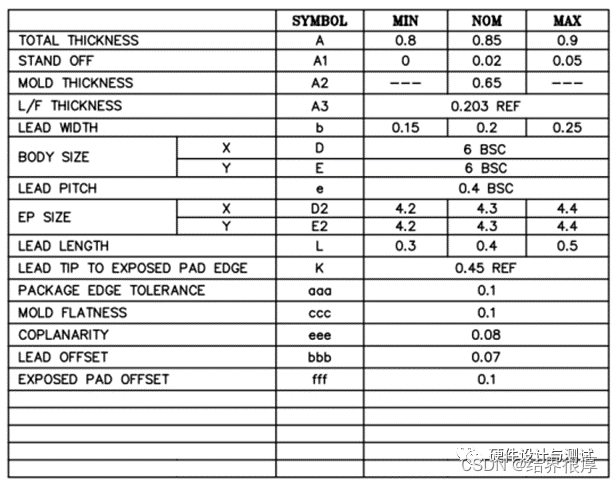

参数配置

功能描述

UTP<=>RGMII \ UTP<=>SGMII

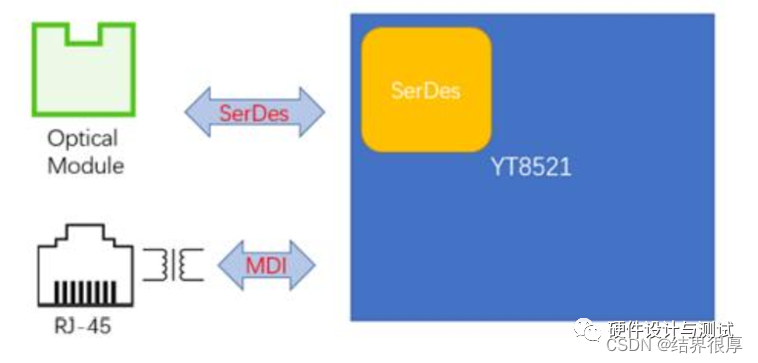

FIBER<=>RGMII

UTP\FIBER<=>RGMII

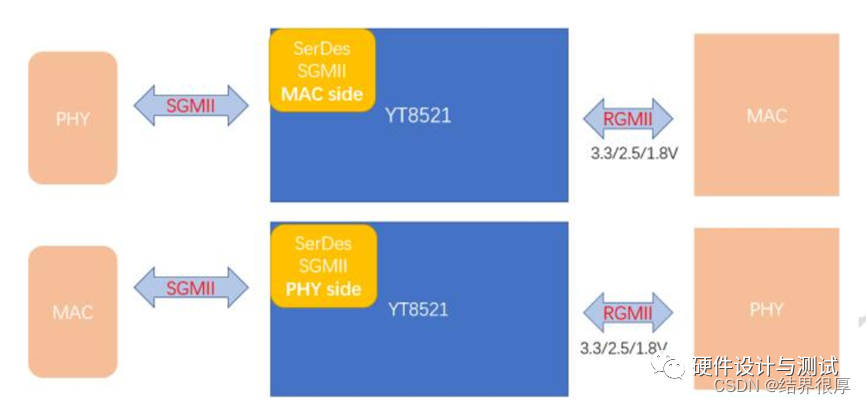

SGMII(PHY/MAC)<=>RGMII

UTP <=>FIBER

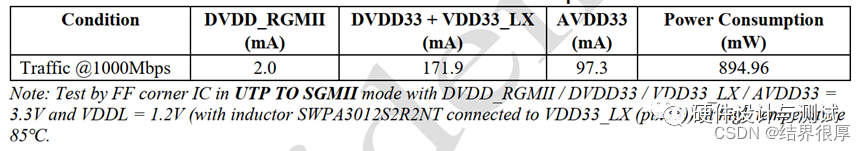

最大功耗

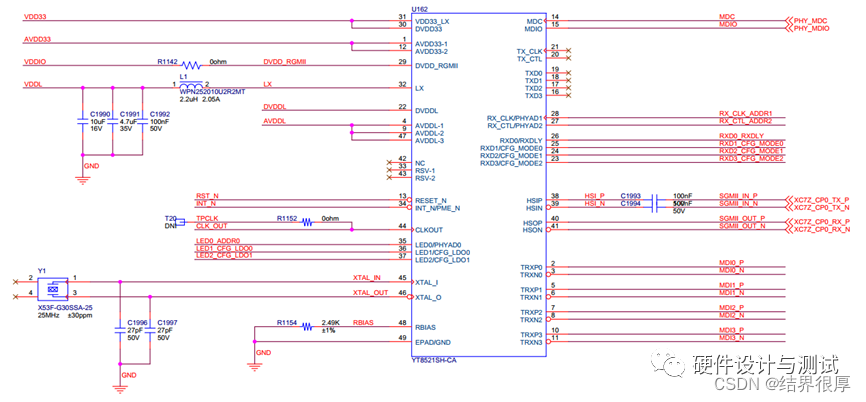

原理图参考设计

调试经验

预留MDIO接口,自协商情况下无法ping通,可采用强制模式。

裕太微YT8521SH硬件设计简单,功能齐全,技术支持专业迅速,国产优选PHY芯片,上述功能均已验证,放心使用。

部分内容转自:

https://blog.csdn.net/sternlycore/article/details/89065789

https://blog.csdn.net/ZCShouCSDN/article/details/80090802

https://blog.csdn.net/wqfhenanxc/article/details/82221495

https://blog.csdn.net/qq_42053636/article/details/88774865

https://mp.weixin.qq.com/s/6B4YON3TqltBQC27PRyprQ

https://mp.weixin.qq.com/s/seB30wijl9MxH5iIX_7Q-w