热门标签

热门文章

- 1用Python的tkinter库做一个简单的打包作业的工具_tkinter打包成apk

- 2AI服务器的互连芯片技术创新和突破研究

- 3leetcode-227. 基本计算器 II_基本计算器 leetcode

- 4# Redis 入门到精通(四)-- linux 环境安装 redis

- 5网易笔试题_如果一根针从一个随机且相当高的高度掉到我们的游戏板上,这是一个画有平行线的表

- 6计算机毕业设计springboot的工程机械设备租赁系统wbv109【附源码+数据库+部署+LW】

- 7ofbiz安装

- 8树状数组(Binary Indexed Tree),看这一篇就够了

- 9LKA相关知识_lka 对eps的要求

- 10五种常用的异常值检测方法(均方差、箱形图、DBScan 聚类、孤立森林、Robust Random Cut Forest_使用均值和方差的异常检测算法

当前位置: article > 正文

【芯片设计- RTL 数字逻辑设计入门 16 -- verilog CRC-8 实现】_crc-8校验verilog实现

作者:喵喵爱编程 | 2024-07-11 21:16:10

赞

踩

crc-8校验verilog实现

CRC 校验

CRC校验(Cyclic Redundancy Check)是一种用于检测数据传输或存储后是否出现错误的技术。其核心思想是通过发送方和接收方都遵循同一算法生成一个数据块的校验码,然后接收方将其与接收到的数据的校验码进行比较。如果两者一致,那么数据很可能是完整和未受损的;如果不同,那么数据在传输或存储过程中可能发生了错误。

简单通俗的介绍:

假设你有一本书,你想检查这本书是否完整,没有丢失任何页面。CRC校验就像是你在书的每一页上都做一个特殊的标记,然后计算所有这些标记的总和。你告诉接收者(比如你的朋友)也按照同样的方法来做。你的朋友收到书后,也按照相同的方法做标记并计算总和。然后,他将他的总和与你的总和进行比较。如果两者相同,那么书很可能是完整的;如果不同,那么书可能在传输过程中丢失了一些页面。

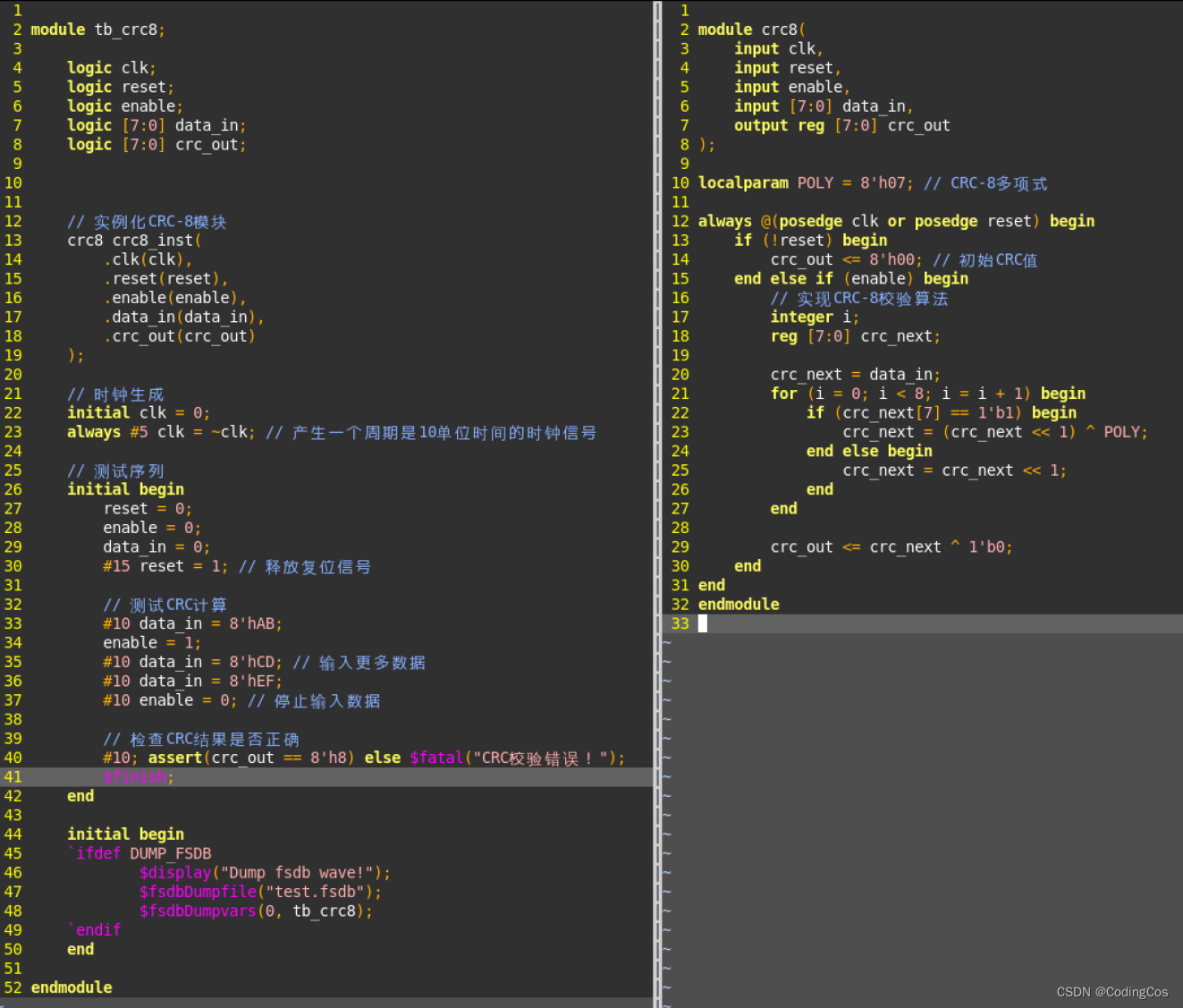

verilog and testbench

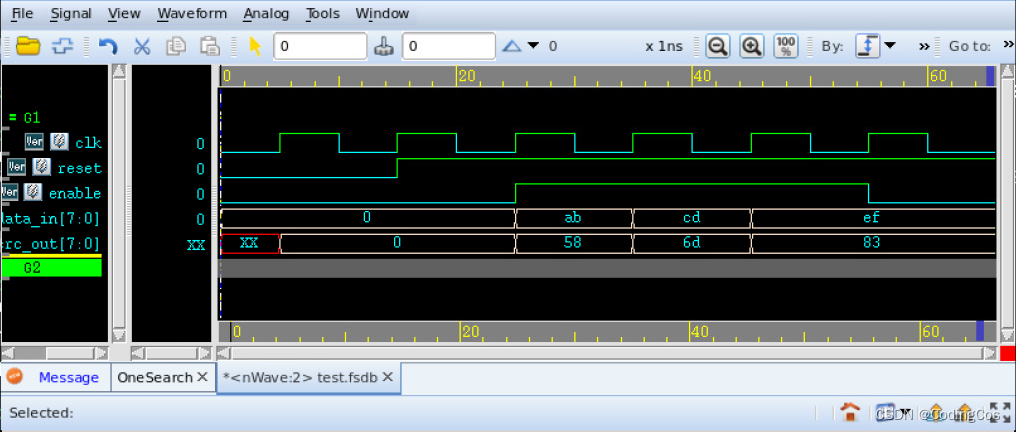

VCS 仿真波形

仿真结果可以使用网页版本 CRC工具:http://www.ip33.com/crc.html

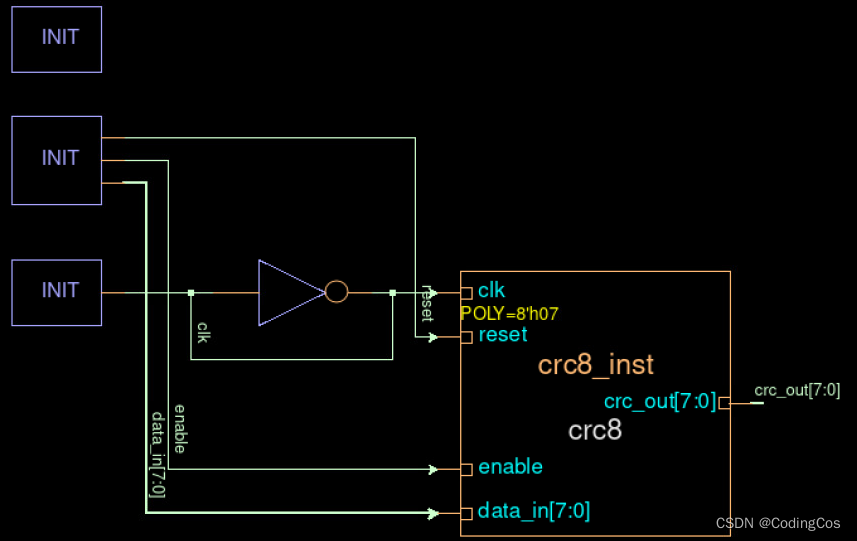

综合图

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/喵喵爱编程/article/detail/811624

推荐阅读

相关标签