热门标签

热门文章

- 1git——github篇_github draft a new release

- 2node爬虫、前端爬虫_node crawler 获取网页后传给前端

- 3java实现单链表上的插入、删除、查找、修改、计数、输出等基本操作_单链表重复字符的统计

- 4进入AI领域做产品 —— 我的自学之路(CV-人脸识别)_粗略人脸识别需要多少算力

- 5IDEA中Git的提交、更新、还原_idea git更新代码到本地

- 6javaagent学习_java agent学习

- 7基于LLM+TTS+Lip-Sync的流式数字人的问答系统框架_llm tts

- 8修改元素内容改值,表单改值, 获取/失去焦点,鼠标移动离开不会冒泡的方式,通过样式让滚动条丝滑滚动_失去焦点修改标签属性

- 9DNS域名解析服务— — —DNS分离解析_windowsdns分离解析

- 10BASE64Encoder_base64encoder.encode(

当前位置: article > 正文

时钟、时钟域_分频的时钟算不算一个时钟域

作者:在线问答5 | 2024-07-17 09:08:52

赞

踩

分频的时钟算不算一个时钟域

1.1 时钟

- 时钟信号是一个按一定电压幅度,一定时间间隔连续发出的脉冲信号。

- 脉冲信号之间的时间间隔称为周期:

- 在单位时间内所产生的脉冲个数称为频率,频率的标准计量单位是Hz(赫兹)

- 每一次时钟脉冲到来,芯片内的晶体管就改变一次状态,让整个芯片完成一定任务。

- 时钟相当于芯片的脉搏、心脏跳动

- 在SDC文件中用Synopsys TCL创建时钟

create_clock -period 2 [get_ports Clk]

- 1

1.1.1 时钟偏斜(clock skew)

时钟偏斜指的是同一个时钟信号到达两个不同寄存器clk pin之间的时间差值,skew的定义就是时钟最长路径减去最短路径的值。

1.1.2 时钟抖动(jitter)

时钟抖动就是两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关。

1.2 时钟源

- 数字电路里一般用晶振提供基本的时钟信号。晶振是晶体振荡器(Oscillator,OSC)的简称。

- 有些芯片的一部分时钟来自于其他芯片。它的时钟源就是外部芯片的输出信号。比如芯片2C、SP接口时钟就来自外部芯片。

1.3 同步时钟

- 同源,比如分频

- 有固定的相位关系

1.4 异步时钟

- 不同源

- 没有固定的相位关系

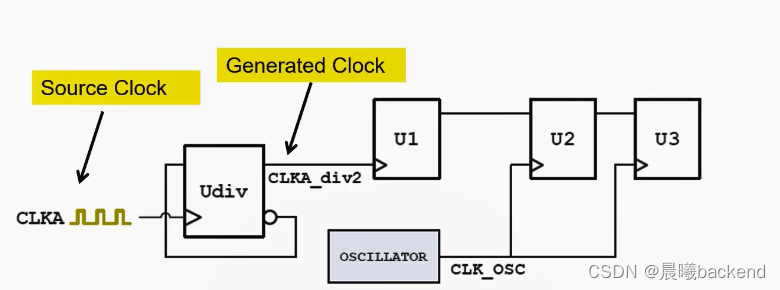

CLKA和CLKA_div2是同步时钟CLKA/CLKA_div2和OSC是异步时钟

- 不同频率但是来自于同一个时钟源,就还是同步时钟(分频、倍频)

- 同一频率但是无固定相位差就还是异步时钟

- 单从同一频率这一点是无法确定同步时钟还是异步时钟

1.5 时钟域(Clock Domain)

1.5.1 单时钟(Single clock domain)

- 数据发送和接收是同一个时钟

1.5.2 多时钟(Multiple clocks domain)

- 数据发送和接收不是同一个时钟

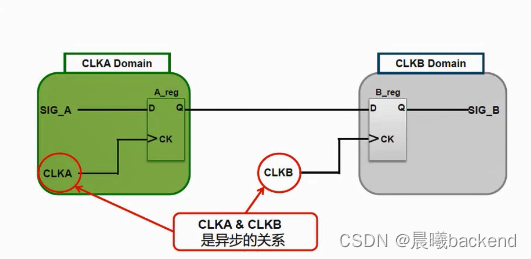

1.6 跨时钟域

- 若一个电路

launch clock和capture clock不是同一个时钟,就是跨时钟域(同源的同步跨时钟和不同源的异步跨时钟)电路- 若这两个时钟是同步时钟就是同步跨时钟域(源时钟到分频时钟)

- 若这两个时钟是异步时钟就是异步跨时钟域

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/在线问答5/article/detail/839195?site

推荐阅读

相关标签