热门标签

热门文章

- 1matlab计算e有效值近似列表,MATLAB_实验5

- 2SQL Server远程连接_sql server 远程连接

- 3大数据-66 Kafka 高级特性 分区 副本因子修改 replicas动态修改_kafka 修改 副本数

- 4一篇文章搞懂人工智能、机器学习、深度学习_ai与机器学习

- 5python爬虫之PySpider框架详解

- 6语义分割和实例分割的区别是什么

- 7MySQL数据库如何解决大数据量存储问题

- 8已解决centos7 yum报错:cannot find a valid baseurl for repo:base/7/x86_64的解决方案_cannot find a valid baseurl for repo: base

- 9chrome 源码分析_google 浏览器源码分析

- 10将Pyinstaller打包后的exe还原成PYC 反编译到.py的Python源码_pyinstxtractor转换后源码

当前位置: article > 正文

干货 | 在FPGA上实现UART串口通信_fpga uart串口通信

作者:天景科技苑 | 2024-08-09 07:24:31

赞

踩

fpga uart串口通信

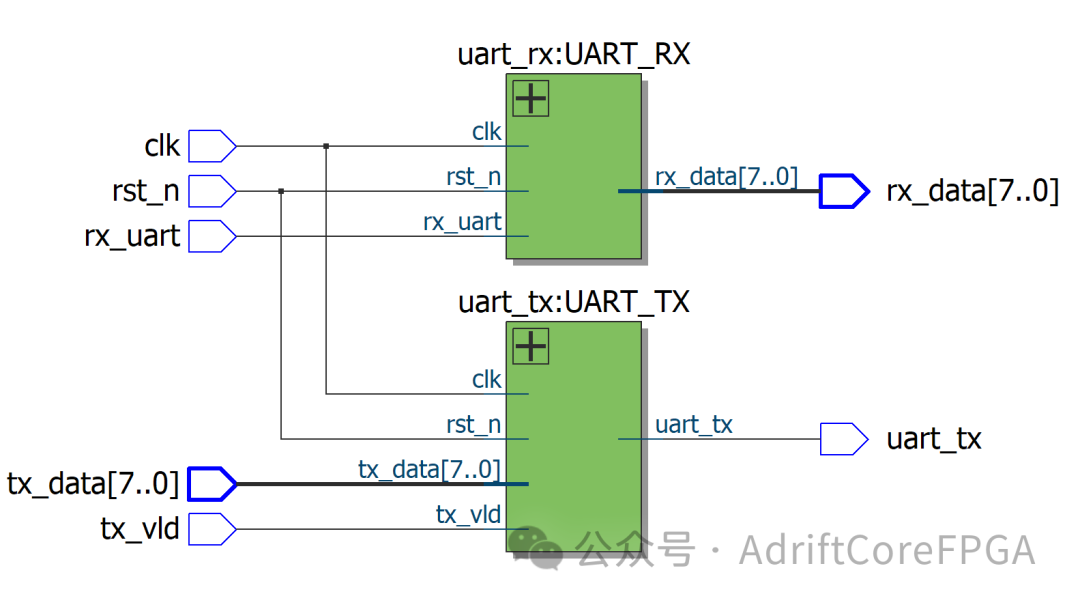

一、RTL Viewer

UART(Universal Asynchronous Receiver/Transmitter)是一种通信协议,用于在电子设备之间传输数据。它是一种串行通信协议,意味着数据位按顺序一个接一个地传输。

在串行通信中,每个数据位按照顺序传输,而在并行通信中,多个数据位可以同时传输。串行通信更适合长距离传输和连接设备之间的通信。

UART是异步通信协议,这意味着数据传输不依赖于定时时钟。相反,发送和接收设备之间的通信通过起始位、数据位、奇偶校验位和停止位的组合来同步。这种异步性使得UART协议在不同速率和不同设备之间的通信更为灵活。

UART通信通常涉及两个设备,一个充当发送器,一个充当接收器。它们通过两根线(TX线和RX线)连接。TX线用于发送数据,RX线用于接收数据。

UART广泛用于嵌入式系统、传感器、模块之间的通信,以及计算机系统中串行端口的实现。它是一种简单而可靠的通信方式,适用于各种不同的应用场景。

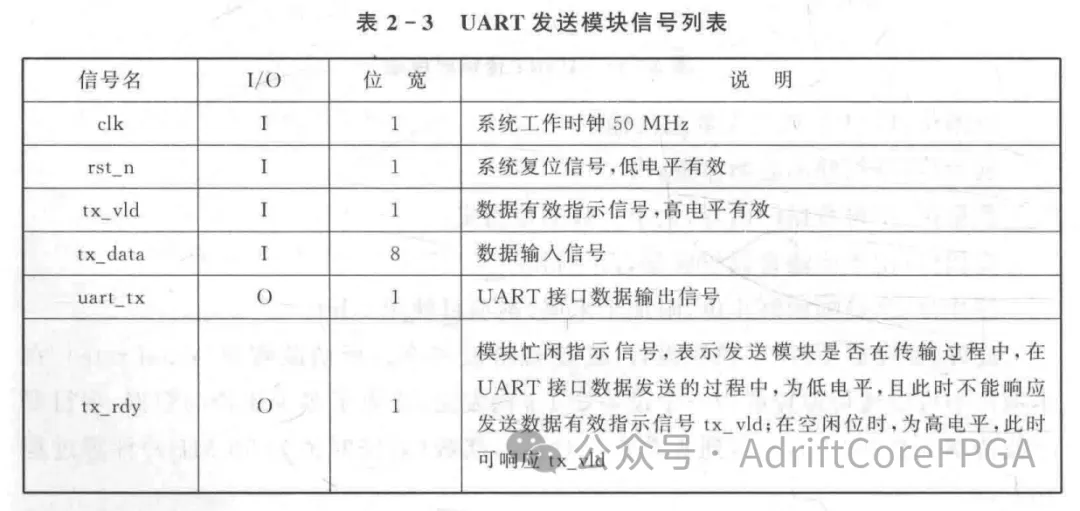

二、引脚描述

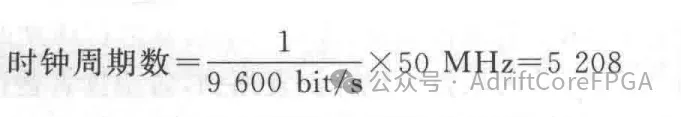

三.波特率计算

系统时钟50MHz

(1bit/波特率bit/s)秒 / (1/50MHz)秒

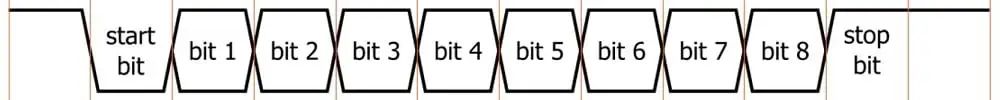

四.UART时序

UART数据帧包括起始位(Start Bit)、数据位、奇偶校验位(Parity Bit,可选)、停止位(Stop Bit)。起始位指示数据帧的开始,停止位表示数据帧的结束。数据位的数量决定了可以传输的数据范围,而奇偶校验位用于检测传输错误。

五.verilog代码

module uart_rx( clk , rst_n , rx_uart , rx_data);

parameter DATA_R = 8;parameter DATA_0 = 13;parameter DATA_1 = 4;

input clk;input rst_n;input rx_uart;output [DATA_R-1:0] rx_data;

reg [DATA_R-1:0] rx_data;

reg [DATA_0-1:0] cnt0;wire add_cnt0;wire end_cnt0;

reg [DATA_1-1:0] cnt1 ;wire add_cnt1;wire end_cnt1;

wire nedge;reg flag_add;

//9600比特率计数always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt0 <= 0; end else if(add_cnt0)begin if(end_cnt0) cnt0 <= 0; else cnt0 = cnt0 + 1'b1; endendassign add_cnt0 = flag_add;assign end_cnt0 = add_cnt0 && cnt0 == 5208 - 1;

//9比特串口数据计数always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt1 <= 0; end else if(add_cnt1)begin if(end_cnt1) cnt1 <= 0; else cnt1 <= cnt1 + 1'b1; endendassign add_cnt1 = end_cnt0;assign end_cnt1 = add_cnt1 && cnt1 == 9 - 1;

//边沿检测,接D触发器//异步信号同步化,防止亚稳态,打两拍reg[2:0] uart_sync;always @(posedge clk or negedge rst_n)begin if(!rst_n)begin uart_sync <= 3'b111; end else uart_sync <= {uart_sync[1:0],rx_uart};endassign nedge = uart_sync[2:1] == 2'b10;

//当接收到的串口由1变0时,flag_add置位//当计数结束时,flag_add复位always @(posedge clk or negedge rst_n)begin if(!rst_n)begin flag_add <= 0; end else if(nedge)begin flag_add <= 1; end else if(end_cnt1)begin flag_add <= 0; endend

//cnt1 == 0时,接收的是起始位0,1-8才是数据位always @(posedge clk or negedge rst_n)begin if(!rst_n)begin rx_data <= 8'h00; end else if (add_cnt0 && cnt0 == 5208/2 - 1 && cnt1 > 0) begin rx_data[cnt1 - 1] <= rx_uart; endend

endmodulemodule uart_tx( clk , rst_n , tx_vld , tx_data , uart_tx);

parameter DATA_T = 8;parameter DATA_0 = 13;parameter DATA_1 = 4;

input clk;input rst_n;input tx_vld;input [DATA_T-1:0] tx_data;output uart_tx;

reg uart_tx;

reg [DATA_0-1:0] cnt0;wire add_cnt0;wire end_cnt0;

reg [DATA_1-1:0] cnt1;wire add_cnt1;wire end_cnt1;

reg add_flag;

reg [9:0] tx_data_temp;wire load_data;

wire en_send;

//9600波特率计数器always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt0 <= 0; end else if(add_cnt0)begin if(end_cnt0) cnt0 <= 0; else cnt0 <= cnt0 + 1'b1; endendassign add_cnt0 = add_flag;assign end_cnt0 = add_cnt0 && cnt0 == 5208 - 1;

//10比特数据发送计数器always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt1 <= 0; end else if(add_cnt1)begin if(end_cnt1) cnt1 <= 0; else cnt1 <= cnt1 + 1'b1; endendassign add_cnt1 = end_cnt0;assign end_cnt1 = add_cnt1 && cnt1 == 10 - 1;

//add_flagalways @(posedge clk or negedge rst_n)begin if(!rst_n)begin add_flag <= 0; end else if(tx_vld)begin add_flag <= 1; end else if(end_cnt1)begin add_flag <= 0; endend

//装载数据always @(posedge clk or negedge rst_n)begin if(!rst_n)begin tx_data_temp <= 0; end else if(load_data)begin tx_data_temp <= {1'b1,tx_data,1'b0}; endendassign load_data = tx_vld && !add_flag;

//发送数据always @(posedge clk or negedge rst_n)begin if(!rst_n)begin uart_tx <= 1;//1空闲位 end else if(en_send)begin uart_tx <= tx_data_temp[cnt1]; endendassign en_send = add_cnt0 && cnt0 == 0;

endmodulemodule UART_PORT( clk , rst_n , rx_uart , tx_vld , tx_data , rx_data , uart_tx);input clk;input rst_n;input rx_uart;input tx_vld;input [8-1:0] tx_data;output [8-1:0] rx_data;output uart_tx;

wire [8-1:0] rx_data;wire uart_tx;

uart_rx UART_RX( .clk (clk), .rst_n (rst_n), .rx_uart(rx_uart), .rx_data(rx_data));

uart_tx UART_TX( .clk (clk), .rst_n (rst_n), .tx_vld (tx_vld), .tx_data(tx_data), .uart_tx(uart_tx));

endmodule声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/天景科技苑/article/detail/952109

推荐阅读

相关标签