- 1【计算机毕设选题】2025计算机毕业设计选题参考大全_2024计算机系毕业设计题目推荐

- 2【基于Docker-Compose安装ELK日志系统完整操作步骤】

- 3python爬取有声小说_2019-04-23-Python爬取有声小说

- 4Spark Streaming实时流处理原理与代码实例讲解

- 5文献阅读(二):On Adversarial Robustness of Trajectory Prediction for Autonomous Vehicles

- 6Ubuntu 安装JDK,Mysql,Nginx 配置环境_ubuntu nginx 并配置环境变量

- 7makefile教程_makefile:252:

- 8大数据量下协同推荐的难点与优化方法

- 9exif linux php扩展_开启PHP exif扩展方法详解

- 10MySQL(三)MySQL-5.7.20 主从复制实战(半同步复制、过滤复制、GTID模式)_mysql5.7 主从过滤复制

FPGA DDS配置实践 保姆级教程_dds 使用教程

赞

踩

担心自己以后忘记了,提前来记录一下学习过程。

在这之前建议先观看小梅哥的DDS讲解会让你对DDS的基本构架有大致了解

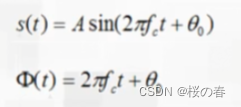

其次想看熟悉这几个公式,后面内容和这几个公式都息息相关

fclk 时钟频率 fout 输出频率 Bθ是位宽 Δθ是频率控制字

最小频率分辨率=fclk 时钟频率 /2的 Bθ次方 这里会和Mode of Operation的模式选择有关,模式不同计算公式不同

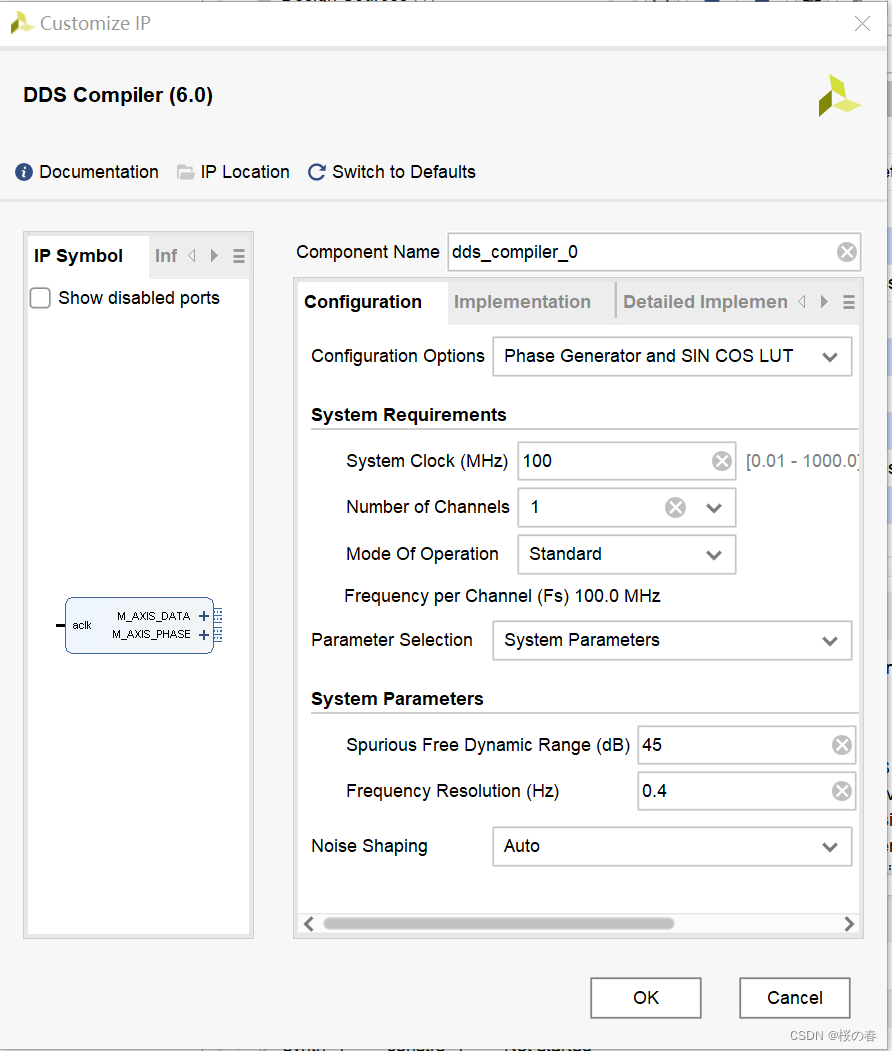

1.先在IP Catalog 中直接搜DDS导入DDS Compiler IP

2.模式选择

DDS IP核可以配置为三种模式:相位产生器、SIN/COS LUT或者相位累加器和SIN/COS LUT(即DDS)

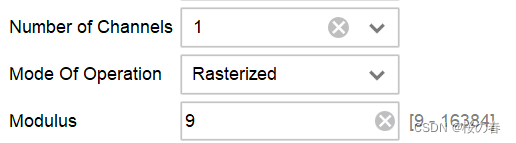

Mode of Operation的模式选择有两种,会决定最小频率分辨率的计算方式不同

Standard:最小频率分辨率=fclk 时钟频率 /2的 Bθ次方

Rasterized:最小频率分辨率=fclk 时钟频率 /设定的Modulus

理论上说Rasterized精度比Standard高因为设定的Modulus 不想2的 Bθ次方 ,收到2的次方倍数限制

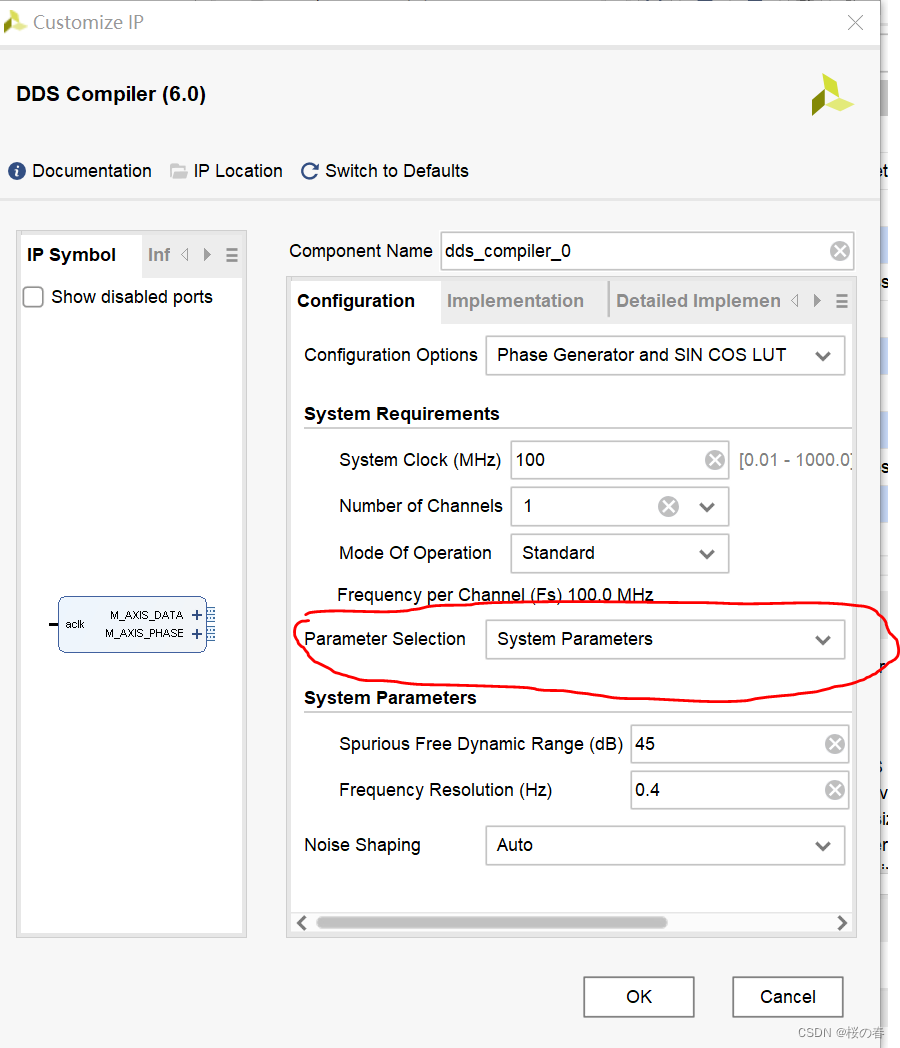

3.频率输入方式选择

parameter Selection有两种选择

System Parameters输出频率可以在IP核中直接输入。

Hardware Parameters输出频率可以在在IP核中或者程序中输入频率控制字PINC来确定输入。

4.1这里先选System Parameters

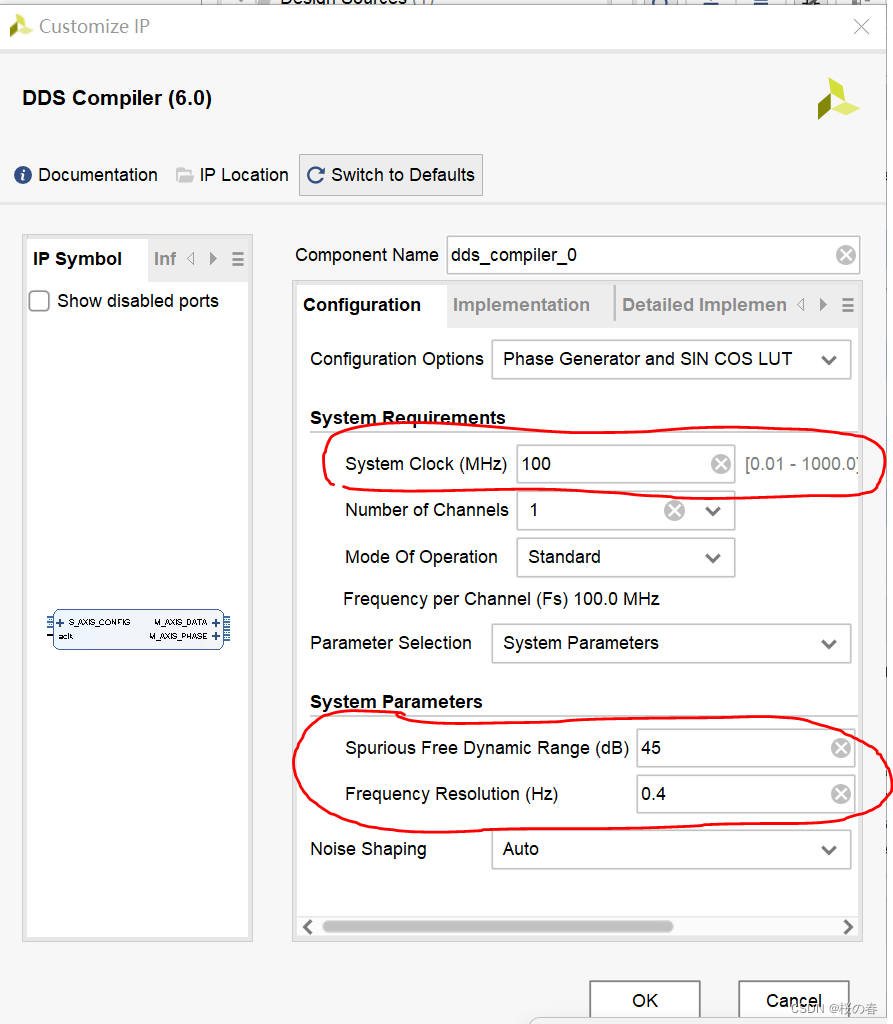

Spurious Free Dynamic Range 是输出信号的幅度.那这里为什么用bB单位呐,其实这中间经过了一些列计算简化后的,其计算公式如下:20*lg(信号的幅度),举个例子,Dpurious Free Dynamic Range为72bB,那么他就表示幅度为[20*lg(信号的幅度)] = 20*3.612约等于72dB;所以72dB等价于这是一个信号的幅度为4096的一个信号。所以Spurious Free Dynamic Range越大表示信号的幅度越大。具体数值具体计算。

Frequency Resolution是频率分辨率,对应这最小的频率变化,是由系统时钟和相位深度计算得到的,比如系统时钟System Clock MHz,相位宽度(用xx位二进制来表示相位),那么计算的频率分辨率就是 总频率/(相位总刻度)=hz/每相位刻度=频率分辨率 。 所以 Frequency Resolution越小,在系统时钟确定的情况下,频率变化的刻度也就越小。

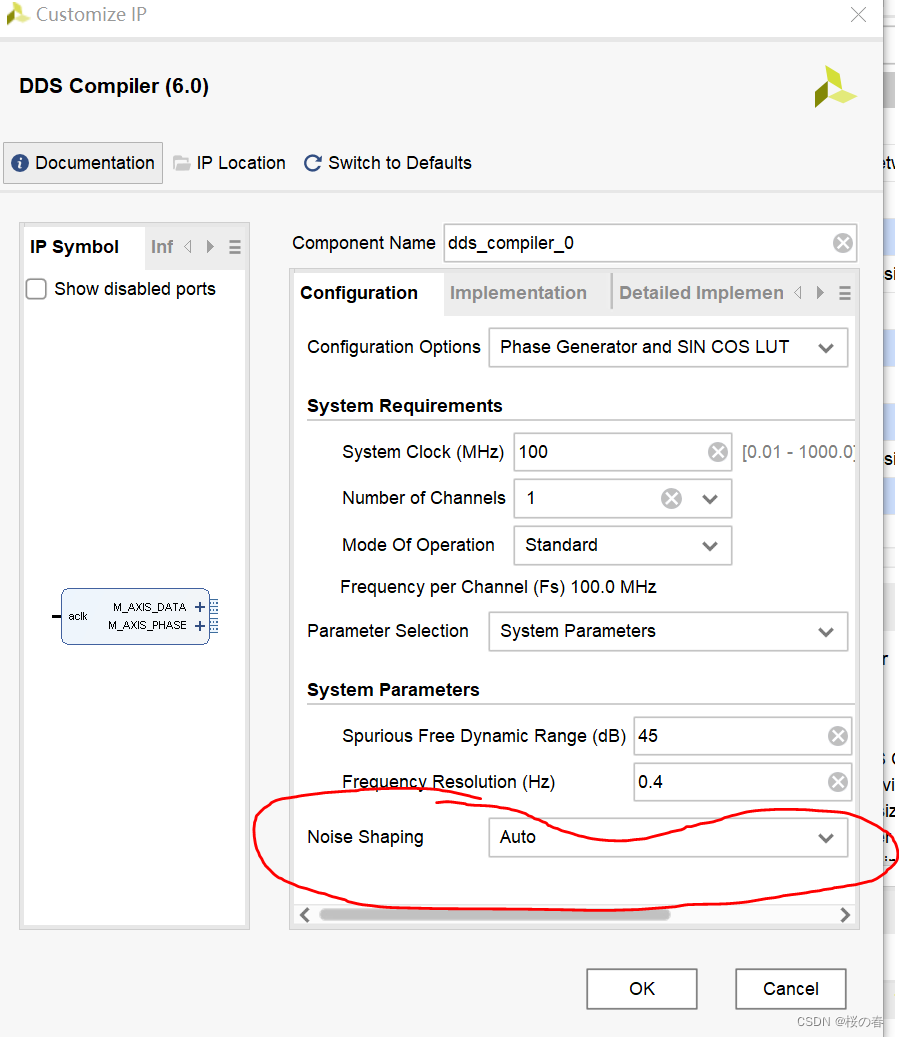

此处还需要配置Noise Shaping,

三种模式:None,Phase Dithering,auto

这里先选AUTO

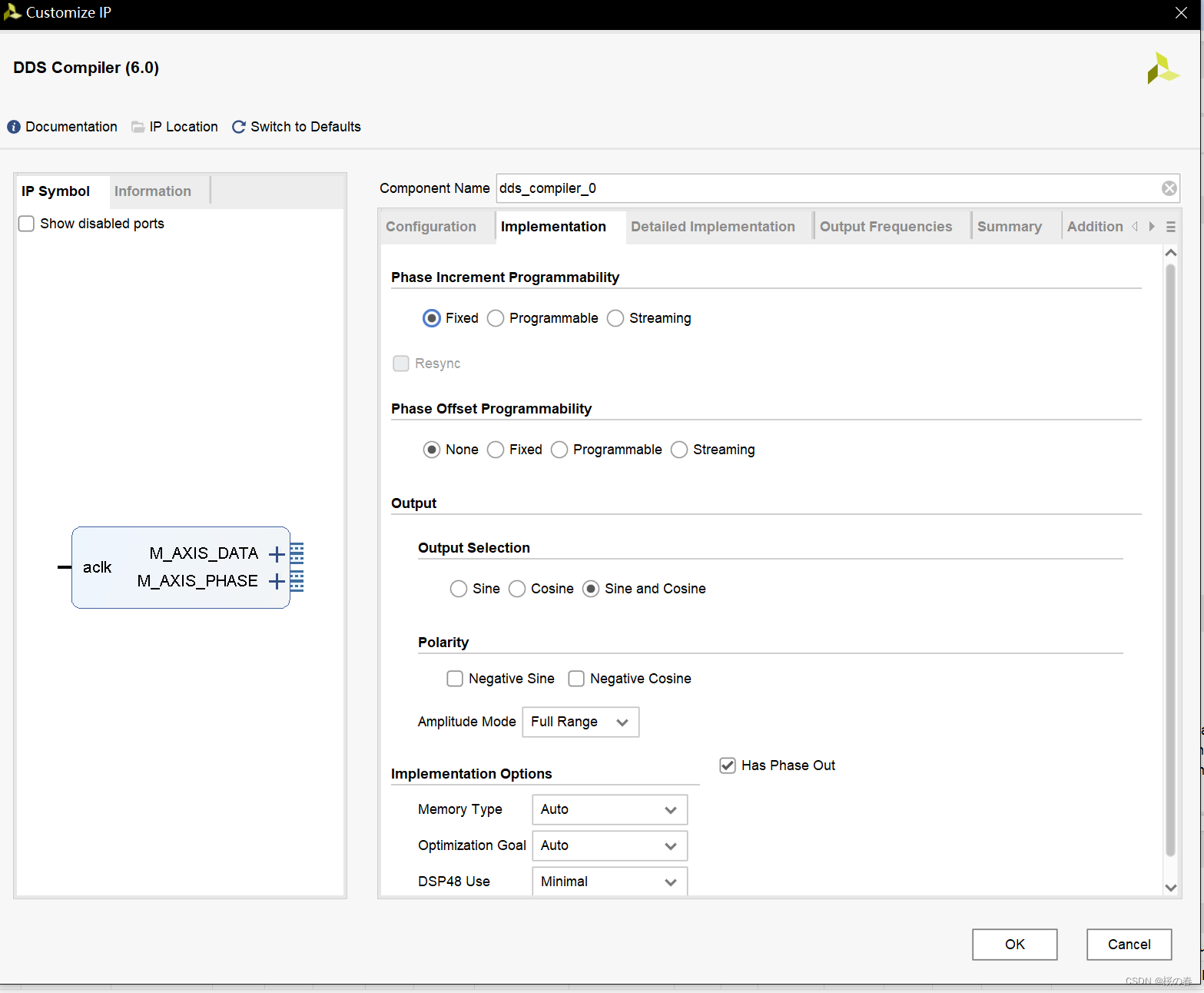

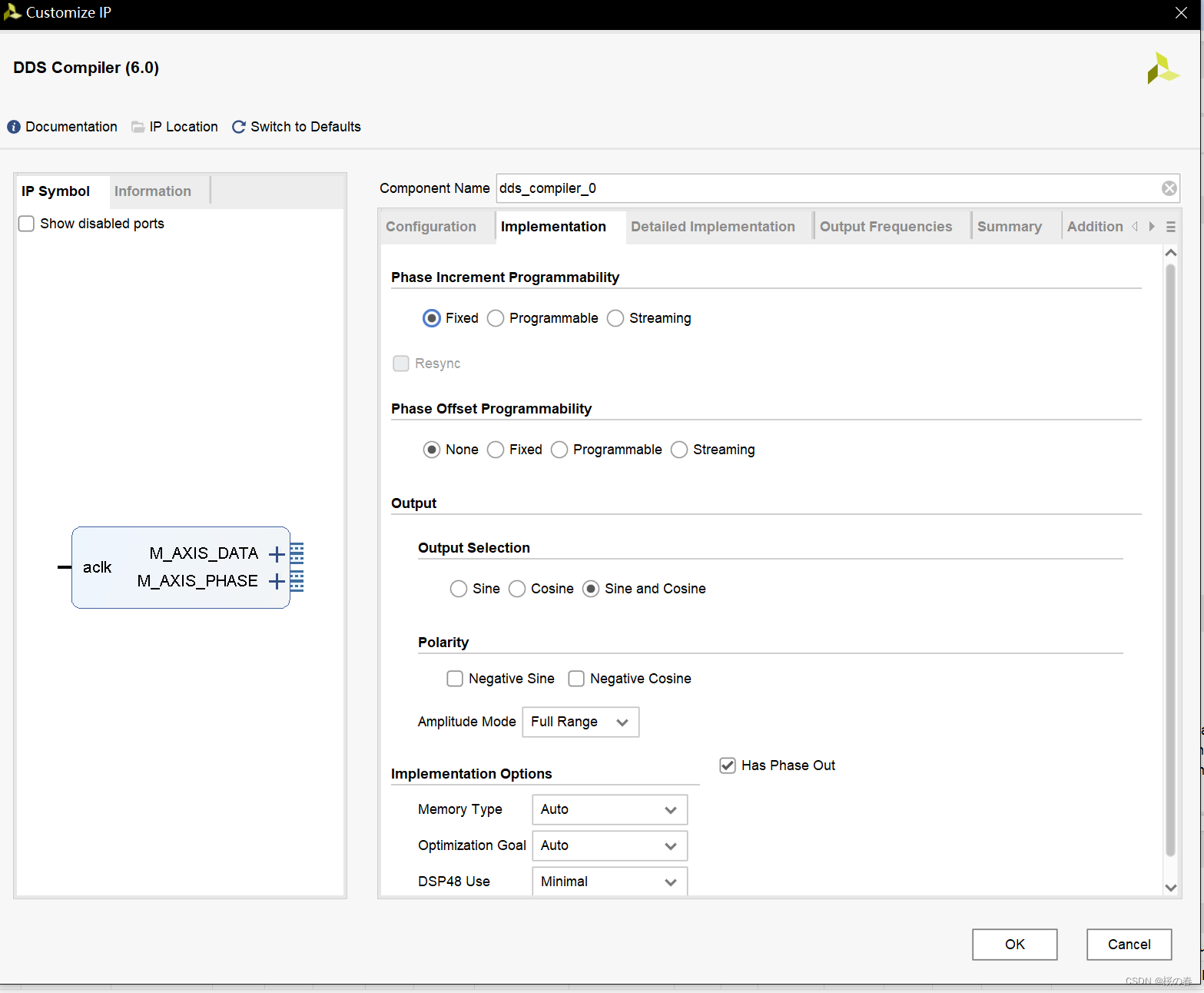

4.1.2进入下一个Implementation界面配置

.Phase Increment Programablilty 设置相位增量(相位增量能够控制输出的正余弦信号的频率)

是固定(Fixed)的还是更改(Programable,streaming{一般SM,DM时使用streaming})的

同时需要注意的时候,生成的信号需要满足奈奎斯特抽样定理,系统时钟和生成正余弦信号的频率最大值要满足2:1的的关系

eg.系统时钟为100M,那么,最多可以生成频率为50MHz的正余弦信号

Fixed 固定 Programable 和 Streaming都是可更改

一般选Programable 或者 Streaming{一般SM,DM时使用streaming}

.Phase Offest Programablilty 设置初始的相位是固定的还是更改的

None 不设置0

Fixed 固定的 Programable 和 Streaming都是可更改

根据需求选择这里先选None不更改

Output Selection 输出波形选择

Has Phase Out 是否同时输出相位信号 根据需求选择这先勾选

其余的建议默认

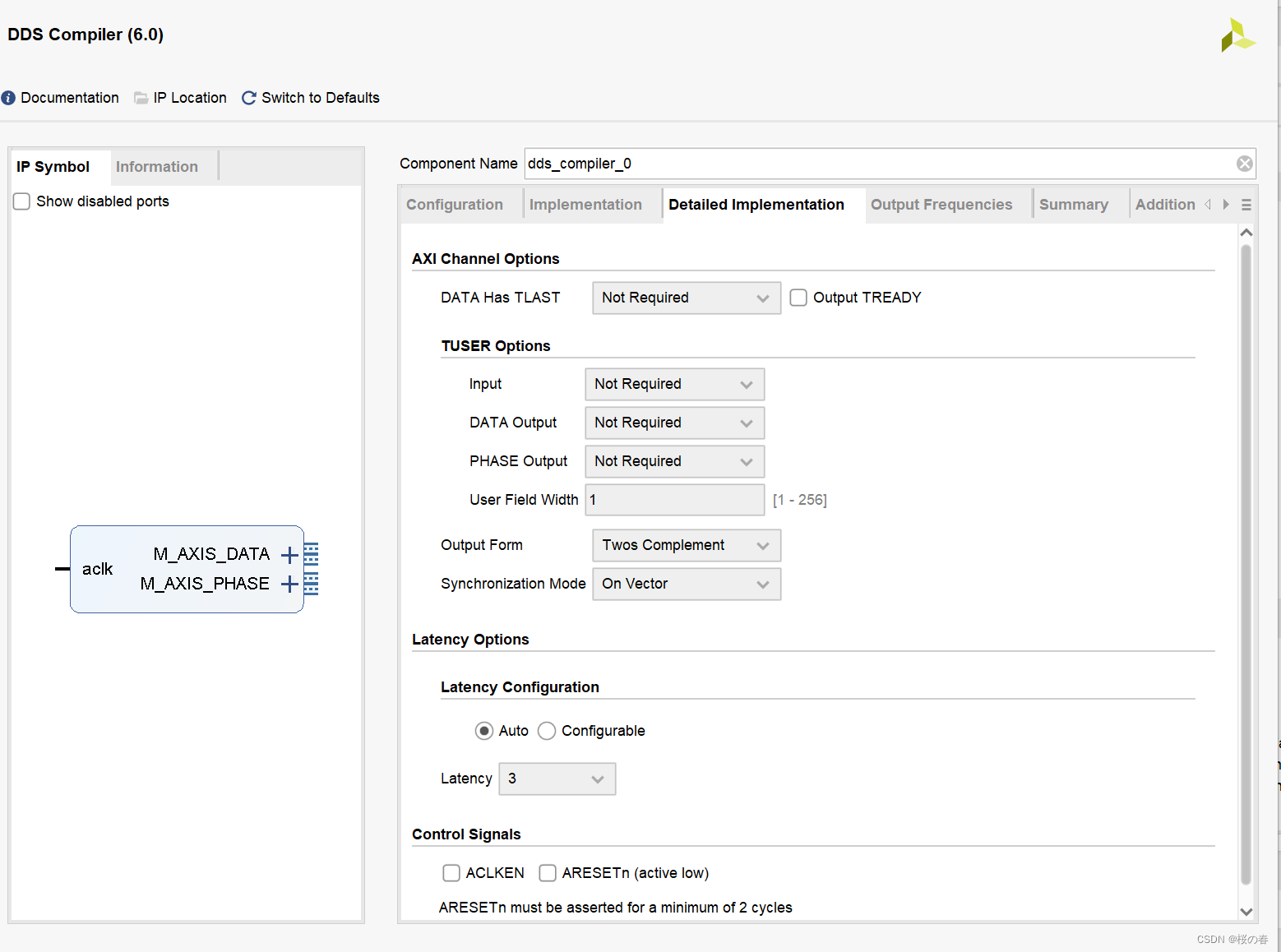

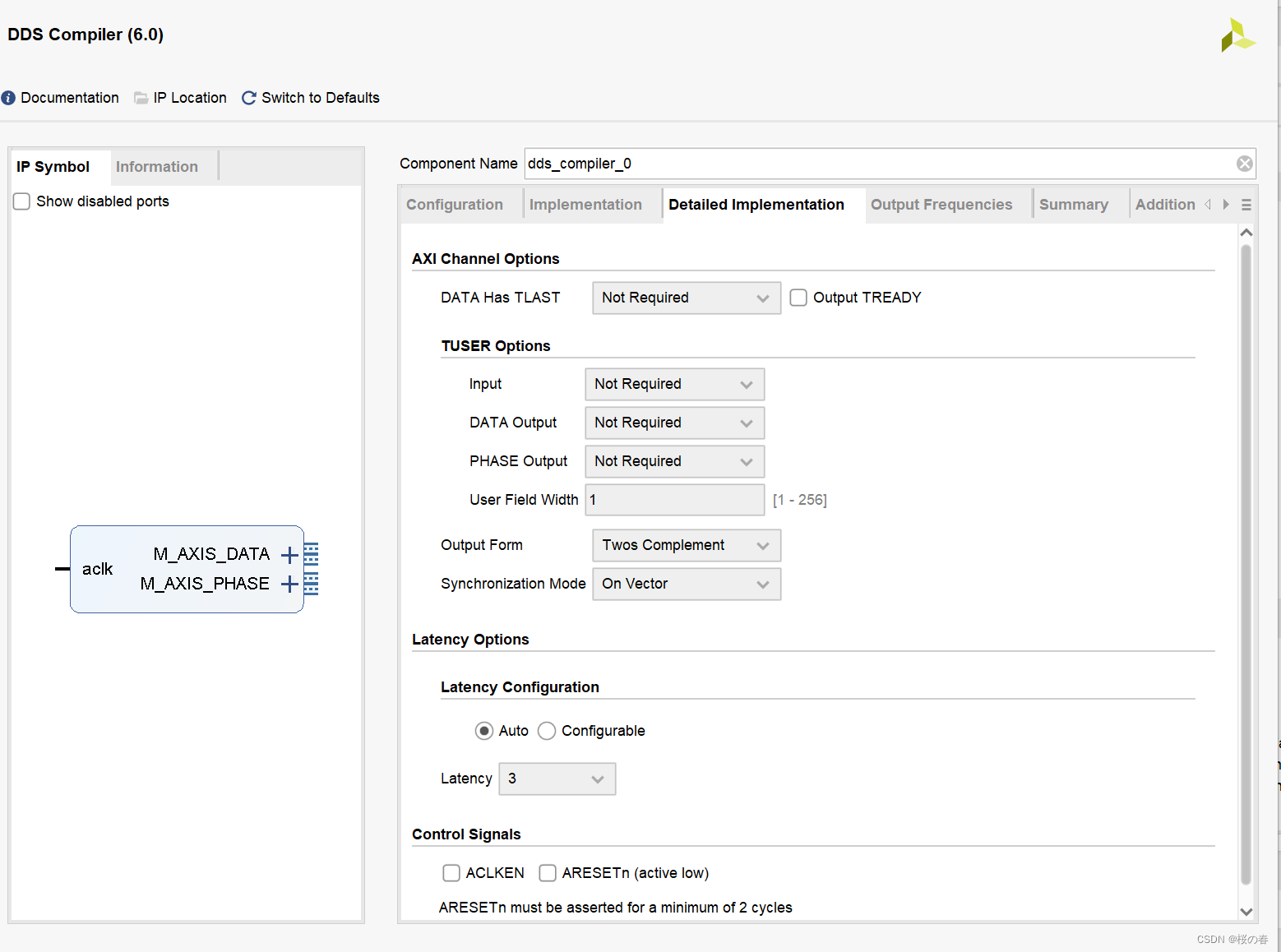

4.1.3进入下一个Detailed界面配置

这个页面主要是用来配置接口

output TRADY是输入的TRADY信号(输入信号)告诉这个ip是否准备好发送波形信号

latency options是关于延时的设置

这里基本保持默认

4.1.4进入下一个界面Output Frequencies配置

就是配置你想要的输出波形频率

.只能在(4.1.2中)Phase Increment Programablilty 设置相位增量的Fixed和Programable模式更改有用

在Fixed模式下就是此处固定的频率不改变

在Programable模式下就是初始一个频率后面通过输入来改变频率

但注意这个期望频率在前面选择了相位增量式可编程的时候就没什么用了。因为最终输出的信号的频率是通过相位增量来控制的

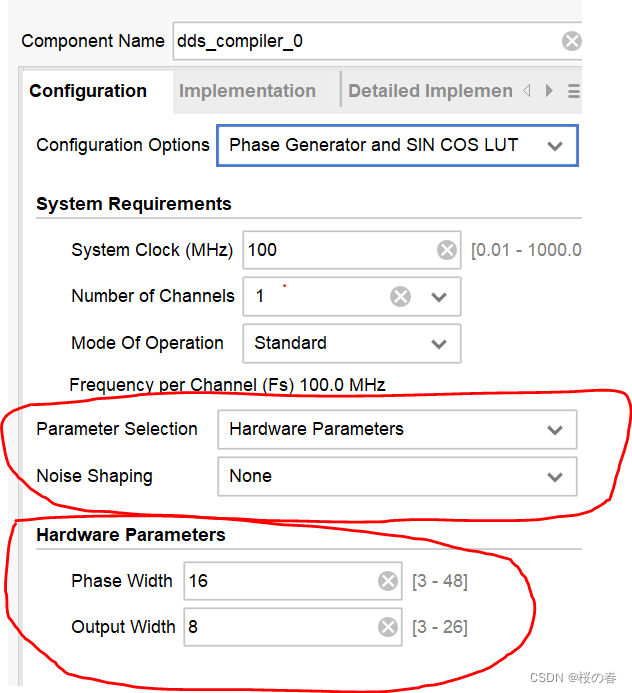

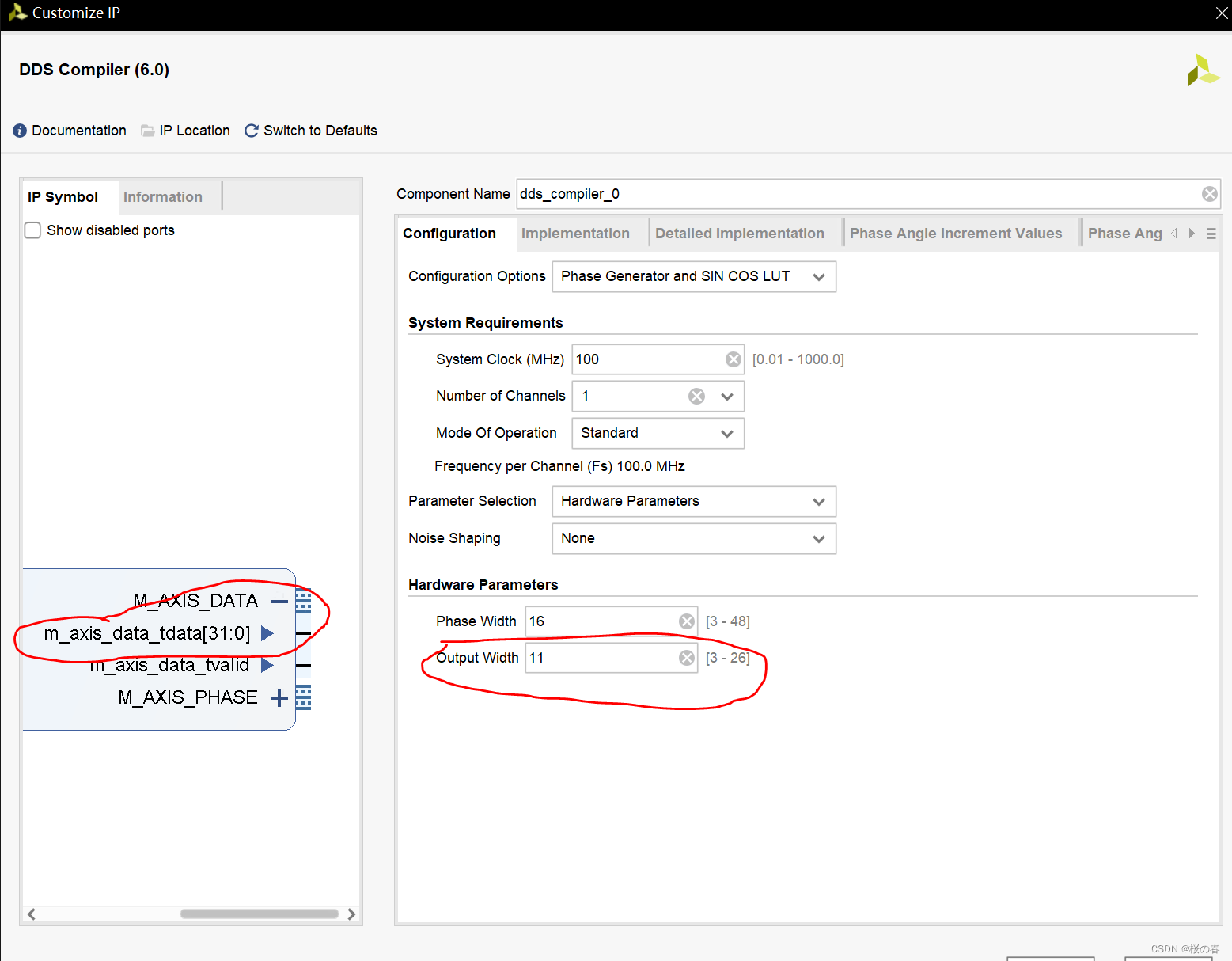

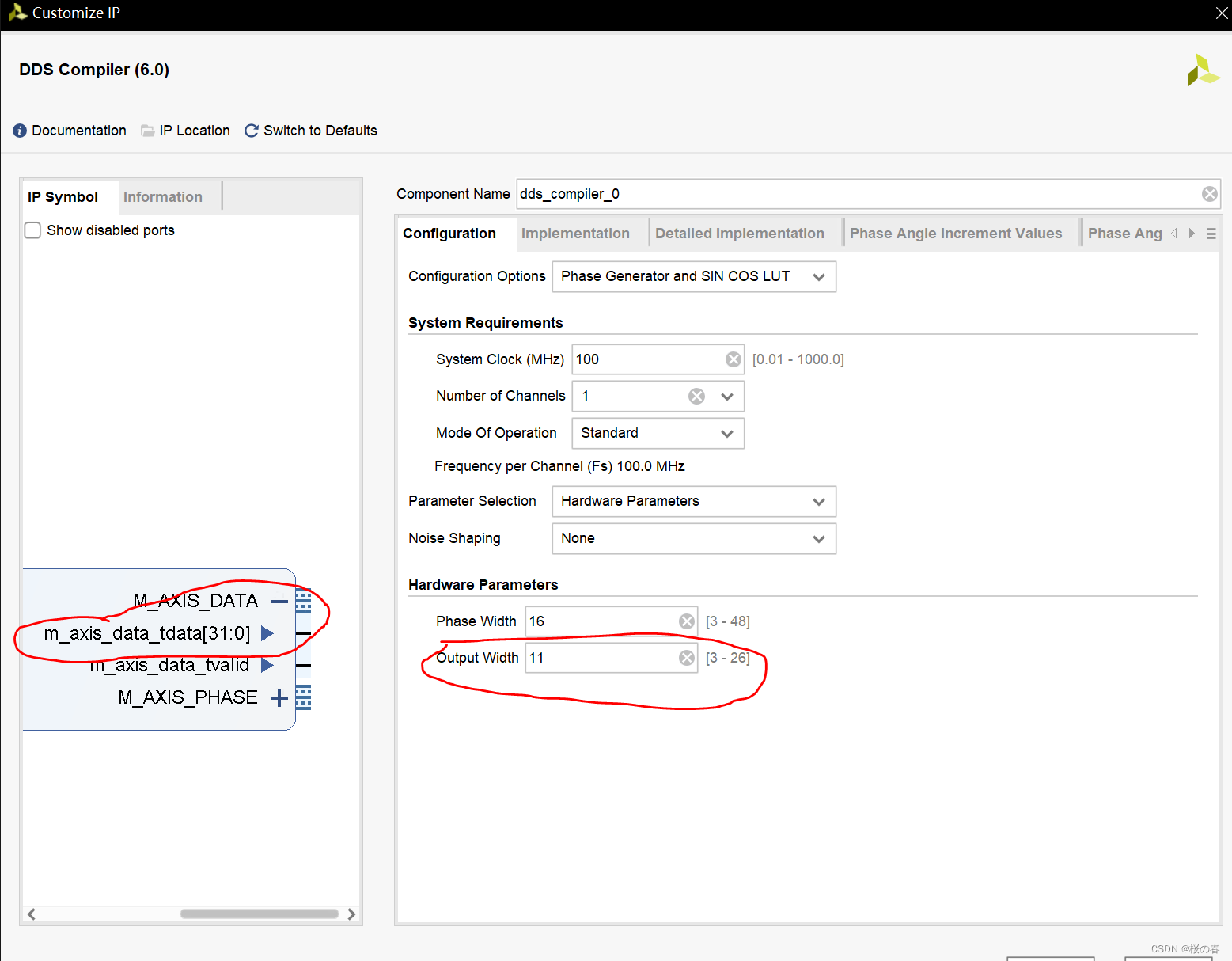

4.2.频率输入方式选择HARDWARE Parameters

这里选HARDWARE Parameters

phase width是相位累加器的位宽

output width是输出波形的位宽(一般和DAC芯片匹配)

但注意这个ip的输出位数不管你输入的多少一定是8的倍速的输出位数,多余的输出位数就为无效位数。

eg.这里设置输出位数为11位,实际ip的输出位数(m_axis_data_tdata)是16位(在cos或者sin输出模式下)

32位(在cosine and sine输出模式下){4.2.2节有配置这个的介绍}

4.2.2进入下一个Implementation界面配置

.Phase Increment Programablilty 设置相位增量(相位增量能够控制输出的正余弦信号的频率)

是固定(Fixed)的还是更改(Programable,streaming{一般SM,DM时使用streaming})的

同时需要注意的时候,生成的信号需要满足奈奎斯特抽样定理,系统时钟和生成正余弦信号的频率最大值要满足2:1的的关系

eg.系统时钟为100M,那么,最多可以生成频率为50MHz的正余弦信号

Fixed 固定 Programable 和 Streaming都是可更改

一般选Programable 或者 Streaming{一般SM,DM时使用streaming}

.Phase Offest Programablilty 设置初始的相位是固定的还是更改的

None 不设置0

Fixed 固定的 Programable 和 Streaming都是可更改

根据需求选择这里先选None不更改

Output Selection 输出波形选择

sine cosine sine和cose 三种会影响输出的位数,毕竟多了一种波形数据输出肯定要多点位数

eg.这里设置输出位数为11位,实际ip的输出位数(m_axis_data_tdata)是16位(在cos或者sin输出模式下)

32位(在cosine and sine输出模式下){4.2.2节有配置这个的介绍}

具体的输出有效位数是多少位见官方手册

Has Phase Out 是否同时输出相位信号 根据需求选择这先勾选

其余的建议默认

4.2.3进入下一个Detailed界面配置

这个页面主要是用来配置接口

output TRADY是输入的TRADY信号(输入信号)告诉这个ip是否准备好发送波形信号

latency options是关于延时的设置

这里基本保持默认

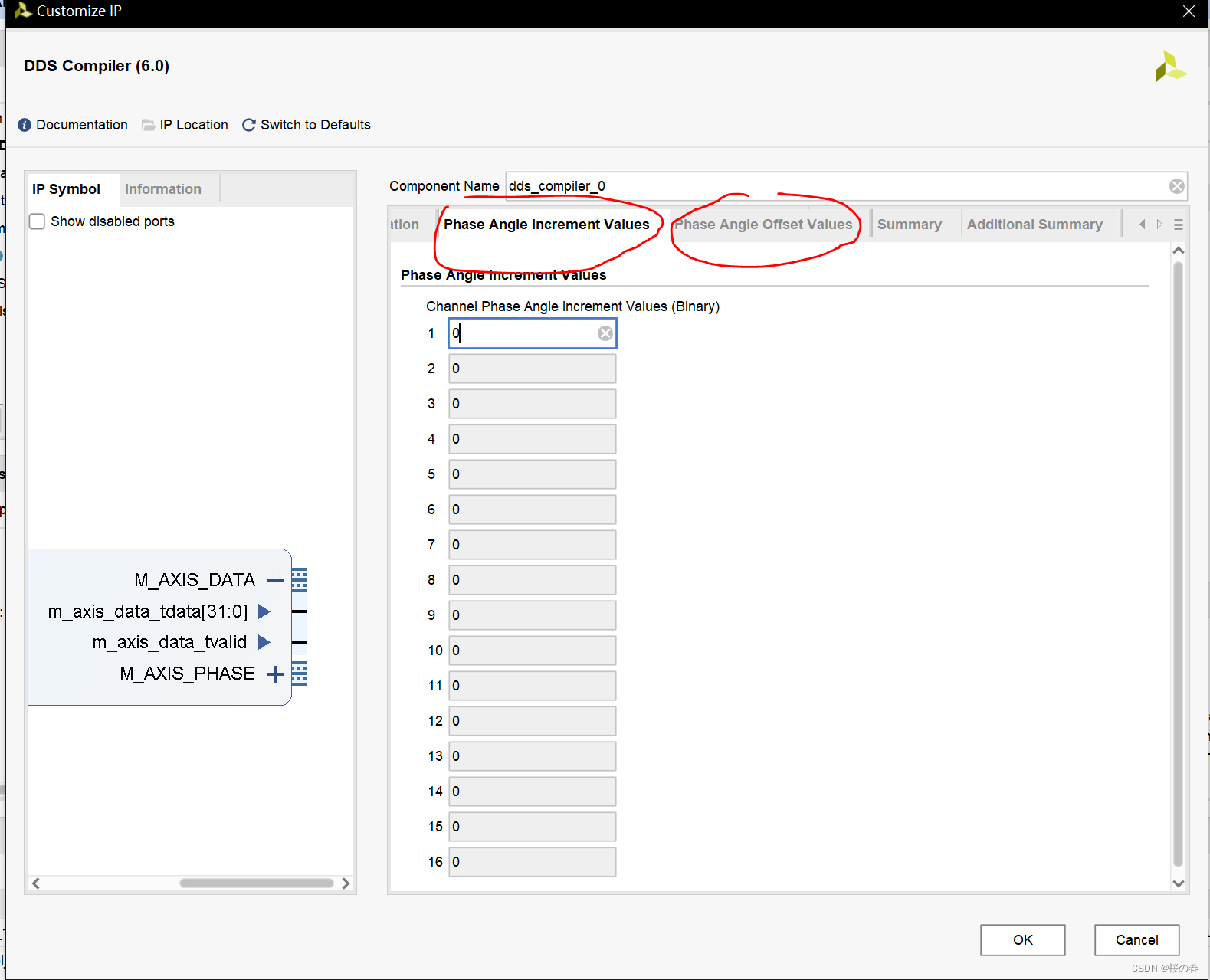

4.2.4进入下一个界面Output Frequencies

和

Phase Angle Offest Values配置

界面Output Frequencies配置就是配置你想要的输出波形频率

.只能在(4.1.2中)Phase Increment Programablilty 设置相位增量的Fixed和Programable模式更改有用

在Fixed模式下就是此处固定的频率不改变

在Programable模式下就是初始一个频率后面通过输入来改变频率

但注意这个期望频率在前面选择了相位增量式可编程的时候就没什么用了。因为最终输出的信号的频率是通过相位增量来控制的

界面Phase Angle Offest Values配置就是配置你想要的输出波形相位

配置和模式相关和上述雷同

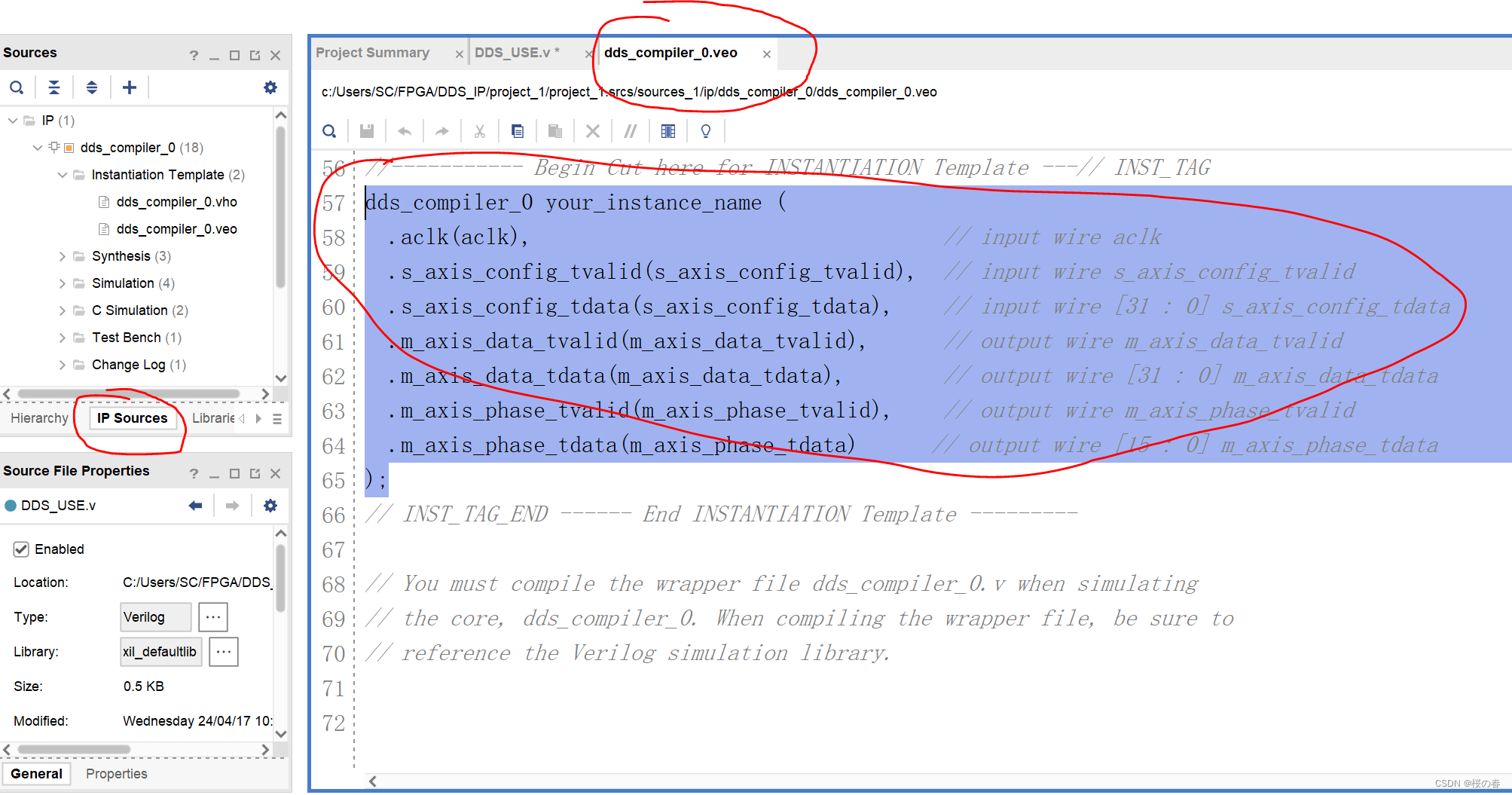

5.0模块例化

生产ip选ip sources的dds_complier_0.veo指定部分是例化模块

端口解析:

aclk时钟端口

s_axis_config_tvalid端口是axi4协议的允许输入端口

s_axis_config_tdata端口是axi4协议的数据输入端口(eg.此处32位)

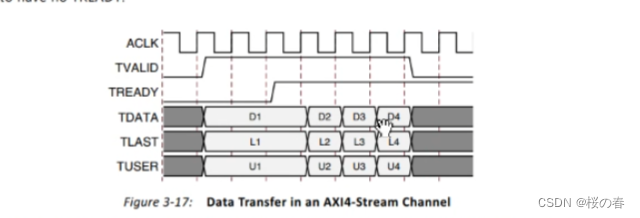

看懂协议原理就懂了原理图如下

当tvalid拉高时,过段时间TREADY输出口(4.2.3和4.1.3有配置教程)就会拉高

当两者同时拉高时,真正开始接收数据