- 1TPAMI 2023 | 无监督域适应语义分割新视角:统一图像和特征层次的对齐

- 2【Python】flask实现登录注册_flask登录注册

- 3李宏毅2023机器学习作业HW06解析和代码分享

- 4原来我一直被骗了!Burp suite诱导劫持攻击【附工具】_burp重发器合法吗

- 5多路开关模式的switch语句_c语言十个开关

- 6【k8s】K8S中的IP地址(Node IP、Pod IP、Cluster IP、External IP、Internal-IP)

- 7Android中View(视图)绘制不同状态背景图片原理深入分析以及StateListDrawable使用详解_安卓代码设置背景图片

- 8Spark-数据倾斜及解决方案_spark数据倾斜和解决办法

- 9黑客入门破解网络密码常用九个方法_破译密码

- 10vscode本地修改后未提交,git如何切换分支,不会覆盖本地修改_签出会覆盖本地更改

学习如何独立的使用Modelsim进行仿真验证?——编写verilog文件并查看仿真波形_verilog仿真波形图怎么弄出来

赞

踩

本篇记录如何独立的使用Modelsim进行仿真,便于之后查看。

Modelsim独立仿真的步骤:

创建工作文件夹——编译设计文件——导入及运行仿真——调试结果

具体的:

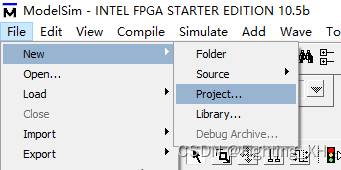

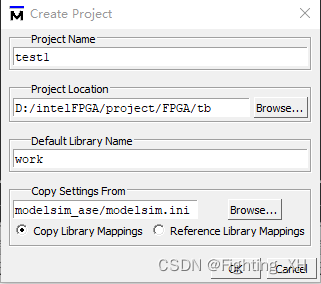

1、新建一个工程

指定工程名称、路径和默认库名称。一般情况下,设定Default Library Name默认库名称为work。

指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。选择.ini文件可以映射库设置,或者将其直接拷贝至工程中。

设置完成后ok。

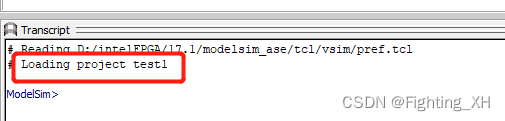

我们就能在报告单中看到我们建立的工程 test1

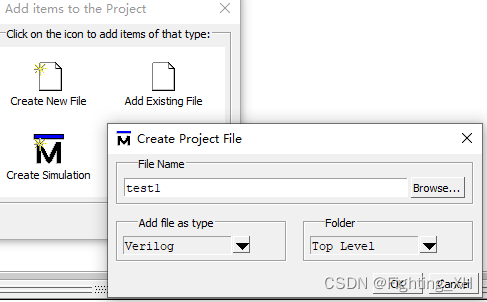

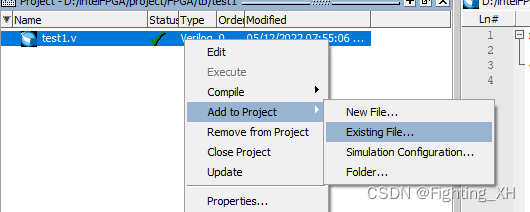

2、创建文件

ok后出现Add Items to the Project的对话框,包含四个类型如下:

Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL或文本文件

Add ExistingFile——添加一个已存在的文件

Create Simulation——创建指定源文件和仿真选项的仿真配置

Create New Folder——创建一个新的组织文件夹

我们这里选择第一个并给予文件名称以及使用的语言。

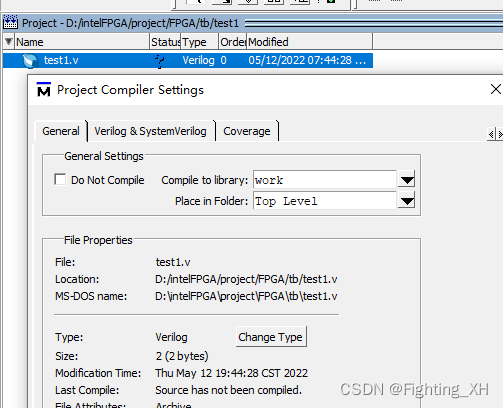

我们在project栏中就可以看到我们新建的tset1文件。右键选择属性properities,可看到是在我们之前指定的文件夹中

3、编写V文件

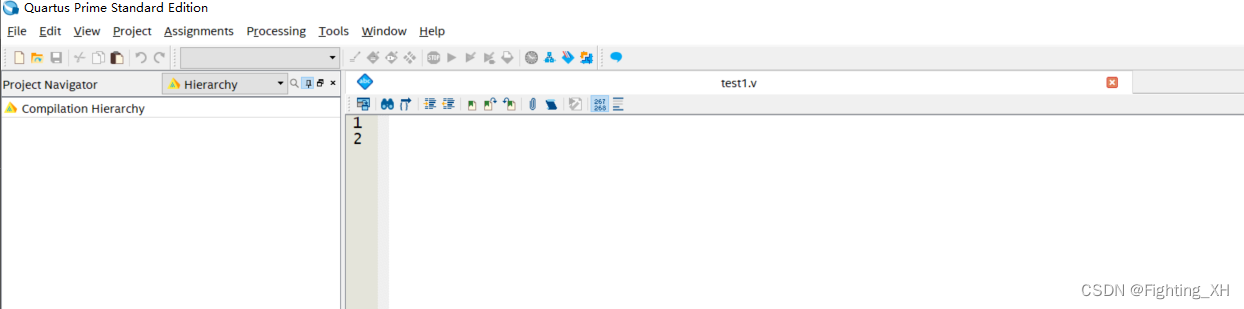

双击tset1即可打开编写,我这里是quartus软件作为编辑器,所以会自动打开quartus软件。在里面编写verilog代码即可。——写tb测试代码

引入随机函数,随机产生两位输入in进行模块的测试。待测试模块实现的功能是与操作。

module test1 (); reg [1:0] in=2'b0; integer i = 89; integer j = 9; //产生随机输入激励 initial begin #10; in = $random(j); #10; in = {$random(i)}%3; //产生0-3 之间的值 #10; in = $random(j); #10; in = $random(i); #10; in = $random(i); #10; in = $random(i); $display ("Hello world! The current time is (%0d ps)", $time); #50 $finish; end andgate u1( .in(in), .out(out) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

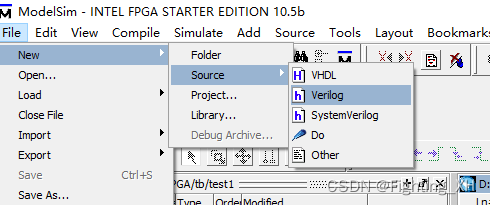

然后新建一个verilog文件,来写待测试的verilog代码

module andgate(in,out);

input [1:0] in;

output out;

assign out = in[0] & in[1];

endmodule

- 1

- 2

- 3

- 4

- 5

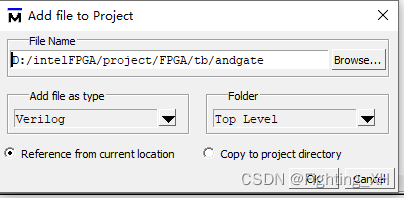

将新写的source v文件加入进去

确定好文件路径以及语言ok

4、编译

在上方的对话选择Compile<Compile ALL,报告单提示没错即可。

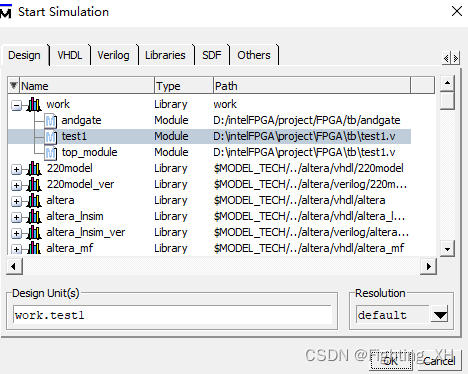

5、开始仿真

在上方对话框选择Simulation ——Start Simulation ,在work中选择我们写的test1 ,ok

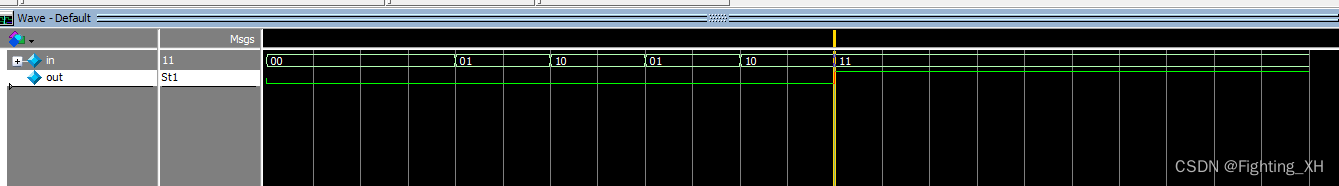

跳转如下的界面,这里将所有的信号加入到波形中

然后点击run-all即可出现波形:

其中in为输入,同时是用随机函数随机产生的,这里不多解释,重点看来结果,由于in是两位的,且两位进行与操作,可看到当in = 2‘b11的时候,输出out为高电平,因此逻辑设计正确。

结语

学习如何采用Modelsim进行独立仿真,在用quartus的时候,如果编写的逻辑不可综合,那么就不能进行仿真,本文的例子在使用random函数的时候出错,显示不可综合,因此这里按照学弟给予的方式,直接用Mdoelsim仿真。另外也可以采用HDLbits提供的仿真器来实现仿真。