- 1python官网下载windows版本时各文件的区别:web-based installer、executable installer、embeddable zip file,x86、x86-64_windows x86-64 web-based installer

- 2安卓pdf阅读器_PDF阅读用哪款软件好?推荐这7款,简单又好用!

- 3web安全--Xml外部实体注入漏洞(XXE)与防护_org.xml.sax 漏洞

- 4CentOS7 yum cannot find a valid baseurl for repo base 7x86_64 解决办法

- 5千字Java学习路径,超全!从零基础到精通~

- 6UI 测试与接口测试的区别与应用_接口测试和ui测试的区别

- 7这篇文章带你从入门级开始学习网络安全_逆向漏洞挖掘复现

- 8【openCV】读取视频、调用摄像头/电脑摄像头_opencv读取摄像头

- 92024年Python 学习路线(2024)_雪峰python教程网站

- 10R语言对医学中的自然语言(NLP)进行机器学习处理(1)_r语言nlp

Vivado使用入门之二:网表物理约束_vivado enter assign routing

赞

踩

目录

一、背景

在工程设计中为了保证上板后功能正常,需对设计定义相关的约束要求。约束根据设计对象的不同可分为时序约束(对时钟)和物理约束(对网表),根据流程可划分为综合约束和实现约束,本文主要讲解物理约束,示例器件为xc7k410tfbv900 ,vivado版本为2019.1。

二、物理约束

2.1 概念

物理约束包括I/O位置约束,网表单元约束,布局约束,布线约束,约束的内容是保存在XDC(Xilinx Design Constraints)文件或Tcl脚本中,在打开工程时被加载进入工程中,载入工程后也可以对约束进行修改。大部分约束的格式为“set_property <propert_name> <value> <object list> ,区域约束的格式存在差异,格式为“create_pblock block_name re size_pblock [get_pblocks block_name]” -add {cell}

2.2 网表约束

网表约束主要是对如端口ports,引脚pin,线nets和单元cells对象,使综合和实现过程按照指定的方式和进行处理。

网表约束主要有四个

a) CLOCK_DEDICATED_ROUTE

b) MARK_DEBUG

c) DONT_TOUCH

d) LOCK_PINS

2.2.1 CLOCK_DEDICATED_ROUTE

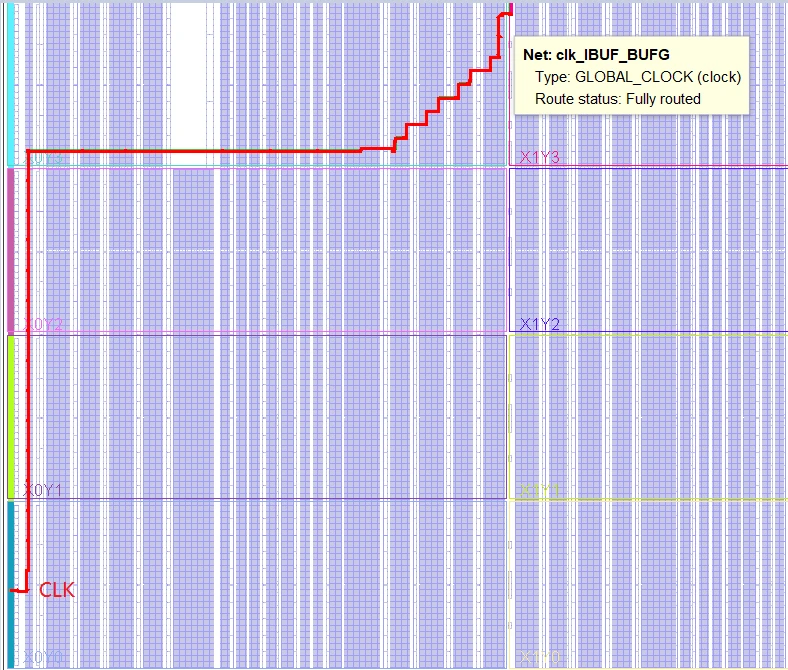

CLOCK_DEDICATED_ROUTE作用对象为net,时钟信号正常是只能通过时钟树到达目的对象的时钟引脚,设置改属性后,时钟信号可走普通线路到达目的对象。缺点是通常走普通线路时延较大,容易导致时序违例。改属性设置为false即为允许时钟从输入端口到达BUFG或MMCM走普通线路。

以一个简单的异步清零寄存器为例,为了构造时钟信号需要走普通线路才能到达的场景,特地将clk端口和FF约束到不同的半区,使用的器件为xc7k480tffv1156-1 (active)

- module dedicate(clk,d,rst,out);

- input clk,d,rst;

- output reg out;

- always @(posedge clk or posedge rst) begin

- if (rst) begin

- out<=0;

- end

- else begin

- out<=d;

- end

- end

- endmodule

XDC约束内容

- set_property BEL AFF [get_cells out_reg]

- set_property LOC SLICE_X189Y393 [get_cells out_reg]

- set_property PACKAGE_PIN AK19 [get_ports clk]

运行到place时报错,符合预期,clk端口无法跨越半个芯片区域到达BUFG,只能到达所属半区的BUFG

对clk net添加属性CLOCK_DEDICATED_ROUTE,布局布线通过

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {clk_IBUF}]左下角的clk端口通过普通布线路径到达BUFG

2.2.2 MARK_DEBUG

在RTL中对net设置MARK_DEBUG,net上的信号会自动地被加入到Debug上,查看Debug上信号的波形,进行功能的确认。添加DEBUG有以下几种方式

方法1、可直接在RTL代码中对net、reg对象标注

- (* mark_debug = "true" *) wire [1:0] data;

- (* mark_debug = "true" *) reg[1:0] state;

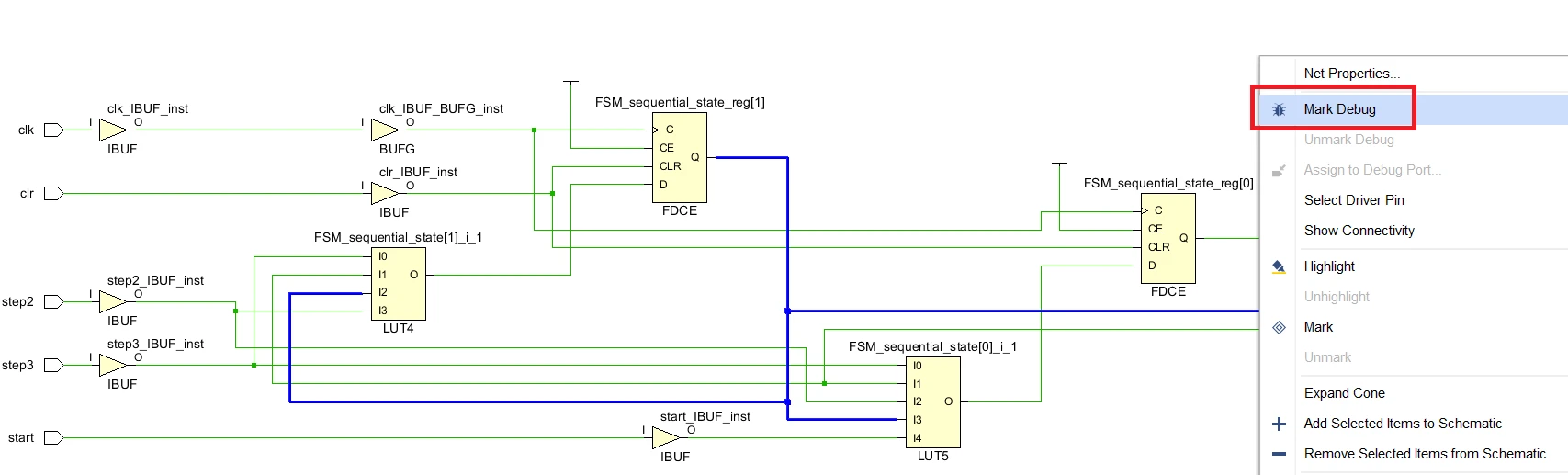

方法2:Schematic中添加

在Schematic图中选定要标记的net,右键弹出设置栏,选择Mark Debug,标记前如下图

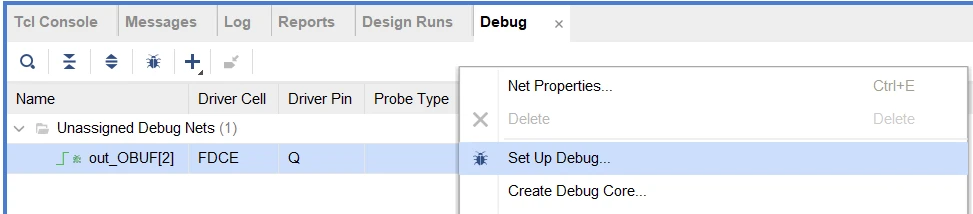

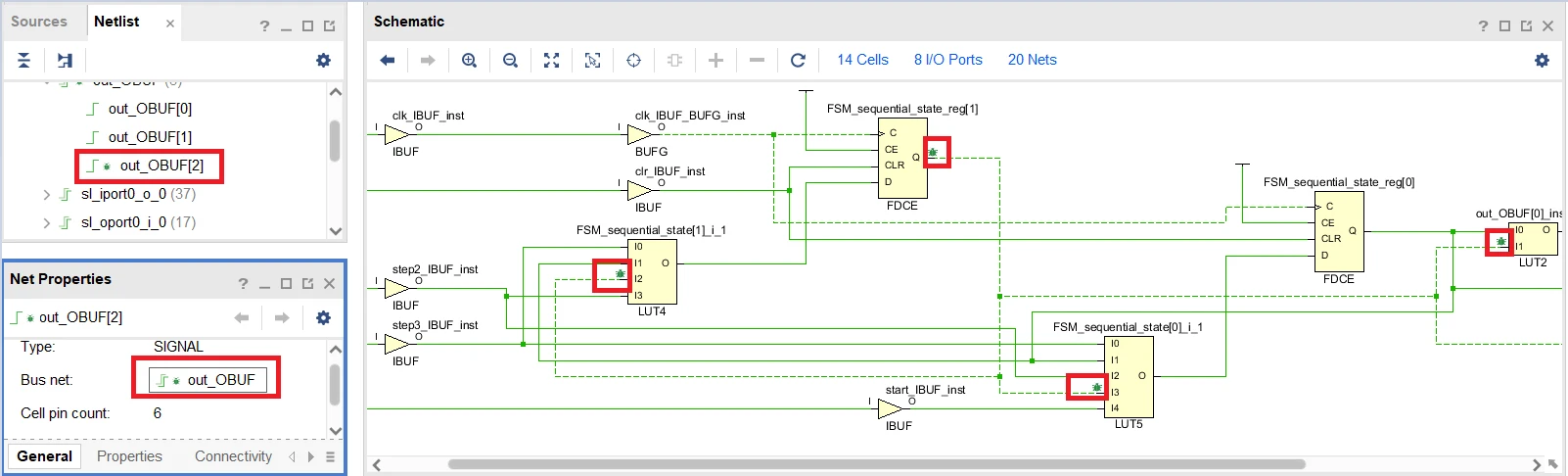

标记后,在Debug窗口对out_OBUF设置Set Up Debug

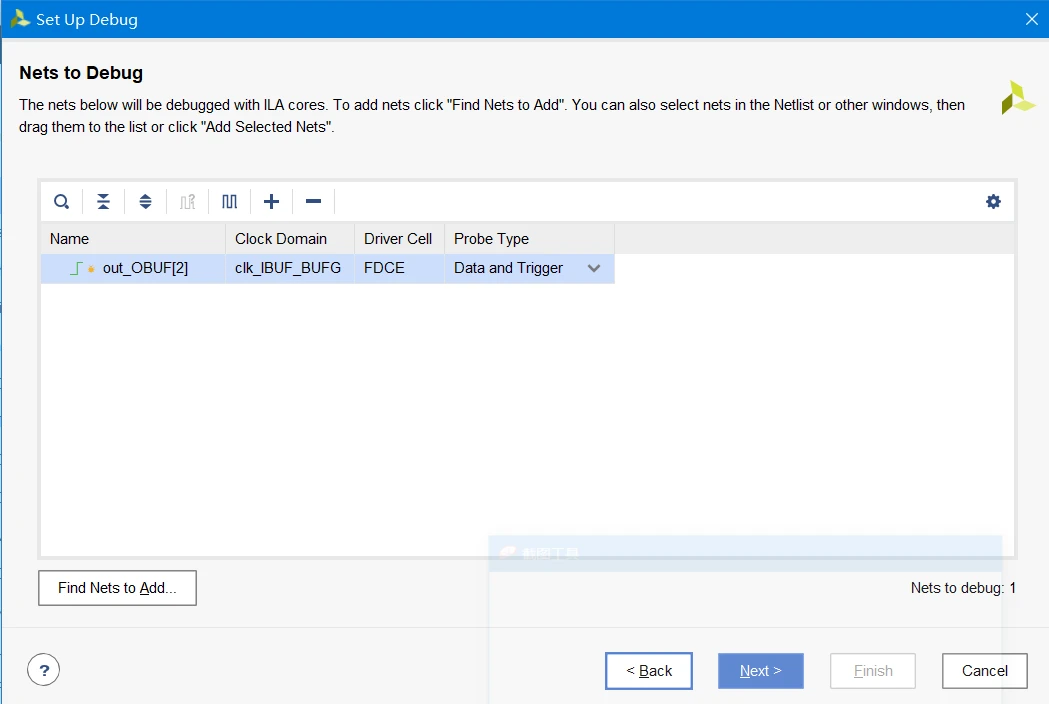

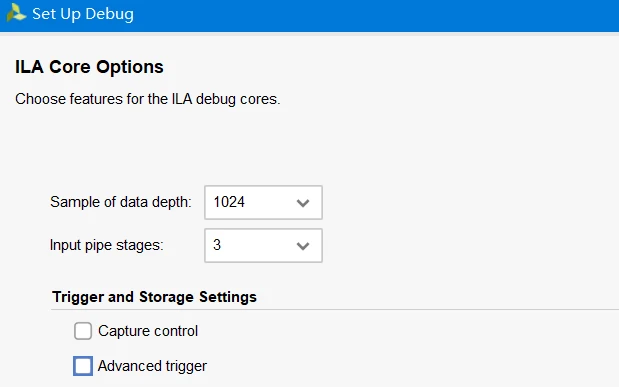

弹出Set Up Debug窗口

设置采样率和输入通道阶段数

设置完成后,在Netlist和Net Properties种,out_OBUF前面有debug标志,Schematic中out_BUF连接的各个pin也带有标志,如红框所示。

2.2.3 DONT_TOUCH

DONT_TOUCH主要是仿真单元或net被优化掉,对于一些逻辑检测或调试很有必要,并且对于一些高扇出的单元,手动复制的寄存器添加属性后也不会被优化。具体的使用方面可参照之前的文章Vivado综合属性系列之七 DONT TOUCH 或CSDN网址:https://blog.csdn.net/zyp626/article/details/130715598

2.2.4 LOCK_PINS

LOCK_PINS用于指定LUT的逻辑约束(I0,...,I5)和Device上LUT单元的物理位置(A1,...,A6)的映射关系,比较常用的场景是将处于关键路径上的LUT的映射到Device中LUT的A5和A6,可以减小时延。

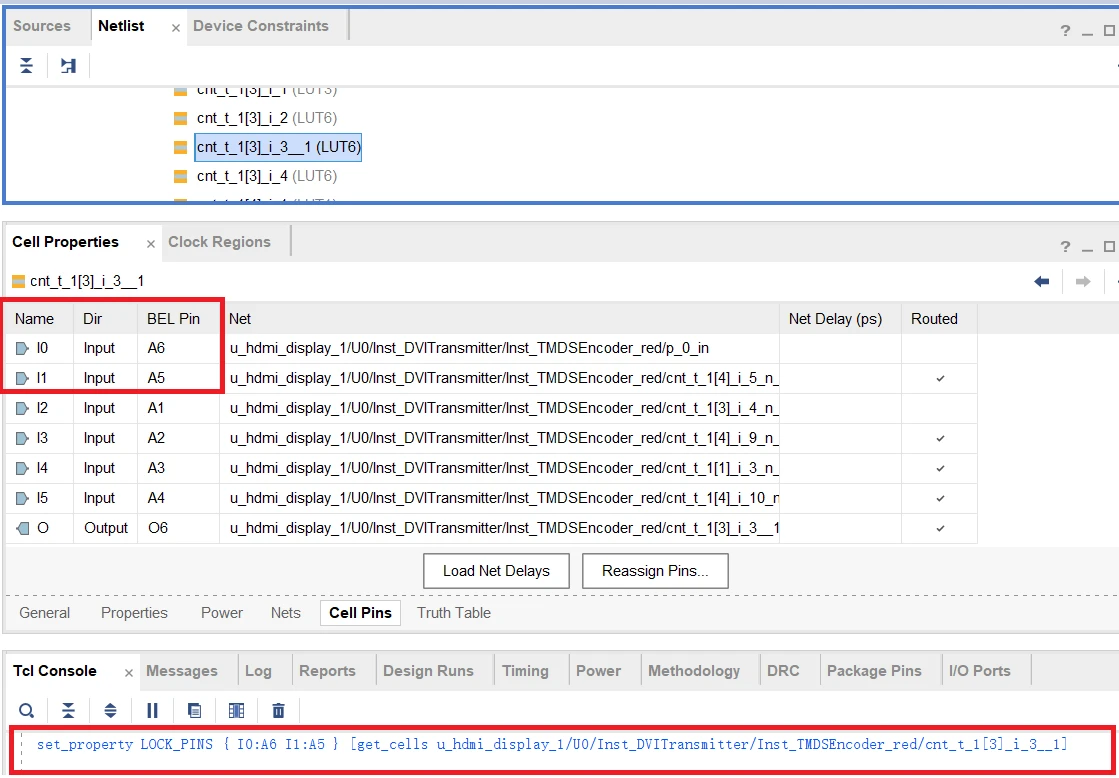

以示例工程中的cnt_t_1[3]_i_3_1(LUT6)为例,inst映射到device的关系见左下角红框,I0对应A4

Tcl Console设置LOCK_PINS属性,I0,I1分别映射为A6,A5

set_property LOCK_PINS { I0:A6 I1:A5 } [get_cells u_hdmi_display_1/U0/Inst_DVITransmitter/Inst_TMDSEncoder_red/cnt_t_1[3]_i_3__1]结果如图所示,映射关系已更改,符合预期

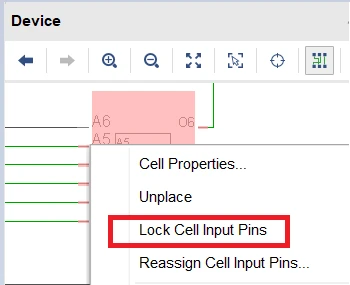

也可在Device中直接选中LUT6网表,右键后点击Lock Cell Input Pins

三、位置约束

网表在device中的状态分为两种:固定位置和非固定位置,固定位置是指被用户通过设置XDC约束,或者在cell对象中使用了IS_LOC_FIXED/IS_BEL_FIXED三种方式进行了手动布局,三种方式效果相同。非固定位置需要实现工具对网表进行布局,通过该方式布局后,网表会有IS_LOC_FIXED/IS_BEL_FIXED属性

本节主要讲解固定位置的设置,在device界面上,可直接对网表进行位置约束,约束的阶段即可是综合后的网表,也可以是实现后的网表,以跨时钟域的代码为例

- module slow_to_fast(digit1,digit2,rst,clk_f,clk_s,sum);

- input digit1,digit2,rst,clk_f,clk_s;

- output sum;

- wire sum0;

- (*KEEP="TRUE"*) reg ff_f,ff_s1,ff_s2,ff_s3;

- //组合逻辑的信号输出

- assign sum0 = digit1+digit2;

- //时钟域一

- always@(posedge clk_s,negedge rst)

- begin

- if(!rst)

- ff_f<=0;

- else

- ff_f<=sum0;

- end

- //时钟域二

- always@(posedge clk_f,negedge rst)

- begin

- if(!rst)

- begin

- ff_s1<=0;

- ff_s2<=0;

- ff_s3<=0;

- end

- else begin //打两拍处理

- ff_s1<=ff_f;

- ff_s2<=ff_s1;

- ff_s3<=ff_s2;

- end

- end

- assign sum=ff_s3&!ff_s2;

- endmodule

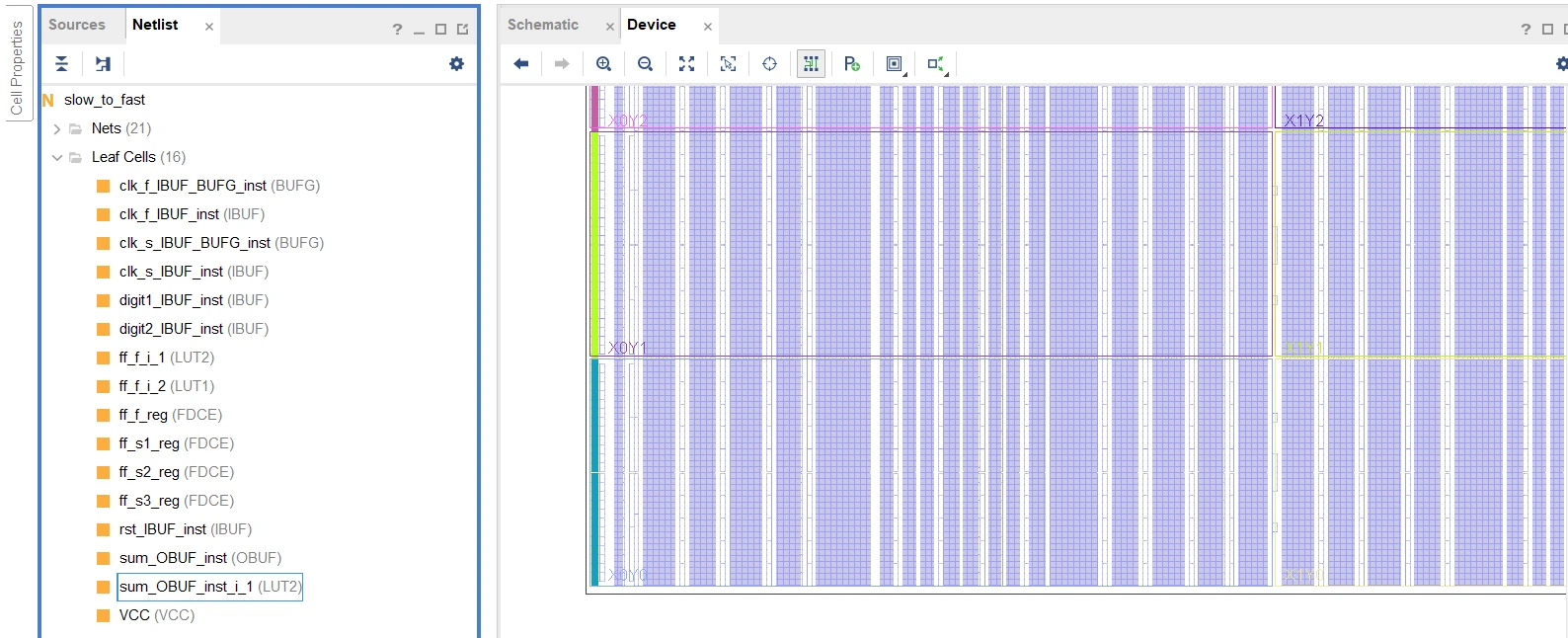

在Netlist窗口的Leaf Cells栏中包含了工程的所有网表,同时在“Window->Device”打开device窗口,

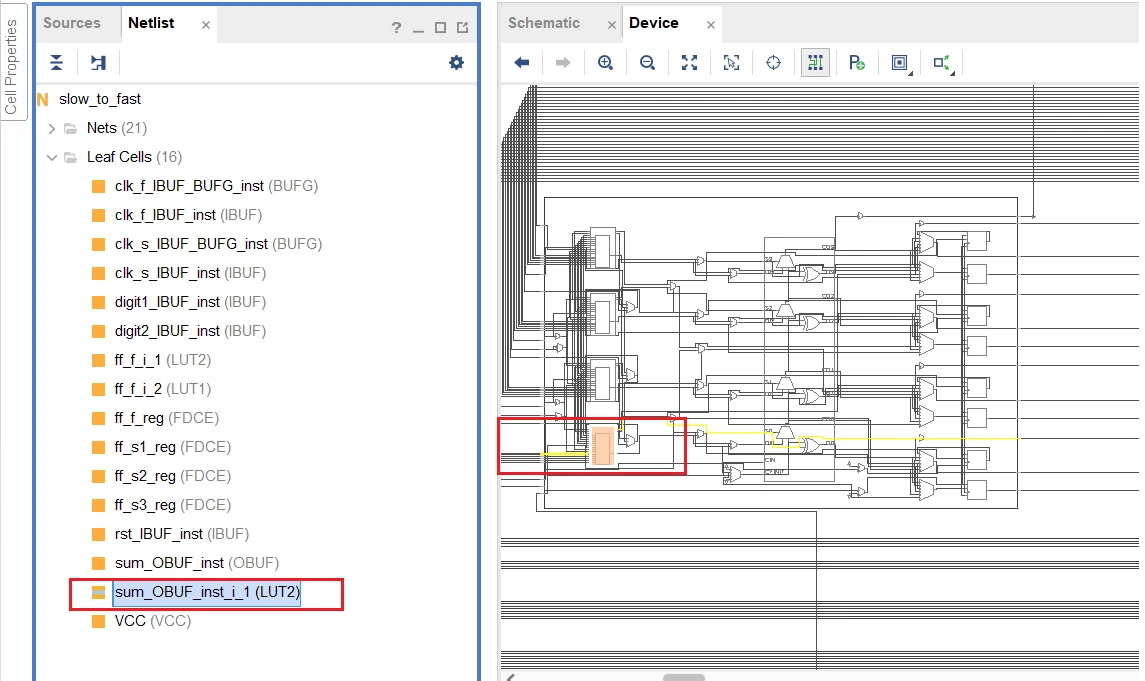

将左侧device的CLB放大,鼠标右键选中左侧的sum_OBUF_inst_i_1(LUT2),将其拖入到右侧的CLB中的LUT位置,保存即设置了该网表的约束,同时device上对应位置有背景颜色标记

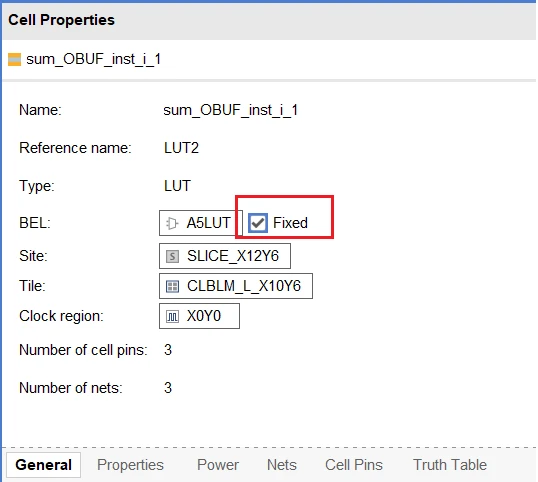

查看网表的cell properties,fixed已被勾选,表示被约束了

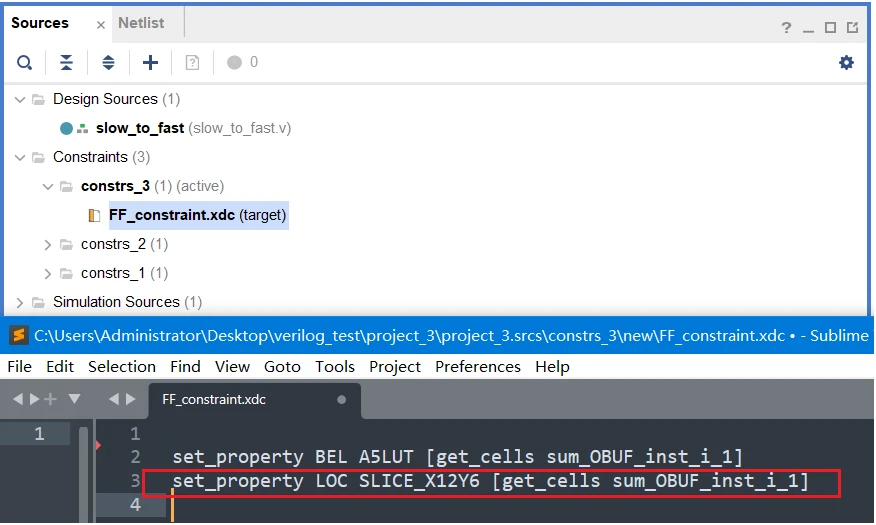

在Constraints打开工程的约束文件,在xdc文件中出现了sum_OBUF_inst_i_1的LOC约束

四、布线约束

布线约束主要是对net的布线资源进行控制,效果和Vivado工具直接布线相同。在综合阶段,要对net进行布线的话,net的driver和load必须先进行约束,否则在device界面不会显示net。布线约束有route和assign routing mode两种方式。

4.1 route

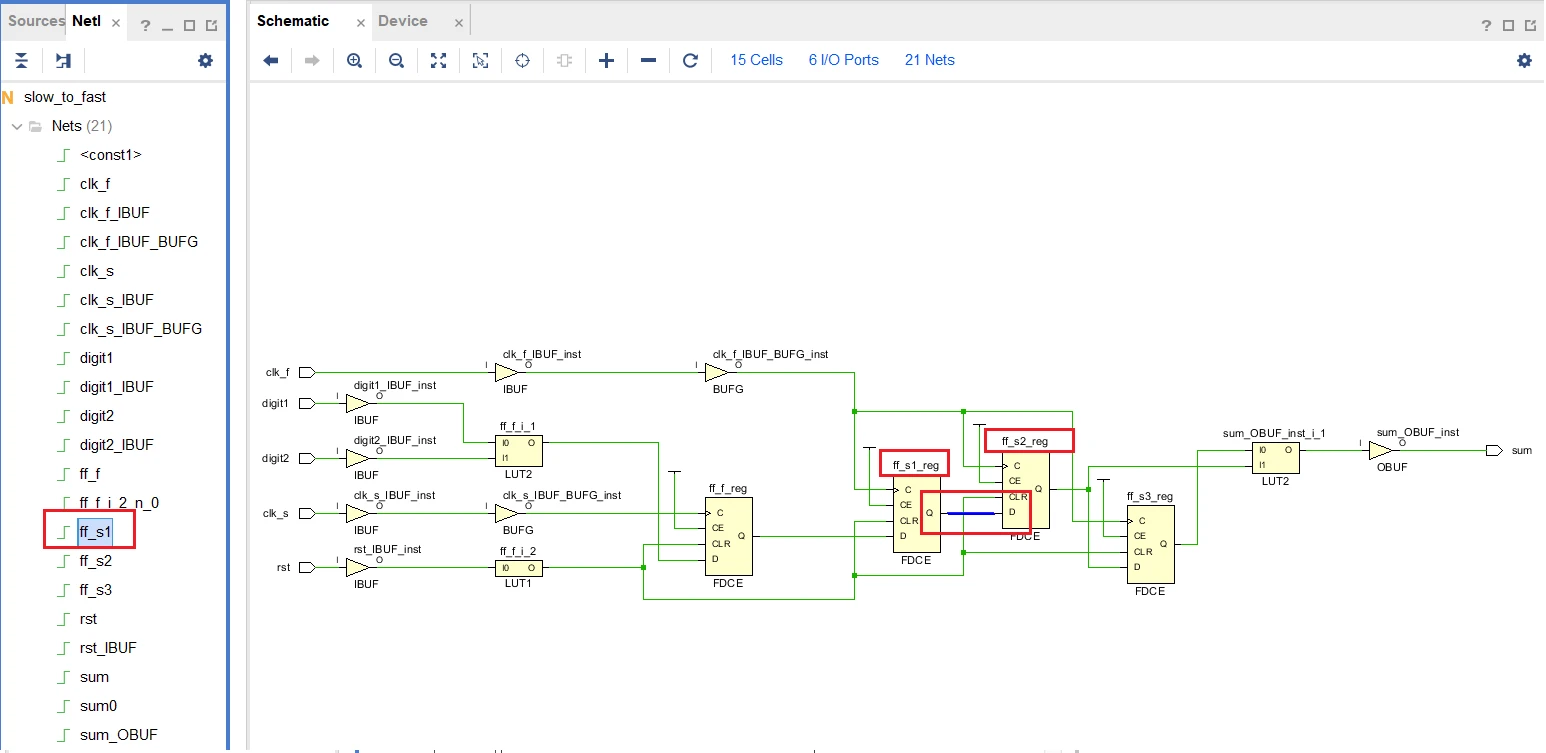

仍旧以2.3节的设计为例,综合后的网表图如下,对ff_s1进行布线约束,对应的driver和load为ff_s1_reg,ff_s2_reg。

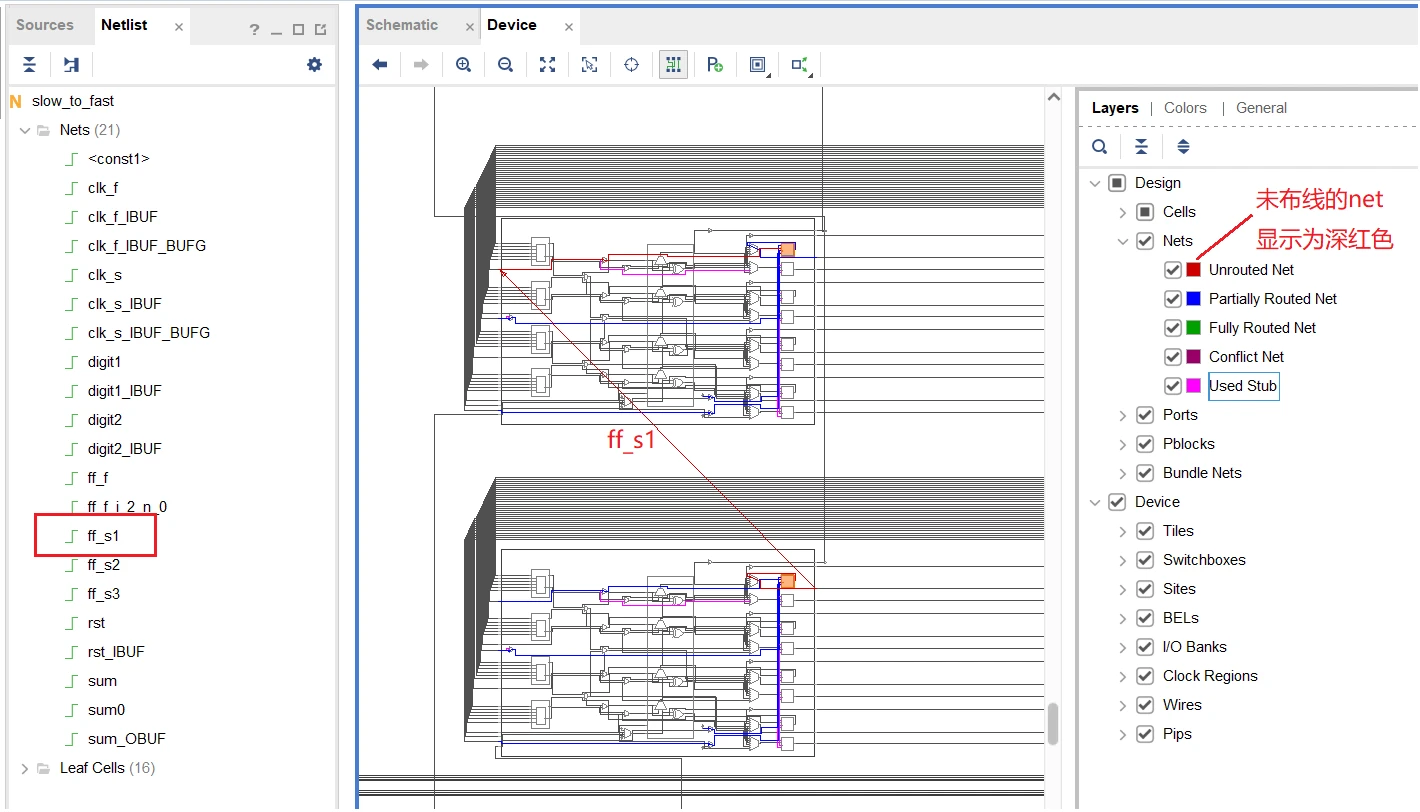

在device中对ff_s1_reg和ff_s2_reg进行位置约束后,在右侧的layers->nets中可知无布线约束的net为unrouted net,显示深红色,ff_s1在device中为图中的斜线

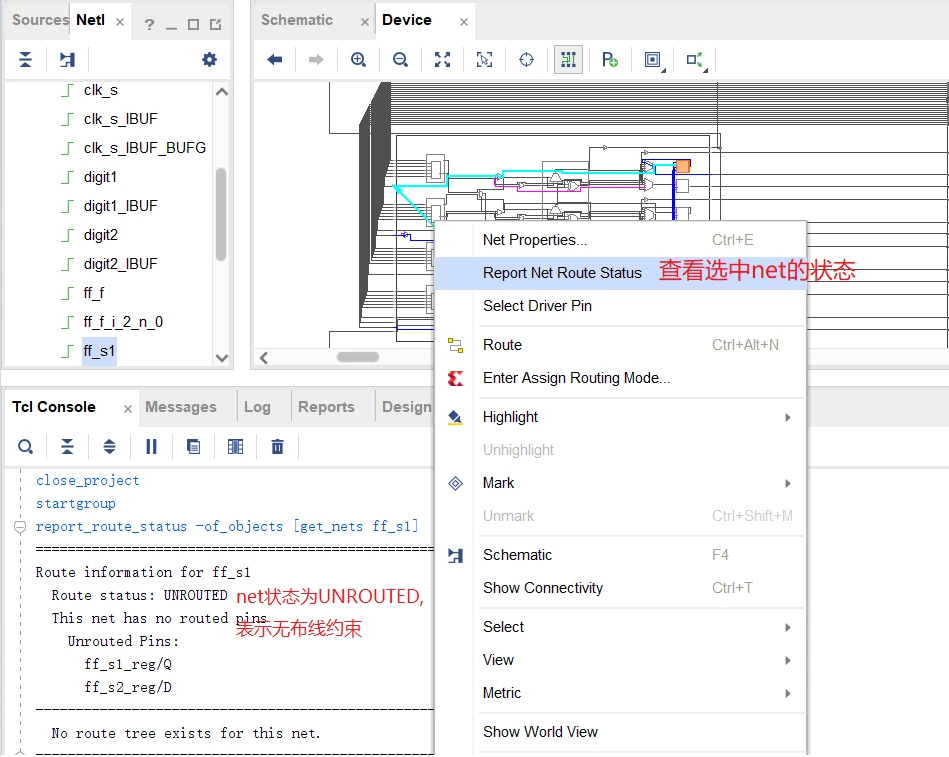

也可选中net执行Report Net Route Status

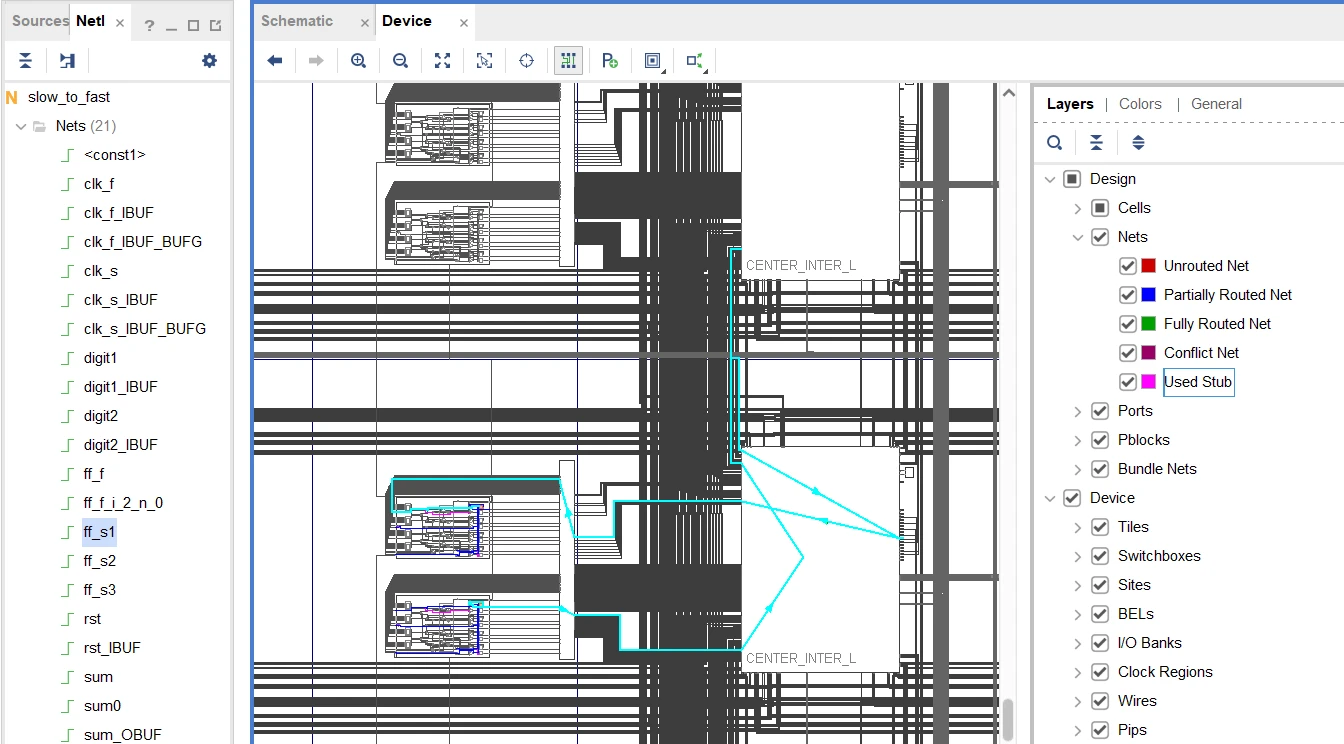

选中net,右键选择“Route”,进行布线约束,原先的ff_s1布线约束后经过了一些switchbox

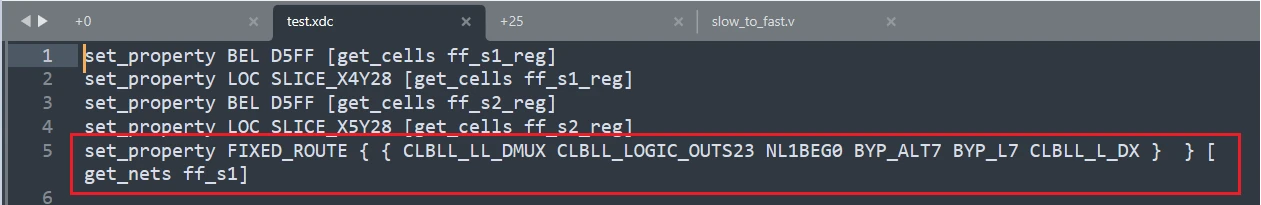

选中该net再执行fix routing将约束固定,保存修改,查看xdc约束内容,包含了FIXED_ROUTE属性的约束,即完成了布线约束

4.2 assign routing mode

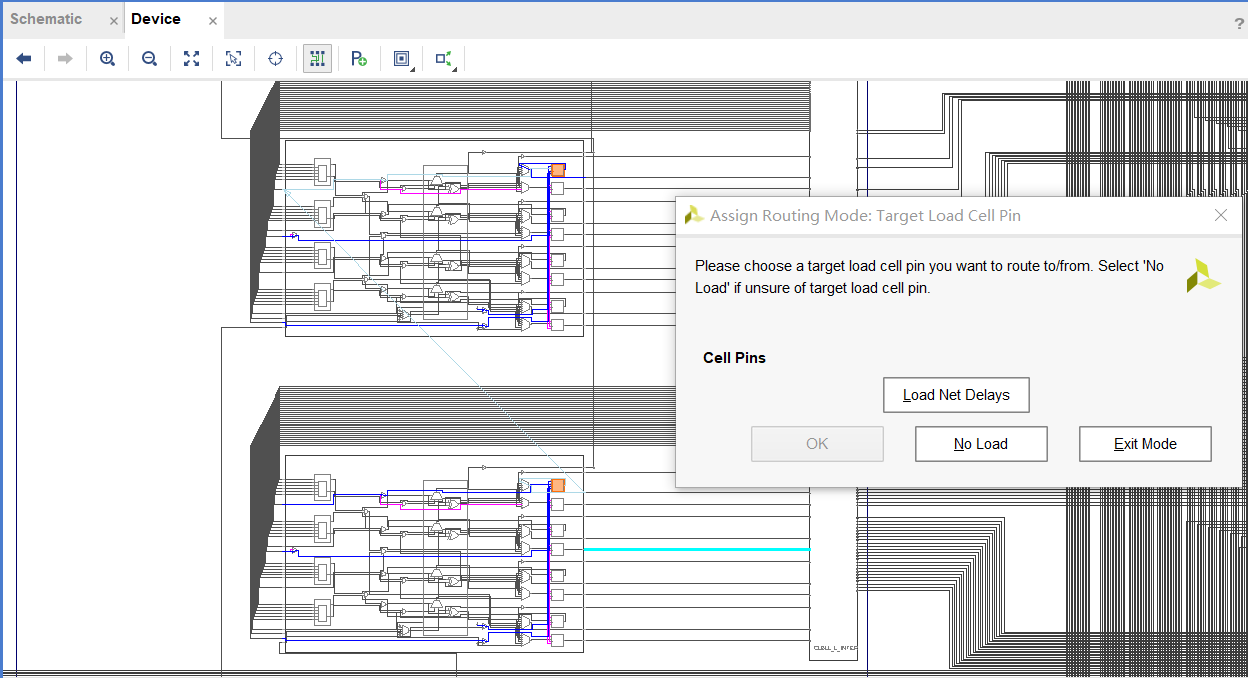

assign routing mode模式布线约束操作与route类似,选中要布线约束的net,右键后选择Assign Routing Mode进入设置界面

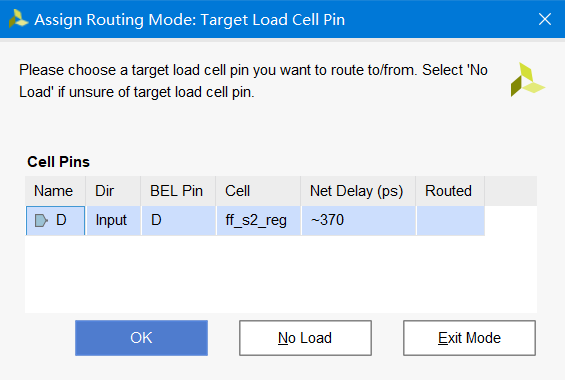

选择load net delay进入设置load界面,Cell Pins中会显示该net所连接的load,此处只有一个,未选择时“OK”图标

点击第一行,此时“OK”高亮,点击"OK",

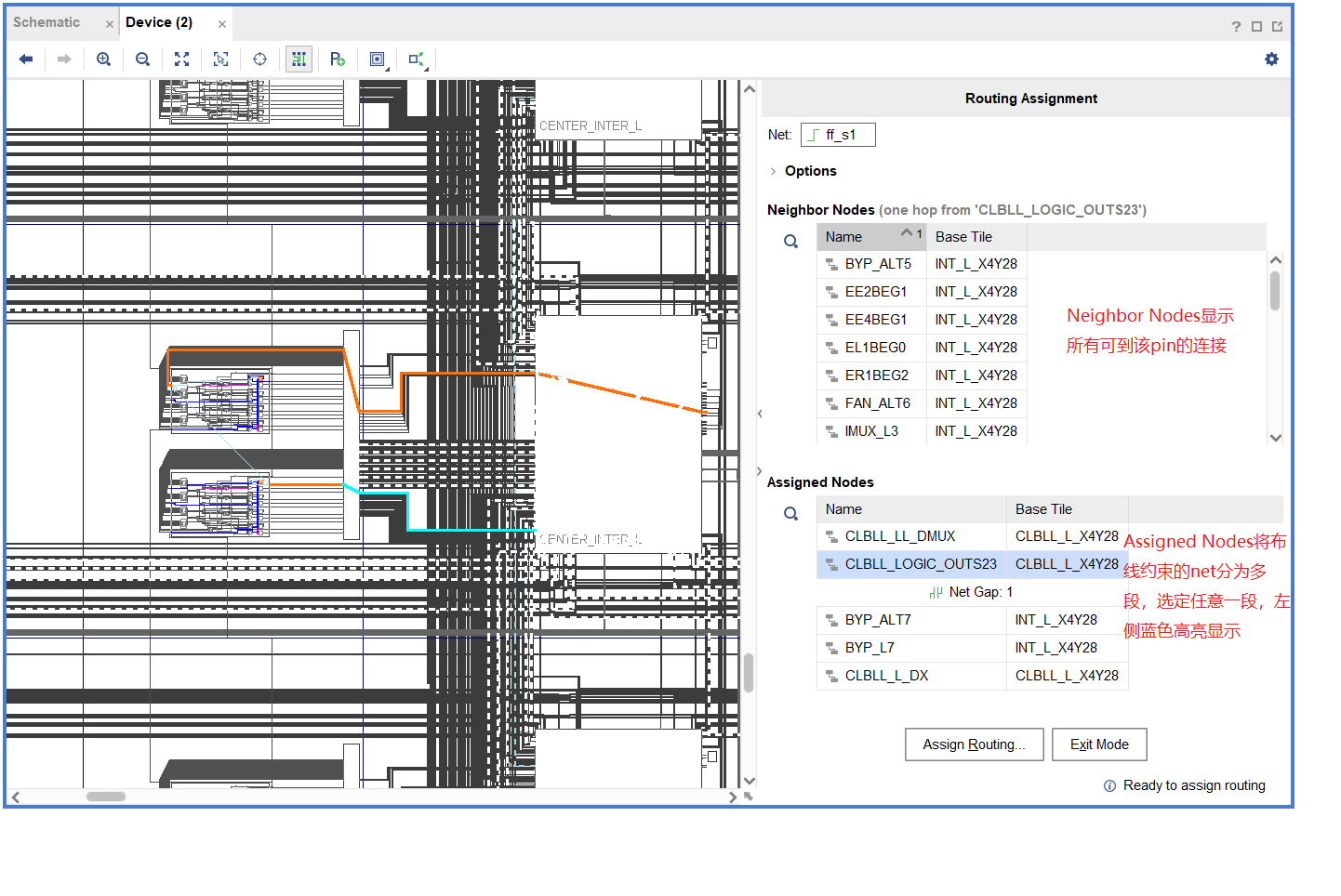

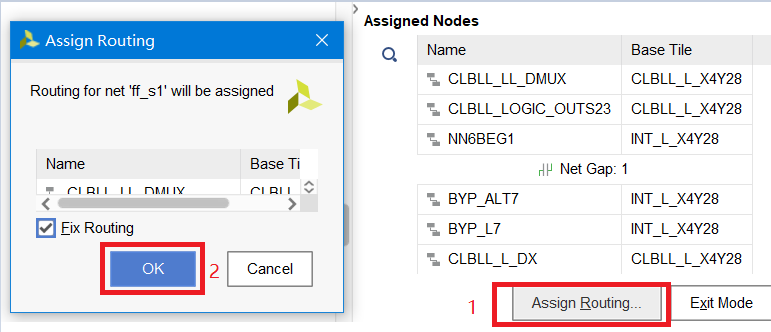

进入Routing Assignment界面,下图右侧中,Assgined Nodes显示的是将布线约束的net分为了多个Net Gap,通俗理解即分为多段,在该栏中任选一行,左侧Device中对应蓝色高亮显示该Net。

在Neighbor Nodes选中任意一个nodes后,Neighbor Nodes中会对应显示该net的node在Base Tile中的其他可连接的nodes。

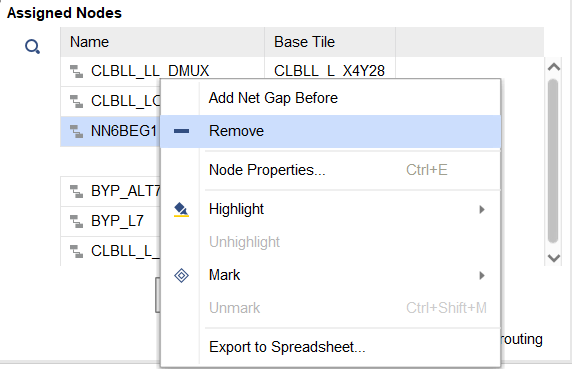

在Aaaigned Nodes中也可以对任意一个Nodes执行删除,或在该Nodes前后添加Net Gap

设置Assigned nodes后,点击下方的“Assign Routing”图标,弹出左侧的Assign Routing窗口,点击“OK”进行Fix Routing,最后ctrl+s保存约束

XDC约束文件中新增ff_s1的FIXED_ROUTE约束,对应内容展示了约束net所经过的路径

五、参考

官方用户手册《ug903-vivado-using-constraints》