热门标签

热门文章

- 1Similarities:精准相似度计算与语义匹配搜索工具包,多维度实现多种算法,覆盖文本、图像等领域,支持文搜、图搜文、图搜图匹配搜索_similarities库

- 2麒麟kylinOS 2303制作自定义免交互安装镜像_kylin镜像

- 3云计算课堂笔记——参考模型_云计算参考模型有哪些

- 42024 Python3.10 系统入门+进阶(一):Python编程基础_python进阶

- 5STM32——TIMER(定时器)篇_stm32定时器

- 6flutter 极光推送华为厂商通道推送_极光推送 华为

- 7一文搞懂SPI通信协议

- 8idea2021.2 就是不能识别application-dev.yml 不将文字进行高亮_idea yam没有高亮

- 9开源AI云测试平台,Hydra Lab

- 10unordered_set和unordered_map模拟实现

当前位置: article > 正文

详解Xilinx FPGA高速串行收发器GTX/GTP(3)--GTX的时钟架构

作者:寸_铁 | 2024-08-06 06:10:05

赞

踩

详解Xilinx FPGA高速串行收发器GTX/GTP(3)--GTX的时钟架构

目录

2.1、单个外部参考时钟驱动单个QUAD中的多个transceiver

2.2、单个外部参考时钟驱动多个QUAD中的多个transceiver

2.3、同一个Quad中,多个GTX Transceiver使用多个参考时钟

2.4、不同Quad中,多个GTX Transceiver 使用多个参考时钟

文章总目录点这里:《FPGA接口与协议》专栏的说明与导航

1、参考时钟

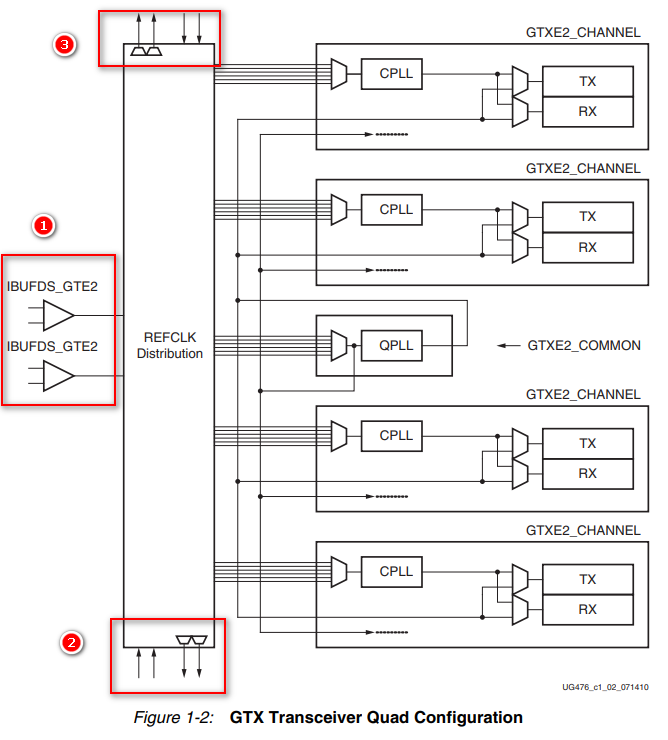

GTX的时钟架构如下:

对于QPLL来说,它的时钟来源有3个:

-

外部差分差分时钟,通过IBUFDS_GTE2原语后变成单端时钟,然后给到QPLL。这种时钟有两个,分别叫做GTREFCLK0和GTREFCLK1

-

来自北边(GT Quad的排布是南北向排布的)的时钟,这个时钟是北边的GT Quad的来自外部的时钟。

-

来自南边(GT Quad的排布是南北向排布的)的时钟,这个时钟是南边的GT Quad的来自外部的时钟。

GTXE2_COMMON原语实际上就是对QPLL的再

推荐阅读

相关标签