热门标签

热门文章

- 1深入理解MySQL:拼接字符串、查询、删除表和创建索引的关键命令

- 2总结 | 常用文本特征选择

- 3【MATLAB源码-第22期】基于matlab的手动实现的(未调用内置函数)CRC循环码编码译码仿真。

- 4Win11查看电脑磁盘分区格式的方法教学_怎样查看磁盘格式

- 5在mmsegmentation框架上实现基于U-net的眼底血管图像分割示例_mmsegmentation unet

- 6使用 python 实现汉字转拼音_python 汉字转拼音 加音标

- 7openlayers 入门教程(六):controls 篇

- 8go 安装

- 9机器学习项目实战识别mnist数据集识别图片数字_采用机器学习或深度学习算法对mnist数字图片数据集进行训练并尽可能提高识别精度

- 10【Python Django Web项目】利用 Python+Django+Pycharm+MySQL 搭建一个自己的Web网站项目的步骤(详细图文)下集_python manage.py makemigrations oatbapp no install

当前位置: article > 正文

基于FPGA的时间数字转换(TDC)设计(三:多相位验证)_基于fpga的时间数字转换器(tdc)的设计与验证

作者:小丑西瓜9 | 2024-04-09 08:43:05

赞

踩

基于fpga的时间数字转换器(tdc)的设计与验证

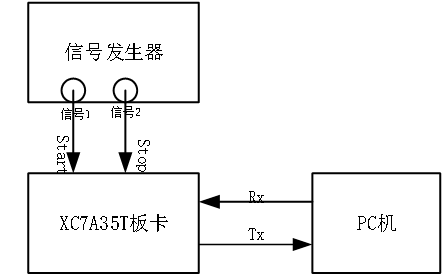

1.多相位TDC计时测试

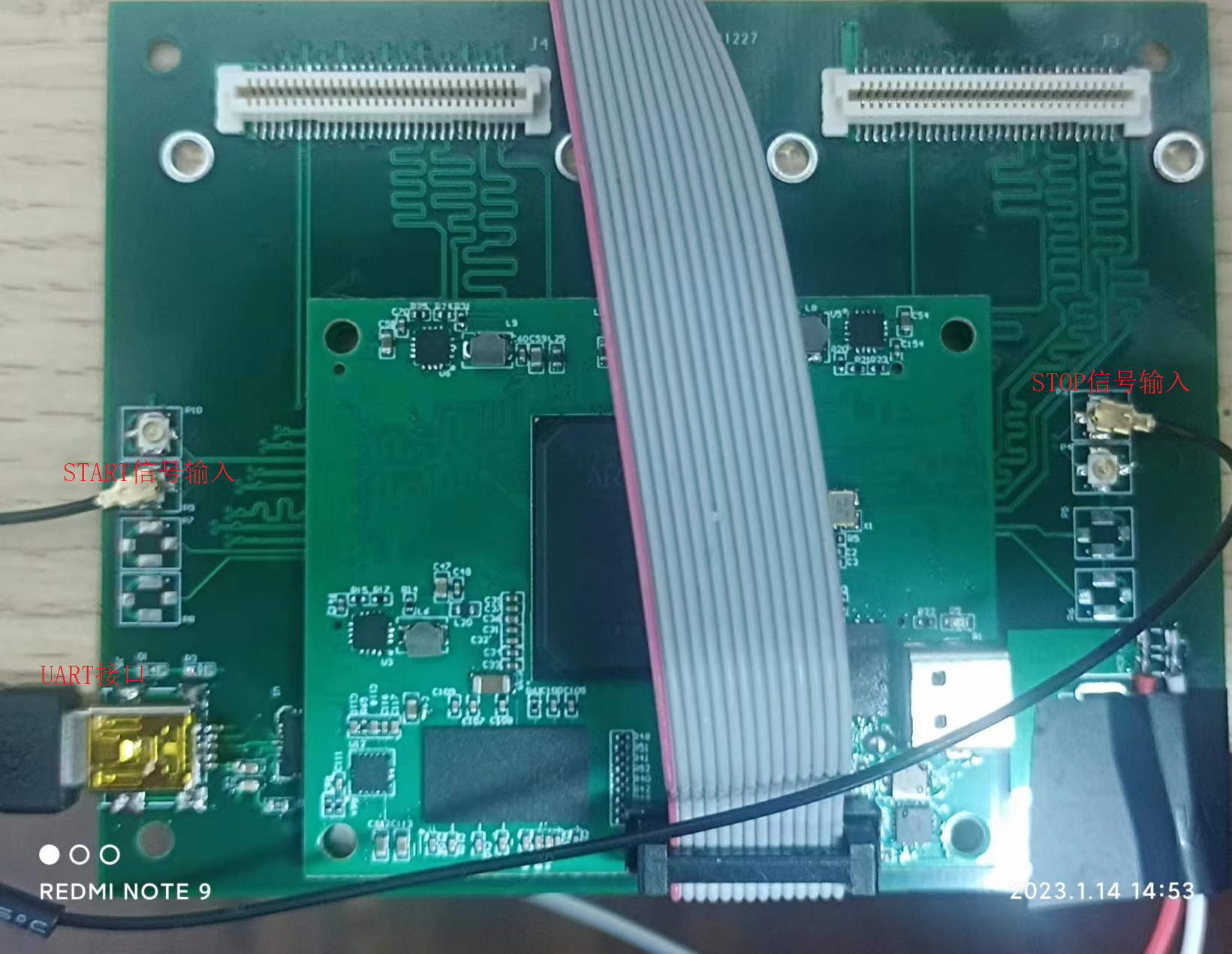

以下为多相位TDC计时的测试。图1为多相位TDC计时的测试框图,利用信号发生器,产生两路同相位、具有固定延时的脉冲信号,一路作为Start信号,另外一路作为Stop信号。由于分辨率为312.5ps,因此以312.5ps为步进,对Stop信号进行延时,扫描一个周期,通过UART接口传输给上位机软件,通过Matlab进行分析。图2为整个硬件实物图,由XC7A35T核心板和底板组成,输入的两路信号Start、Stop通过IPEX接口,连接至FPGA IO口。FPGA板卡采用上海卫红实业公司生产的XC7A35T核心板,表1为板卡详细参数。

图1 多相位TDC计时测试框图

图2 XC7A35T核心板+底板实物图

表1:XC7A35T核心板详细参数

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小丑西瓜9/article/detail/391555

推荐阅读

相关标签