- 1面试经验|拿了8家大厂SSP offer_sspoffer

- 2scrapy-redis_scrapy-redis配置

- 3【论文阅读及代码实现】BiFormer: 具有双水平路由注意的视觉变压器

- 4如何评价cisp-pte证书?_cise-pte

- 5linux mips汇编指令集,MIPS汇编与指令

- 6springboot3使用自定义注解+Jackson优雅实现接口数据脱敏_springboot3 jackson

- 7PU学习相关知识

- 8读英语计算机书籍读后感,读英语小说的读后感(精选14篇)

- 9uni-app的开发环境_uniapp安装依赖

- 10【文章系列解读】AI绘图必读模型:Derambooth和Textual Inversion

AD936x Evaluation Software配置流程/AD9361配置寄存器/AD9361配置流程/zynq配置ad9361/AD9361手把手教程/AD936x教程/纯逻辑控制AD936x

赞

踩

因最近公司需要,借此机会和大家一起学习AD9361

制作不易,记得三连哦,给我动力,持续更新!

工程文件下载:纯硬件SPI配置AD9361 提取码:g9jy

----------------------------------------------------------------------------------------

因为ADI官方,只提供了利用软件(SDK)和硬件平台(vivado)去配置AD936x,但是在一些工程中,这种方法很难去应用到实际的项目中,所以给大家介绍一个纯硬件配置AD936x的一个详细教程。因为是手把手教程,所以有些大佬不要嫌麻烦。同时后期会更新工程上的项目设计。废话不多说了,直接进入主题!和我一起学习神秘而又神奇AD936x吧!少年!

我用的是zedboard+ad9361,和我的硬件一样的伙伴,可以完全按照我的步骤进行,FPGA芯片为zynq7020的应该也可以。其余的根据自身芯片要求略微修改即可

一、寄存器配置软件

ADI官方提供了一个配置AD936x寄存器的一个软件,这个软件可以非常方便的配置AD936x的一系列参数,并生成一个可以供vivado上面去调用的脚本文件,从而利用SPI去进行AD936x的配置和设计。

这里我免费把软件分享给大家:我安装的版本为AD936X Evaluation Software 2.1.4版本,安装我就不做多讲解了,会安装企鹅的应该都会安装这个软件,一路点下一步即可完成安装。

AD936X Evaluation Software软件安装包: AD936x配置软件, 提取码:5o25 。

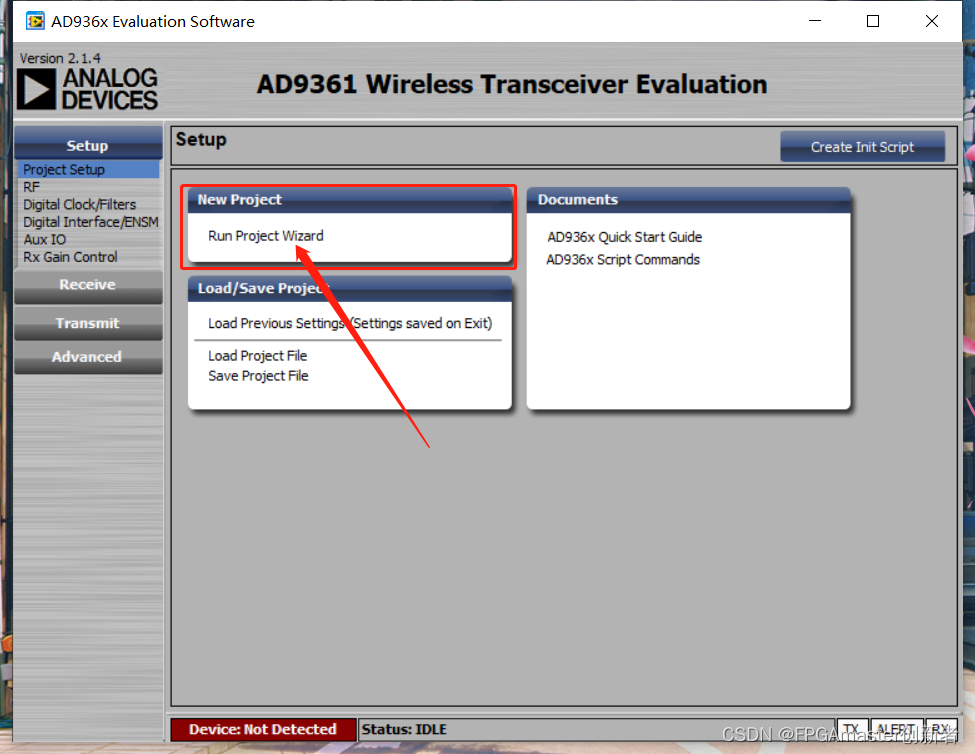

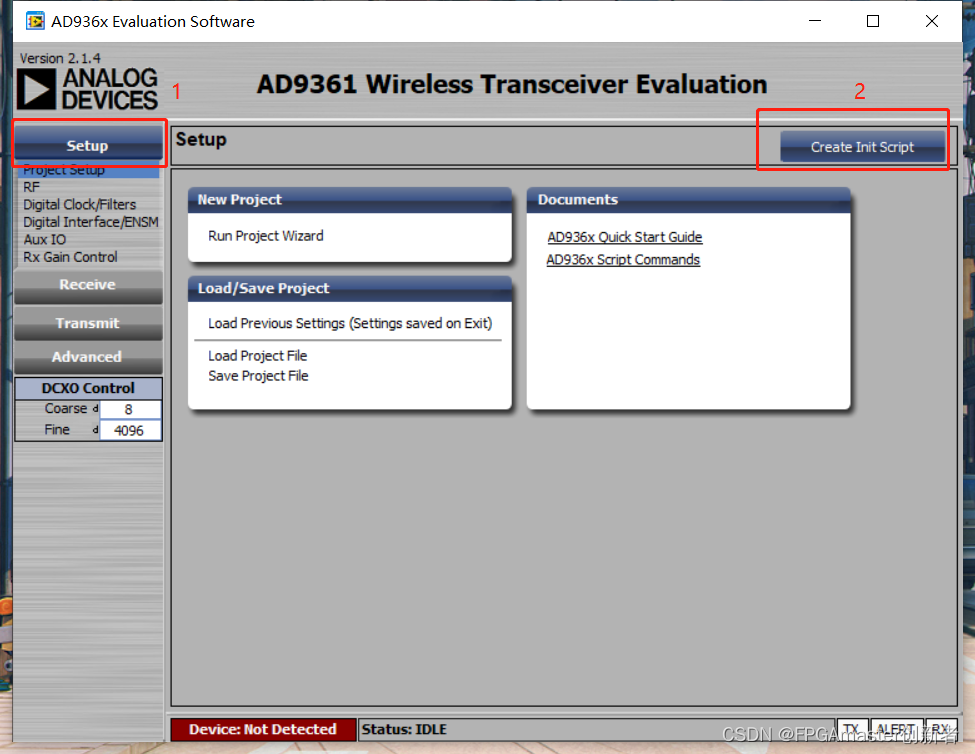

安装完成后,打开软件,界面如下:

二、AD936x寄存器配置参数

2.1 创建新工程

首先打开软件,点击Run Project wizard,创建一个新的工程

界面介绍:

| New Project | 新建工程,用于建立一个新的工程 |

| Load/Save Project | 加载之前保存的工程/保存当前工程 |

| Documents | 软件介绍文档 |

| Create Init Script | 创建初始化脚本文件(配置AD936x的所有SPI寄存器) |

2.2 用户参数

界面配置介绍:

| 名称 | 介绍 | 我的配置 |

| Device | 器件型号 | AD9361 |

| Device Rev | 版本号 | 保持默认 |

| Project Profile | 配置文件(自定义、模板) | 自定义 |

| Rx Channel | 接收通道(单收,双收) | RX通道1(单) |

| Tx Channel | 发送通道(单发,双发) | TX通道1(单) |

| Rx Input Structure | 接收信号方式(差分、单端) | 最佳噪声系数:差分 |

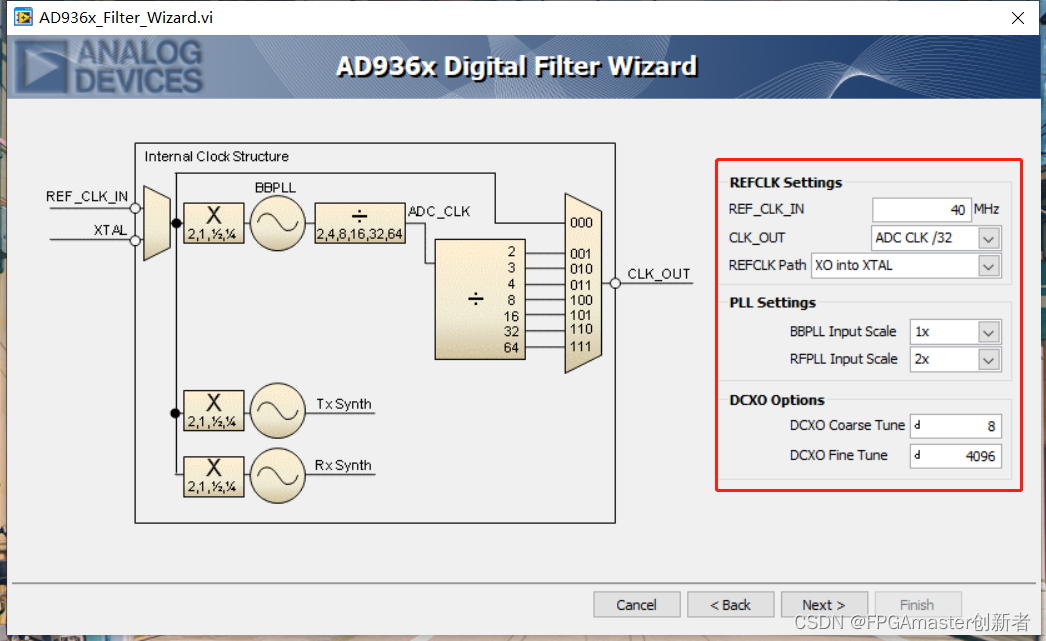

2.3 时钟设置

界面配置介绍:

| 名称 | 介绍 | 我的配置 |

| REF_CLK_IN | ad936x的工作时钟 | 40M |

| CLK_OUT | ad936x内部配置的时钟输出(根据项目需要自行设置) | ADC_CLK/32 |

| REFCLK Path | 参考时钟输入路径(根据硬件电路板进行设计) | XO into XTAL |

| BBPLL Input Scale | 相对于输入参考频率源的分频或者倍频 | 1x |

| RFPLL Input Scale | 相对于输入参考频率源的分频或者倍频 | 2x |

| DCXO Coarse Tune | DCXO粗调节数值,具体查看相应的寄存器 | 保持默认 |

| DCXO Fine Tune | DCXO精调节数值,具体查看相应的寄存器 | 保持默认 |

由于BBPLL 参考时钟频率最好在35-70MHz中选大的值,RF PLL 参考时钟频率最好在10-80MHz中选大的值,所以BBPLL和RFPLL 分别为1x和2x。

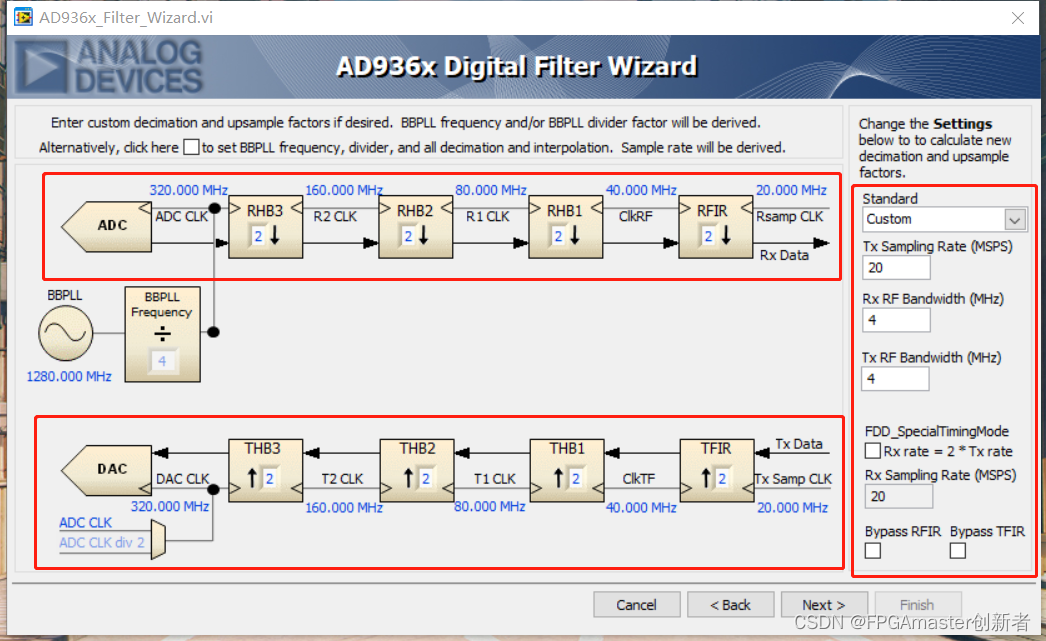

2.4 滤波器设置

界面配置介绍:

| 名称 | 介绍 | 我的配置 |

| Standard | 滤波器标准(自定义、ADI官方模板) | 自定义 |

| Tx Sampling Rate(MSPS) | 发送采样率,根据项目要求而定 | 20 |

| Rx RF Bandwidth (MHZ) | 接收带宽,根据项目要求而定 | 4 |

| Tx RF Bandwidth (MHZ) | 发送带宽,根据项目要求而定 | 4 |

| FDD_SpecialTimingMode | 非标准化的时序模式 | 默认不勾选 |

| Rx Sampling Rate(MSPS) | 接收采样率,根据项目要求而定 | 保持默认20 |

| Bypass RFIR | 绕过射频滤波器 | 默认不勾选 |

| Bypass TFIR | 绕过时域滤波器 | 默认不勾选 |

| 名称 | 介绍 | 我的配置 |

| RFIR | 接收FIR数字滤波器,最小16拍最大128拍(必须为16倍数),抽取因子1、2和4,可编程增益-12dB、-6dB、0dB与6dB | 2 |

| RHB1 | 固定系数半带抽取数字滤波器,抽取因子1、2,固定系数为[-8, 0, 42, 0, -147, 0, 619, 1013, 619, 0, -147, 0, 42, 0, -8] | 2 |

| RHB2 | 固定系数半带抽取数字滤波器,抽取因子1、2,固定系数为[-9, 0, 73, 128, 73, 0, -9] | 2 |

| RHB3 | 固定系数抽取数字滤波器,抽取因子1、2、3,HB3固定系数为[1, 4, 6, 4, 1] | 2 |

| TFIR | 接收FIR数字滤波器,最小16拍最大128拍(必须为16倍数),插入因子1、2和4,可编程增益-6dB、0dB | 2 |

| THB1 | 固定系数半带抽取数字滤波器,抽取因子1、2,固定系数为[-53, 0, 313, 0, -1155, 0, 4989, 8192, 4989, 0, -1155, 0, 313, 0, -53] | 2 |

| THB2 | 固定系数半带抽取数字滤波器,抽取因子1、2,固定系数为[-9, 0, 73, 128, 73, 0, -9] | 2 |

| THB3 | 固定系数抽取数字滤波器,抽取因子1、2、3,HB3固定系数为[1, 2, 1] | 2 |

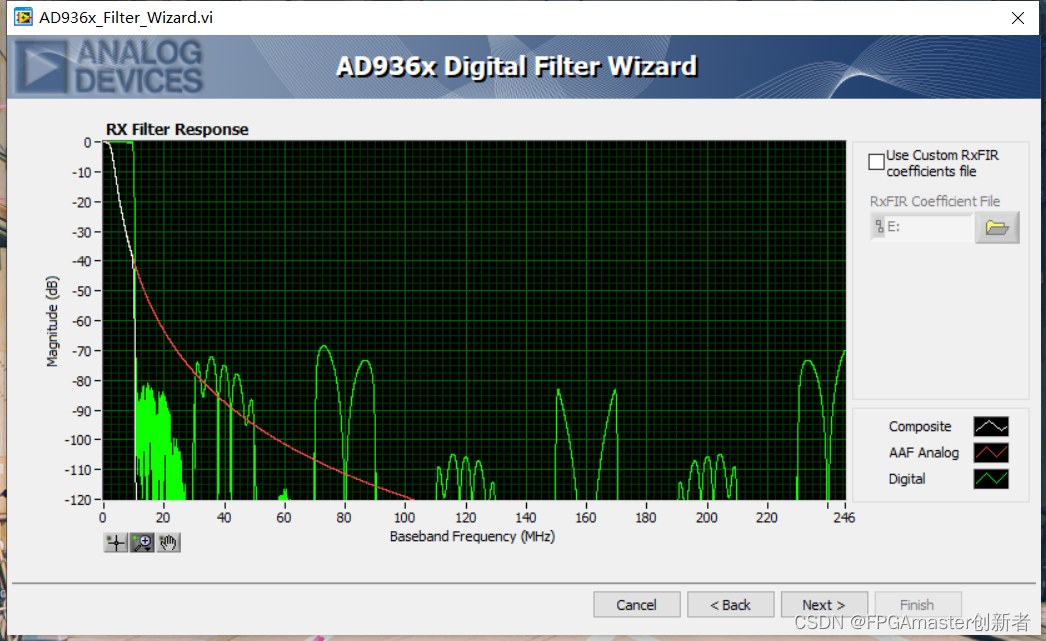

2.5 接收滤波器配置

在这里可以使用默认的,也可以使用自定义的(matlab中产生,后续会讲),本次先使用默认的接收滤波器。

绿色:FIR数字滤波器响应,是软件依据之前设定的采样速率Rx/Tx Sampling Rate自动生成的全通滤波器

红色:模拟防混淆滤波器响应,其3dB角频率和之前设置的带宽RF Bandwidth有关

白色:模拟滤波器和数字滤波器级联后的响应曲线

2.6 发送滤波器设置

蓝色:发射数字滤波器响应曲线

2.7 数字接口配置

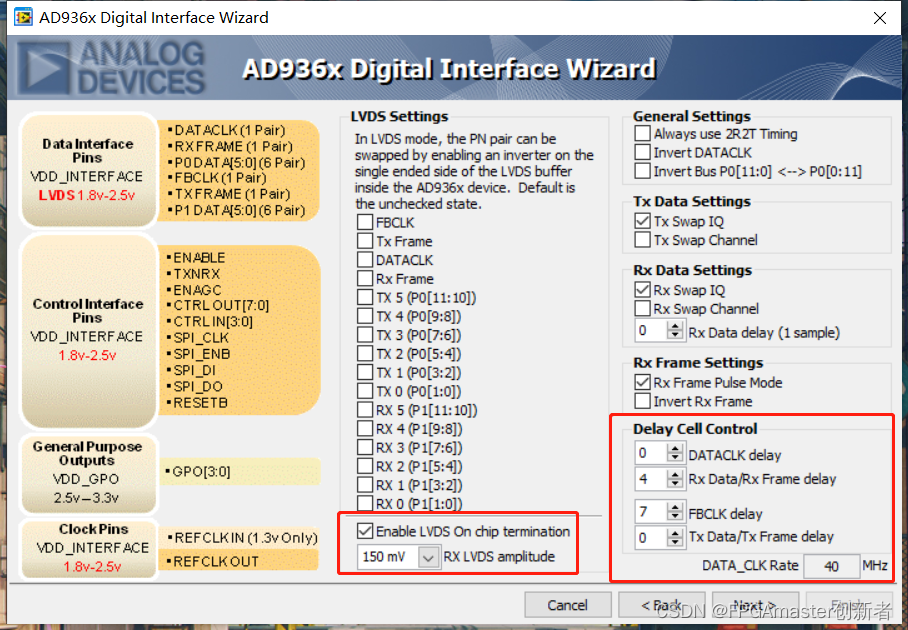

根据前面的配置,所以选择LVDS,其余的全部不用设置,COMS模式后期会具体出一个教程,本次先选择LVDS。

左边的数据传输图,也是非常有用的一个图,建议大家保存起来,后期对着图片看代码,对代码理解有很大帮助。

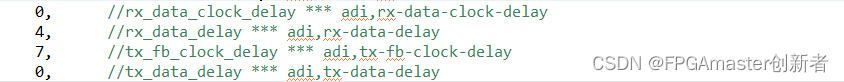

2.8 数据接口详细配置

这里最重要是设置:

RX LVDS amplitude:150mv,根据开发板选择(我用的是zedboard,官方推荐150mv)

Delay Cell Control:(非常重要)

根据ADI官方要求,zedboard开发板设置如下:

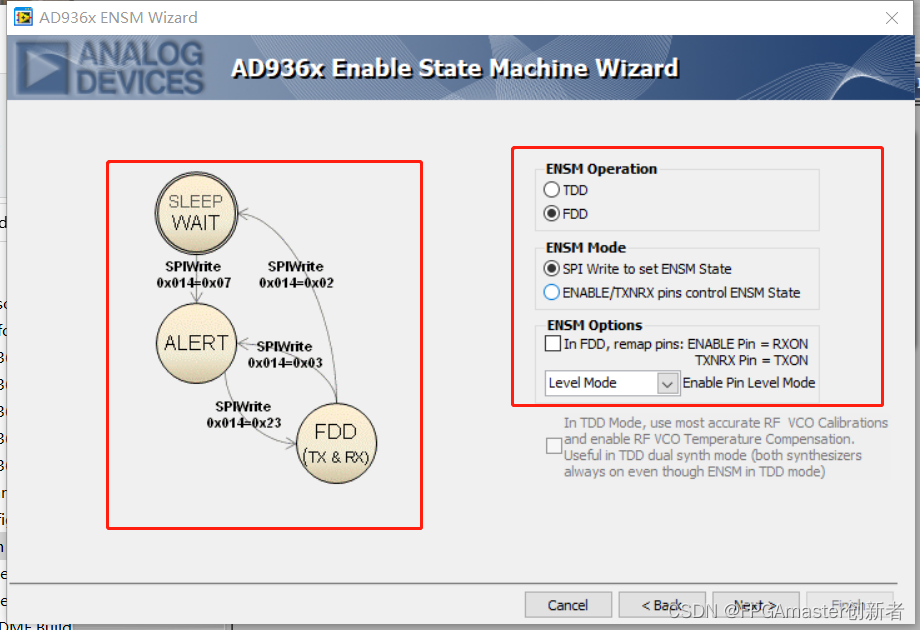

2.9 使能状态机

AD936x使能状态机界面主要包含两个组成部分,分别是AD936x状态机变换框图与相应的状态机配置参数,状态机变换框图详细介绍了从一个状态变换到另一个状态需要进行的操作过程,用于可以根据该信息进行状态的变换控制。

界面配置介绍:

| 名称 | 介绍 | 我的配置 |

| ENSM Operation | 频分双工FDD与时分双工TDD状态变换不一样,用户需要根据设计要求进行选择 | FDD |

| ENSM Mode | ENSM的控制方法有两种,一种是通过SPI进行状态的切换,一种是通过ENABLE/TXNRX引脚控制状态的转换。 | SPI |

| ENSM Options | 当选择ENABLE/TXNRX引脚控制状态的转换时,需要设置引脚的触发模式,有电平触发与脉冲触发两种方式。 | 电平触发 |

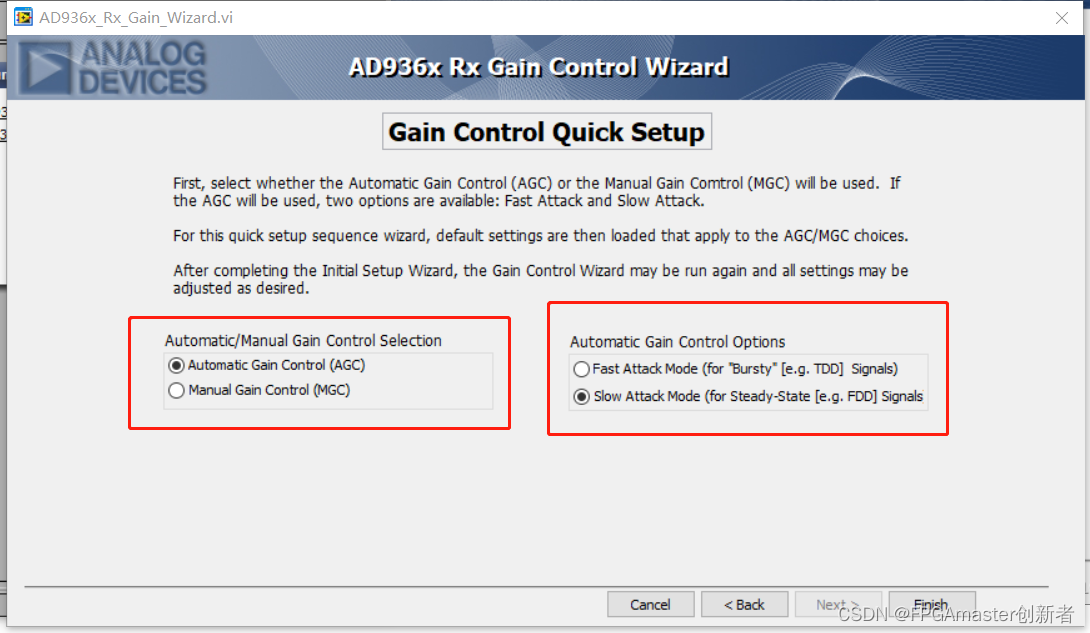

2.10 接收增益控制

接收增益主要分为两种:AGC模式(自动增益)与MGC模式(手动增益),AGC模式又分为快速attack模式(TDD模式下使用)与慢速attack模式(FDD模式下使用),根据前面的设置本次设计接收增益选择自动增益慢速attack模式。

接收增益主要分为两种:AGC模式(自动增益)与MGC模式(手动增益),AGC模式又分为快速attack模式(TDD模式下使用)与慢速attack模式(FDD模式下使用),根据前面的设置本次设计接收增益选择自动增益慢速attack模式。

然后点击finish。

2.11 设置接收频率

本次设计设计接收频率为2.4G,根据自己的设计可以进行更改。

本次设计设计接收频率为2.4G,根据自己的设计可以进行更改。

界面配置介绍:

| 名称 | 介绍 | 我的配置 |

| RX Frequency | 设置为输入参考时钟的整数倍,这一点至关重要,否则会引起频率跳变过程中相位随机发生变化的情况,就不能进行接收通道的校准,影响整个系统。 | 2.4G |

| Gain Index | 增益值根据用户的需求进行设置 | 76 |

2.12 设置发送频率

本次设计设计发射频率为2.4G,根据自己的设计可以进行更改。

本次设计设计发射频率为2.4G,根据自己的设计可以进行更改。

界面配置介绍:

| 名称 | 介绍 | 我的配置 |

| TX Frequency | 设置为输入参考时钟的整数倍,这一点至关重要,否则会引起频率跳变过程中相位随机发生变化的情况,就不能进行接收通道的校准,影响整个系统。 | 2.4G |

| TX1/2 Attenuation | 衰减值根据用户的需求进行设置 | 10 |

2.13 生成脚本文件

Low Level Scripting(适用于SPI读写),而High Level Scripting(使用于ADI Script function)。本次设计需要用SPI进行配置AD936x,所以选择Low Level Scripting。

Low Level Scripting(适用于SPI读写),而High Level Scripting(使用于ADI Script function)。本次设计需要用SPI进行配置AD936x,所以选择Low Level Scripting。

下期讲解如何把导出的脚本文件,转换为Verilog代码,以及如何用SPI进行读写的,感兴趣的伙伴可以继续阅读。