- 1mac 安装redis_mac redis 下载

- 2雷达回波模拟仿真(三):杂波(以LFM为例)matlab_基于地形的杂波仿真建模

- 3Linux|Awk 变量、数字表达式和赋值运算符

- 4我30岁,为高薪转行当程序员,第一份工作月薪7500_30岁成为一名程序员

- 5支持向量机——pytorch与paddle实现支持向量机

- 6ios手游退款有风险吗?_梦幻手游苹果退款惩罚

- 7python爬虫豆瓣读书top250+数据清洗+数据库+Java后端开发+Echarts数据可视化(一)_基于爬虫,数据清洗,echars数据可视化的项目

- 8Java全局变量

- 9csdn最详细最牛逼的 阿里最新app自动化测试---自动化测试框架搭建_app自动化测试框架爬数据

- 10启动appium session报错:Neither ANDROID_HOME nor ANDROID_SDK_ROOT environment variable was exported.

SOC FPGA介绍及开发设计流程

赞

踩

目录

一、SoC FPGA简介

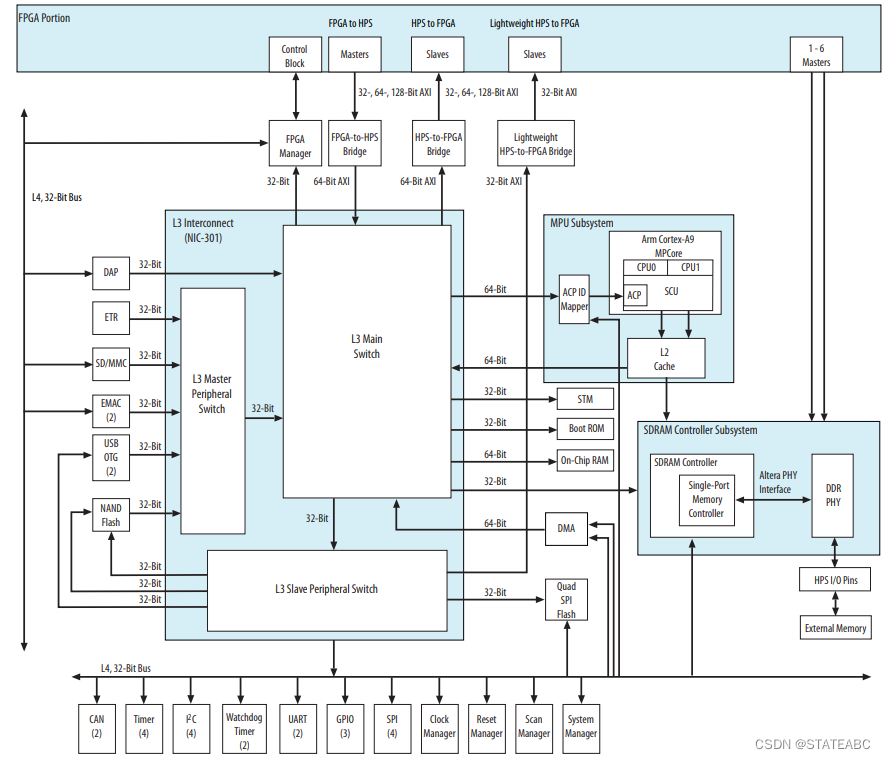

SOC FPGA是在FPGA架构中集成了基于ARM的硬核处理器系统(HPS),包括处理器、外设和存储器控制器。相较于传统的仅有ARM处理器或 FPGA 的嵌入式芯片,SOC FPGA既拥有ARM处理器灵活高效的数据运算和事务处理能力,又拥有FPGA的高速并行数据处理优势。同时,基于两者独特的片上互联结构,在使用时可以将 FPGA 上的通用逻辑资源经过配置,映射为ARM处理器的一个或多个具有特定功能的外设,并通过高达128位位宽的AXI高速总线进行通信以完成控制命令和高速数据的交互。

HPS中的MPU子系统包括了两个Cortex-A9处理器核、二级(L2)高速缓存(Cache)和缓存器子系统、侦测控制单元(SCU)、一致性加速端口(ACP)以及调试功能模块。Cortex-A9处理器核中包括浮点单元(FPU)用于支持浮点运算,可以极大的提升依赖于浮点运算应用系统的性能,如高级控制算法、成像(缩放、三维变换)、快速傅里叶变换以及图像中的滤波等。每个Cortex-A9处理器核都包含一个ARM NEON媒体处理引擎(Media Processing Engine,MEP),该引擎支持多数据的同时运算,而可以加速多媒体等信号处理运算的速度。

HPS其他部分位于MPU子系统之外,处理器通过一组64位的ABMA(Advanced Microcontroller Bus Architecture)高级扩展接口(Advanced eXtensible Interface, AXI)主机访问HPS的其他部分。

SOC FPGA集成芯片的HPS和FPGA能够独立工作,通过高性能ARM AMBA AXI总线连接。FPGA架构中的IP总线能够通过FPGA至HPS互连访问HPS总线从机,HPS总线主机能够通过HPS至FPGA桥接访问FPGA架构中的总线从机,ARMBA AXI接口均可配置为32/64/128位。

二、SoC FPGA开发流程

2.1 硬件开发

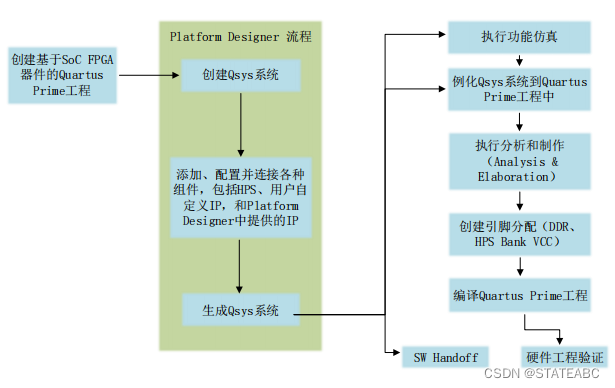

硬件开发使用Quartus Prime和Platfom Designer。

硬件设计工作流程:

(1) 在Platform Designer中添加HPS组件以及各外围器件(如片内存储器、PIO、定时器、UART、片外存储器、DMA 等),并定制和配置它们的功能;分配外设地址及中断号;设定复位地址:;最后生成系统。

(2) 使用Platform Designer生成含HPS的系统后,会得到一个.qsys 后缀的文件,将其集成到整个Quartus Prime工程中。可以在Quartus Prime工程中加入 qsys 系统以外的逻辑。用户可以将HPS高性能处理器和具有强大并行处理能力的FPGA高度整合,以得到最佳的性能。

(3) 使用Quartus Prime选取具体的SOC FPGA器件型号;然后为系统分配引脚,对于 HPS,主要是设置 SDRAM的引脚电平和IO Bank电平。另外还要根据要求进行硬件编译选项或时序约束的设置;最后编译工程,在编译过程中Quartus Prime将对Qsys生成系统的HDL设计文件进行布局布线从HDL源文件综合生成一个适合目标器件的网表,生成FPGA配置文件(.sof)。

(4)使用Quartus Prime编程器和IntelFPGA下载电缆(如 USB Blaster),将配置文件(用户定制的含 HPS 系统的硬件设计)下载到目标板上。当校验完当前硬件设计后,可将新的配置文件下载到目标板上的非易失存储器里(如EPCS器件)。下载完硬件配置文件后,软件开发者就可以将此目标板作为软件开发的初期硬件平台进行软件功能的开发验证了。

2.2 软件开发

软件开发主要使用到两个工具,SOC EDS和Intel FPGA 部门深度定制的DS-5软件。

SOC EDS:类似一个Linux虚拟机,支持 Linux 系统中常用的各种命令如cd、ls、chmod、cat、make,也包含了一些专用的工具,如用于生成dts文件的spocdts工具、用于生成Altera专属的 Preloader头文件用的mkpimage工具,用以烧写U-Boot和 Preloader文件到sd卡中用的alt-boot-disk-util工具等等。使用SOC EDS,可以针对特定的硬件工程生成相应的U-Boot 源码并编译得到 U-Boot镜像文件,也可以实现对Linux 应用程序、内核和驱动的编译。在不安装 Linux 操作系统的情况下,就能完成基于HPS系统的软件开发和调试。

DS-5可以用来编写、编译、调试 SoC 片不含操作系统的裸机程序,Linux 内核和驱动模块,该软件包含以下特性:基于易用的Eclipse编辑器、支持GCC编译器编译和调试Linux应用程序、支持调试Linux内核和驱动模块、支持使用USB Blaster调试ARM处理器、支持FPGA和ARM交叉触发联合调试、支持优化软件的profile特性

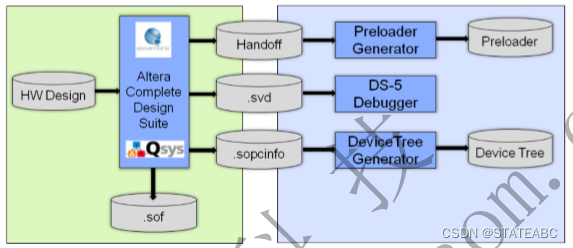

硬件设计经过Quartus编译后会产生三个文件:

Handoff文件夹:包括HPS元件配置信息,例如使能的HPS外设、复用引脚的选择和IOSCR设置、存储器参数设置等;

SVD文件:包括HPS寄存器描述以及FPGA部分的软核IP寄存器描述;

SOPCINFO文件:包括整个系统的描述信息。

Handoff文件夹用于SOC EDS软件的Preloader Generator创建Preloader,Preloader根据Handoff文件夹中的信息配置HPS元件,初始化SDRAM,将下一阶段的引导过程(boot process)加载到SDRAM中并向它传递控制信息。

通过SVD文件可以在DS-5调试器中对HPS外设及FPGA外设寄存器进行检查和修改。

SOPCINFO文件用于设备树产生器(Device Tree Generator)创建Linux内核所需的设备树。设备树是描述硬件到操作系统的标准方式,主要应用于Linux系统中,它制定了开发板硬件和FPGA的配置,使内核启动时回家再相应的驱动程序。

参考文献:

SoC FPGA 设计和开发教程

基于FPGA的嵌入式系统设计—Altera Soc FPGA

Cyclone V Hard Processor System Technical Reference Manual