- 1大脑与反向传播

- 2adb工具下载及安装_adb下载

- 3Flutter零基础入门学习资料集合_mk甄选-2024年flutter零基础极速入门到进阶实战[同步更新中]

- 4消息队列基础篇_消息队列cnds

- 5全国青少年信息素养大赛图形化编程复赛·模拟一卷,含答案解析_图形画编程 竞赛

- 6大数据再出发-06Hadoop(优化&特性&HA)_hadoop的数据压缩和编码技术可以帮助减少存储空间和提高数据传输效率。以下哪个选

- 7了解AIGC:让AI创造内容,改变未来

- 8自然语言处理(NLP)原理、用法、案例、注意事项_nlp如何使用

- 9资深老鸟,自动化测试分层模型与落地总结,“我“该如何提升?_性能测试分层模型是什么

- 10ElasticSearch的Update By Query的坑(使用注意事项及其方案)_updatebyquery的坑

verilog宏功能中dds信号发生器_高效实战及电赛训练(6)- 如何快速制作DDS信号源?...

赞

踩

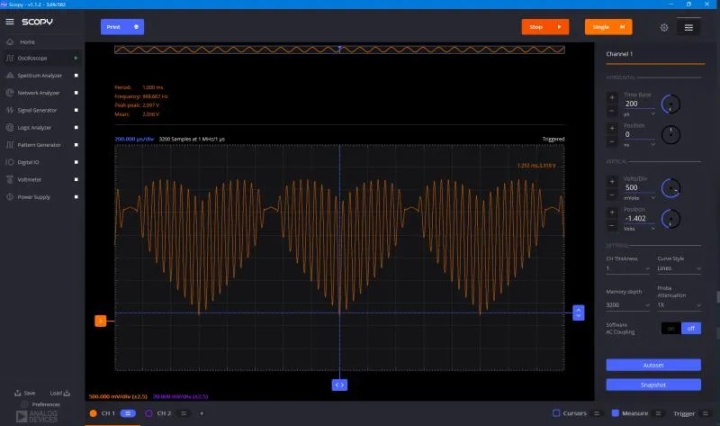

在每届的全国大学生电子设计竞赛中,DDS作为信号源、以及通信里面本振、波形合成的基本方式,几乎成了必考的技能,虽然考察的角度不同,但核心都是一个 - 通过数字的方式得到你需要的某种频率的某种幅度的某种波形。

在测试测量领域有另一个概念 - AWG(任意波形发生器)是跟DDS紧密相关的,波形发生器未必一定采用DDS的方式,但“任意”波形的产生就离不开DDS了。

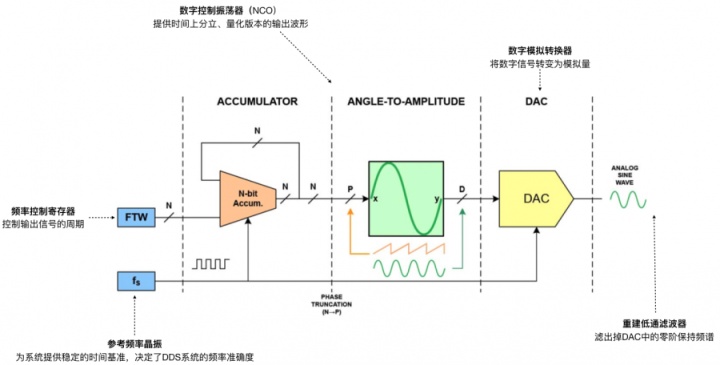

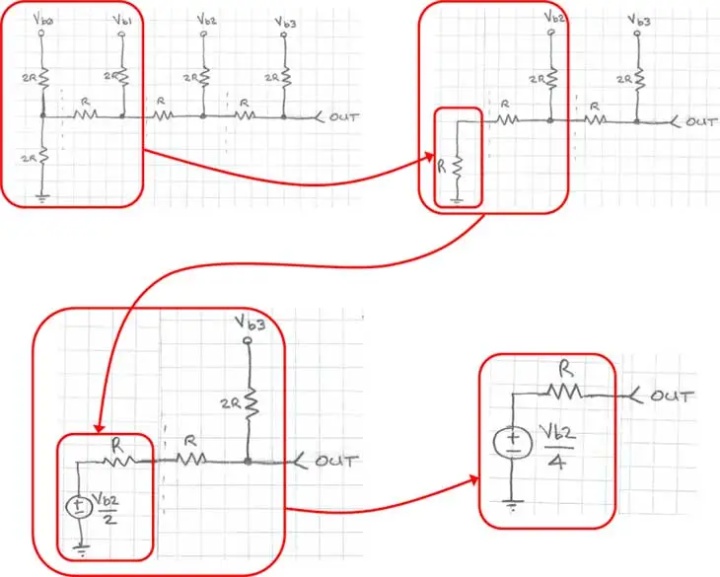

DDS的基本原理如下面的框图,主要由以下几个部分构成:

- 相位累加器 - 改变累加器的步进值,也就可以改变输出信号的频率;

- 存储的波形表 - 决定了你要产生的波形的形状,其深度和位数影响了输出信号的性能;

- 高速DAC - 将数字的波形转换为模拟的电信号,其分辨率位数和转换率影响了能够产生的电信号的最高频率和信噪比、SFDR等参数

- 在DAC后面还有模拟调理电路 - 对生成的信号进行幅度调节和频率分量的筛选

ADI公司有多种针对不同应用的DDS器件,其性能指标也不一样,由MCU通过SPI端口对DDS芯片进行编程即可得到你需要的波形、频率、幅度等。经典的器件AD9850、AD9833/37、AD9102等。

在具体的使用中仅一颗器件是不够的,也还是要需要设计专门的PCB来完成系统的功能 - MCU + DDS + 模拟链路 + 电源,一套下来,无论从制作成本还是调试的时间上都不见得是比较经济的方式,使用现成芯片也只能在其能力范围内,灵活性不高,用一颗器件应对不同可能的考题,是很难的。

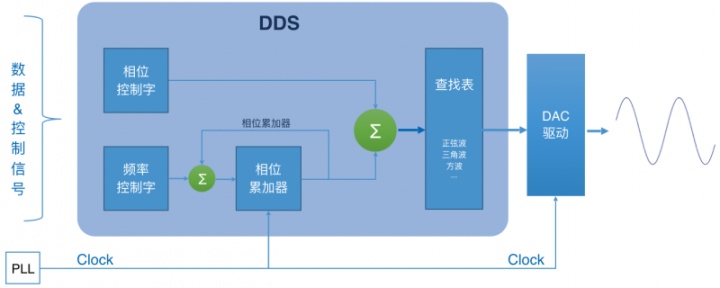

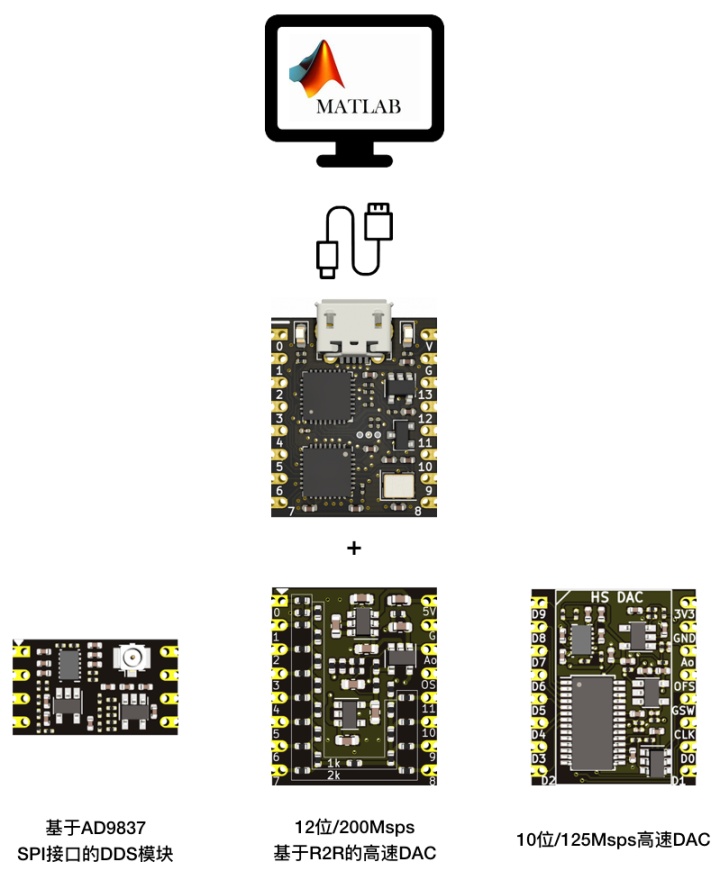

最佳的方式自然是使用FPGA + DAC + 模拟链路的方式来实现。

注:除了上图中的功能,按键输入控制和参数的输出显示乃至菜单,也都可以通过FPGA来实现

只要你了解FPGA的使用,理解了DDS的工作原理,通过非常简单的Verilog编程,就可以灵活地实现各种你需要的功能和性能。

能够实现DDS功能,对于FPGA内部资源的要求其实很小,只需要非常少的逻辑资源和有限的内部存储器就可以实现,一颗十几块RMB的FPGA只需要其不到1/5的资源就能够实现,而高速的DAC也非常便宜,尤其是采用R-2R的构成方式,20个电阻就可以构成10位/200Msps的高速DAC,这种方式生成的波形性能虽然相比商用的高速DAC(比如AD9740)有一定的降低,但足以满足电赛的需求。

随着国产化器件的高速发展,使用国产的价廉物美的高速DAC也可以用来做DDS信号发生器。比如我们硬禾学堂刚刚验证过的3Peak公司的3PD5651,就是跟AD9740兼容的10位/125Msps的高速DAC,我们用它做成的高速DAC模块,实测转换率能够高达200Msps无压力。

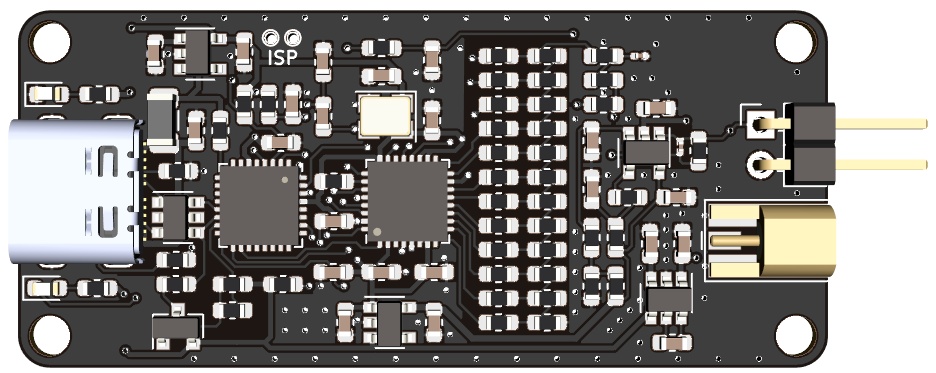

当然,无论你使用FPGA + R2R还是FPGA + DAC,都需要你来设计PCB才能实现,如果实现高达100Msps的转换率,对PCB的设计能力也是有要求的。为了方便参加电赛的同学们在不需要制作PCB的情况下也能方便使用DDS,我们硬禾学堂专门制作了半成品的16管脚的模块 - FPGA最小系统模块、R2R高速DAC模块、基于AD9740的200Msps的高速DAC模块以及基于3PD5651的125Msps的模块。只要将FPGA模块和DAC模块简单地连接在一起,就可以方便地实现DDS的功能。

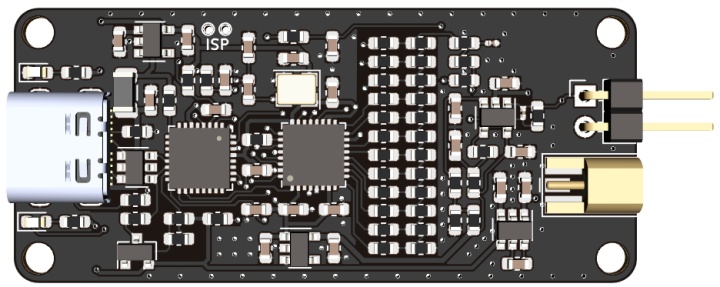

如果你嫌两个模块焊接都觉得麻烦,也可以使用下面的一体化的模块,可以通过USB端口对其供电和编程、UART通信,通过逻辑控制其中的参数,或由上位机通过UART对FPGA的逻辑进行参数配置。

是不是很方便?

下面我简单讲一下DDS的实现逻辑:

1 首先将你要实现的波形的一个周期的量化数据存放在FPGA内部的逻辑寄存器或块状RAM中,下面的代码就是存放一个64个10位数据来表征1/4周期正弦波的代码,由于正弦波4个象限的对称性,只需要1/4周期的数据即可,这样可以只使用1/4的逻辑或存储资源。

module 2 用查找表的方式寻址一个波形的整个周期, phase(相位)即为波表的256个地址,sin_out为10位的数据输出:

- module lookup_tables(phase, sin_out);

- input [7:0] phase;

- output [9:0] sin_out;

-

- wire [9:0] sin_out;

-

- reg [5:0] address;

- wire [1:0] sel;

- wire [8:0] sine_table_out;

-

- reg [9:0] sine_onecycle_amp;

-

- //assign sin_out = {4'b0, sine_onecycle_amp[9:4]} + 9'hff; // 可以调节输出信号的幅度

- assign sin_out = sine_onecycle_amp[9:0];

-

- assign sel = phase[7:6];

-

- sin_table u_sin_table(address,sine_table_out);

-

- always @(sel or sine_table_out)

- begin

- case(sel)

- 2'b00: begin

- sine_onecycle_amp = 9'h1ff + sine_table_out[8:0];

- address = phase[5:0];

- end

- 2'b01: begin

- sine_onecycle_amp = 9'h1ff + sine_table_out[8:0];

- address = ~phase[5:0];

- end

- 2'b10: begin

- sine_onecycle_amp = 9'h1ff - sine_table_out[8:0];

- address = phase[5:0];

- end

- 2'b11: begin

- sine_onecycle_amp = 9'h1ff - sine_table_out[8:0];

- address = ~ phase[5:0];

- end

- endcase

- end

-

- endmodule

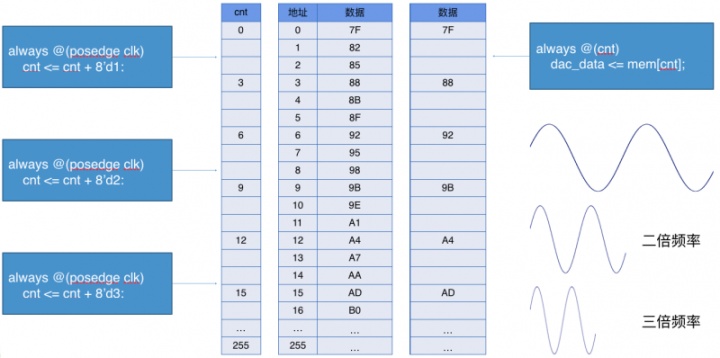

如果使用计数器作为地址输出,逐个地址的数据读出送给DAC,就可以得到频率为主时钟频率1/256的正弦波形。要改变输出频率,只有改变主时钟频率,这种方法得到“任意”频率是不可能的,另外对模拟链路的输出滤波器的设计也带来了巨大挑战。因此这就要下面的一步:

3 通过相位累加器来实现任意频率

比如下面的代码就能够通过一个24位的相位累加器,得到频率最小调节精度达到主时钟/2^24 ~ 主时钟/16M,比如主时钟为12MHz,则频率最小调节精度可以达到0.75Hz,相位累加器的值取27962就可以得到频率为20KHz的正弦波信号。

- reg [23:0] phase_acc; // 24位相位累加器

- always @(posedge clk) phase_acc <= phase_acc + 27962; //在12MHz的主时钟时输出20KHz频率的波形

- lookup_tables u_lookup_table(.phase(phase_acc[23:16]), .sin_out(dac_data));

4 利用内部锁相环PLL得到高频率的内部时钟

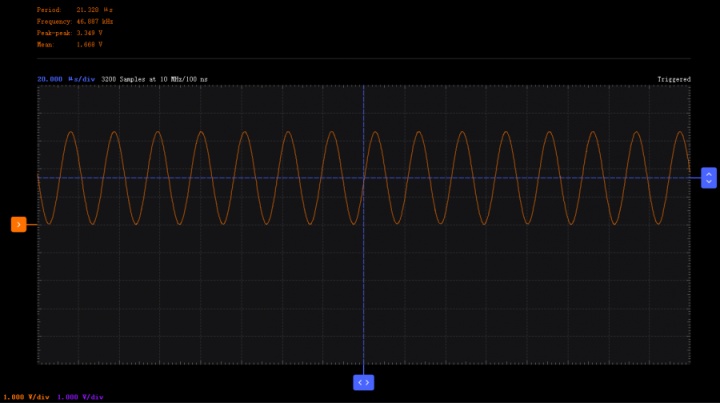

无论是MCU还是FPGA,外部的时钟源提供的频率都不会太高,比如我们常用的12MHz的时钟,根据奈奎斯特定律,以及低通滤波器的频响特性得到的DDS输出的频率最高为12MHz * 40% ~ 4.8MHz,如果想得到更高的输出频率,比如20MHz的正弦波形,那就需要DDS的主时钟高达50MHz,乃至更高,这样使得一个周期内的点数更多,比较理想的状态是一个周期的波形由10个以上的点构成,也就是20MHz的正弦波最好使用200MHz的主时钟。那就需要用到PLL,由输入的低频时钟得到内部的高频时钟用于DDS的逻辑和DAC的转换时钟。

在我们的系统中,选用了12MHz的输入频率,可以通过内部PLL得到192MHz(12MHz*16)的内部时钟频率,生成20MHz的正弦波毫无压力。

下面是PLL + 相位累加器的代码,PLL通过调用FPGA内部的IP核来实现:

- wire clk_120m; //内部高倍时钟的名字cll_120m

-

- clk_pll u_clk_pll(.CLKI(clk), .CLKOP(clk_120m)); // 以Lattice的IPCore为例产生高速内部时钟

- // 从12MHz产生120MHz,用以内部的逻辑以及DAC转换

- reg [23:0] phase_acc; // 24位相位累加器

-

- always @(posedge clk_120m) phase_acc <= phase_acc + 2796; //在120MHz的主时钟时输出20KHz频率的波形

- lookup_tables u_lookup_table(.phase(phase_acc[23:16]), .sin_out(dac_data));

有细心的朋友会问,苏老师,您的模块上看不到常规使用的LC滤波器的影子啊?没有LPC滤波器如何滤除20MHz以上的混叠、非线性、杂散信号?

其实我们巧妙地利用了运算放大器的GBW和压摆率的指标,通过合理选择运算放大器,该放大器自身就能够实现对20MHz以内的信号进行线性放大,对20MHz以上的信号进行衰减的功能。

放大器的选用以及相关阻、容的值的选择可以根据具体的电路拓扑辅之以模拟仿真来实现,由于篇幅限制,这个在这里不再细说了。

要了解更多关于DDS的实现方法和硬件信息,可以通过下面的二维码或点击左下角的“阅读原文”直接到达。

https://wxb04f9fe0f7b92b52.h5.xiaoe-tech.com/mp/eyJpZCI6MTA5Mzc1Mn0 (二维码自动识别)