- 1网络安全综合实验(eNSP)(DHCP、OSPF、NAT、防火墙、ACL)_ensp安全实验

- 2Python根据文件名划分文件_python分割文件名

- 3Diffusion Model, Stable Diffusion, Stable Diffusion XL 详解

- 4[转]Bram和Dram的区别

- 5中兴新支点操作系统小教程——用户_中兴新支点系统拷贝文件

- 6Windows Server安全日志与系统事件变更审计_windows server2008 安全日志审计

- 7git merge 回退_git常用命令

- 8运行stable-diffusion-webui-directml时报RuntimeError: Torch is not able to use GPU的错误解决办法_torch is not able to use gpu;

- 9常用游戏服务架构(http,golang技术版)_golang 游戏框架 http

- 10SpringBoot 解决跨域问题的 5 种方案!_springboot跨域配置

7 Series FPGAs Integrated Block for PCI Express IP核基本模式配置详解_use startup primitive external to ip

赞

踩

7 Series FPGAs Integrated Block for PCI Express® core" 是在 Xilinx 的 7 系列 FPGA(如 Virtex-7, Kintex-7, Artix-7 等)中集成的专门用于处理 PCI Express(PCIe)协议的IP核,是 FPGA 架构中的一部分,被设计为高效且易于配置的方式来实现 PCIe 接口。它通常包含物理层(PHY)和链路层(MAC)的功能,可以大大简化用户实现 PCIe 接口的复杂性,并提升性能。

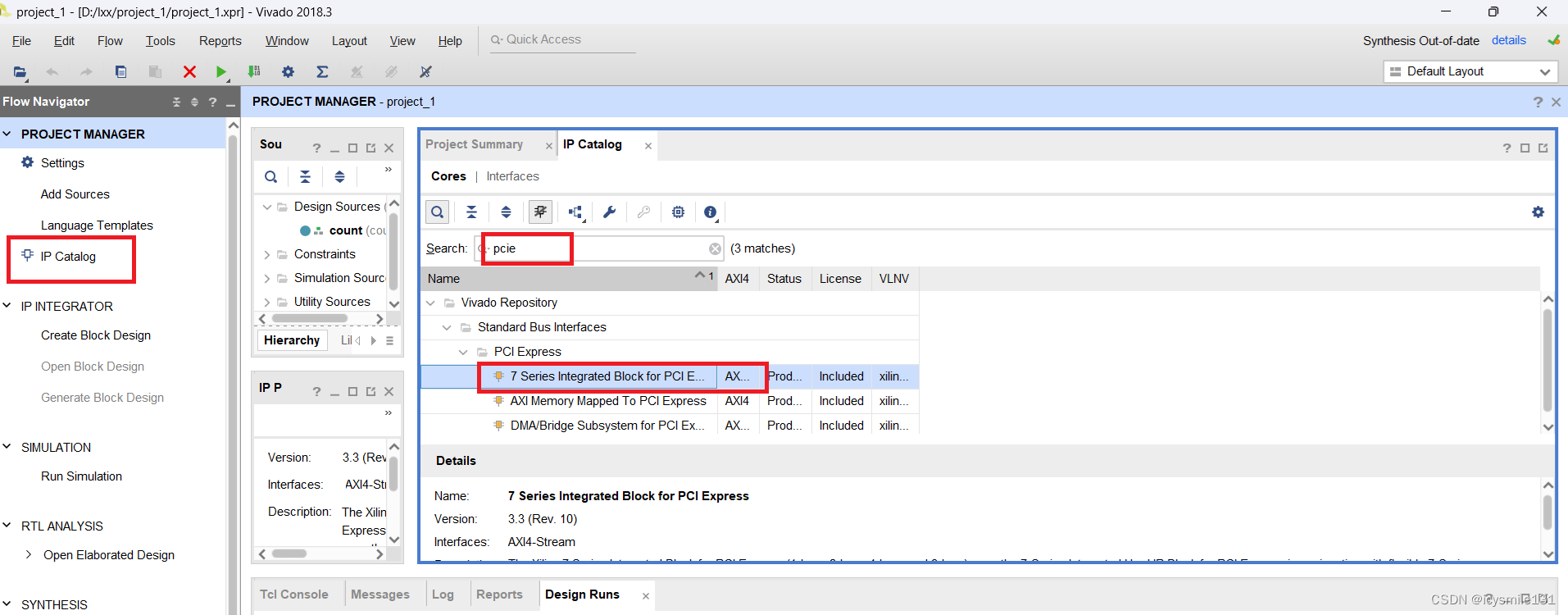

7 Series FPGAs Integrated Block IP核基本模式配置的流程如下:

1 打开或新建一个工程。

2 如下图所示,找到7 Series FPGAs Integrated Block IP核。

3 双击IP,或从工具栏或右键菜单中选择“Customize IP”命令,打开该IP核的配置页。

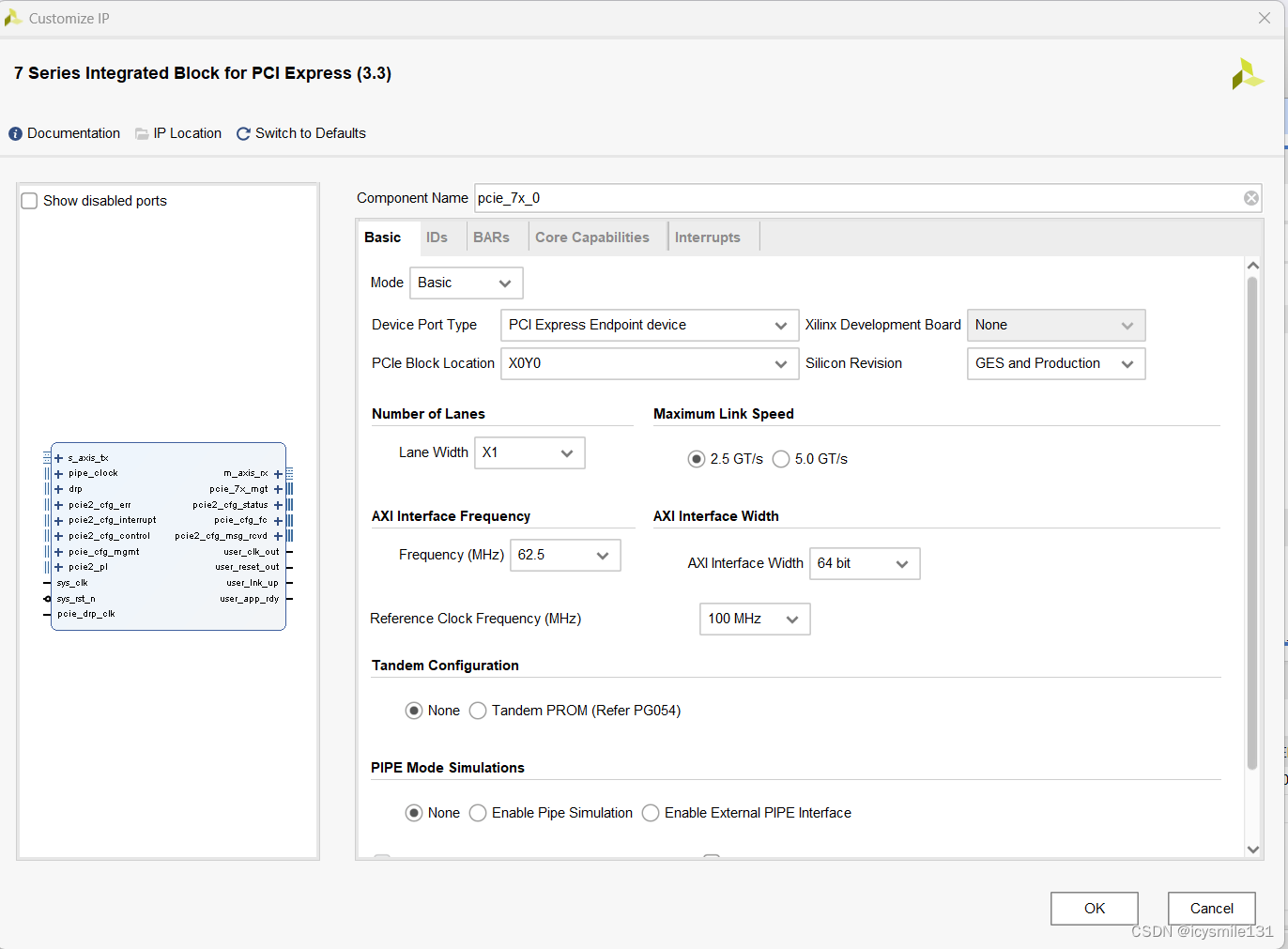

4 Base选项页配置

Base Mode 参数定义了IP核的基本设置和属性。

Component Name

为PCIe IP核生成的输出文件的基础名称。名称必须以字母开头,并可以由以下字符组成:a到z、0到9以及“_”。

Mode

选择PCIe IP核配置为Basic模式或Advanced模式。其中,Basic模式可能只提供IP核的基本配置选项,而Advanced模式可能提供更多的定制选项和详细配置。

Device Port Type

指示PCI Express逻辑设备的类型,根复合体(Root Complex)或端点(Endpoint)等。

PCIe Block Location

从可用的集成块中选择,以启用生成特定位置的约束文件和引脚分配。

如果选择了Xilinx开发板,则此选项可能不可用,因为开发板通常已经预定义了PCIe块的位置。

Xilinx Development Board

选择Xilinx开发板以启用生成针对该开发板的特定约束文件。

ilicon Revision

选择硅版本,可能的选项包括Initial_ES(工程样本)或GES_and_Production(工程样本和生产版本)。其中,样本用于早期验证和测试,而生产版本用于最终产品。

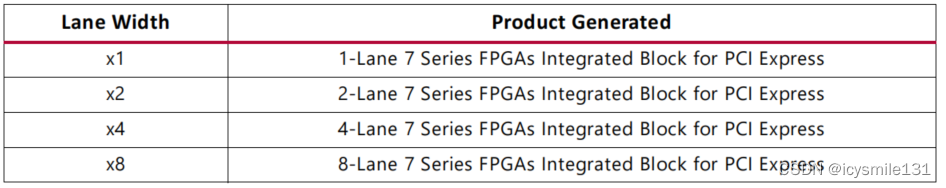

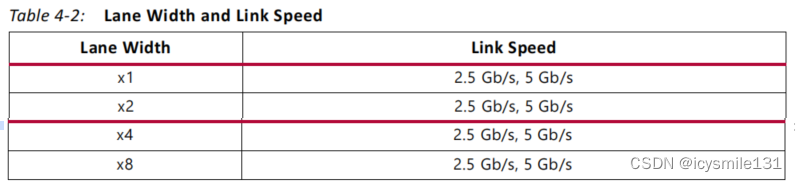

Number of Lanes

选择初始的通道宽度。可用的宽度和与之关联的IP核如下表所示。较宽的通道宽度IP核如果连接到较小通道宽度的设备,则能够向下兼容到较小的通道宽度。这提供了灵活性,可以根据连接的设备动态调整带宽。

Maximum Link Speed

选择PCIe设备所支持的最大链路速度。

7系列FPGA的PCIe集成块支持不同的链路速度,如下表所示。这些速度包括PCIe 2.0的5 GT/s、PCIe 3.0的8 GT/s等。如果设备连接到一个支持较低链路速度的设备,较高的链路速度IP核可以向下兼容到较低的链路速度。

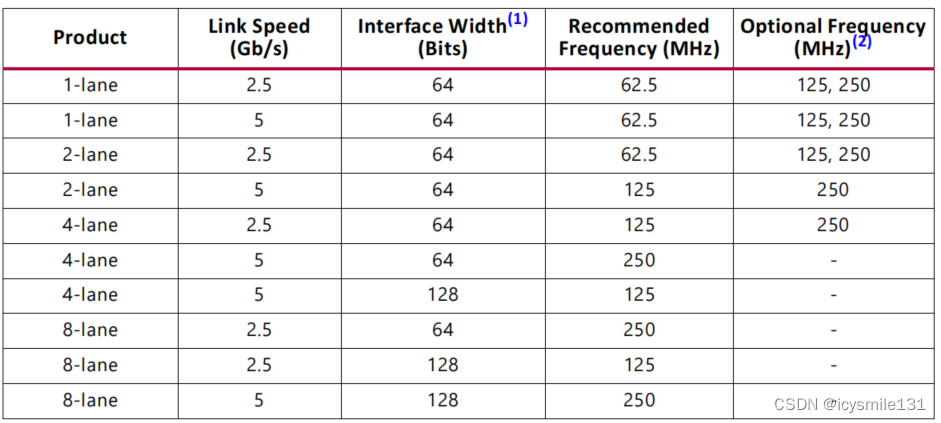

AXI Interface Frequency

选择PCIe IP核用户接口的时钟频率。每个通道宽度,都有多个频率选择,包括默认频率和替代频率,如表4-3所定义的那样。

如果可能的话,使用默认频率。选择替代频率并不会在IP核中导致吞吐量的差异,但它允许用户应用以不同的速度运行。

- 注意:

- 接口宽度是一个静态选择,不会随着动态链路速度的变化而改变。

- 对于所有Artix-7设备,当选择速度等级为-1、-1i、-1l、-1m或-1q时,不支持250 MHz的可选频率。只支持62.5 MHz和125 MHz这两个频率。

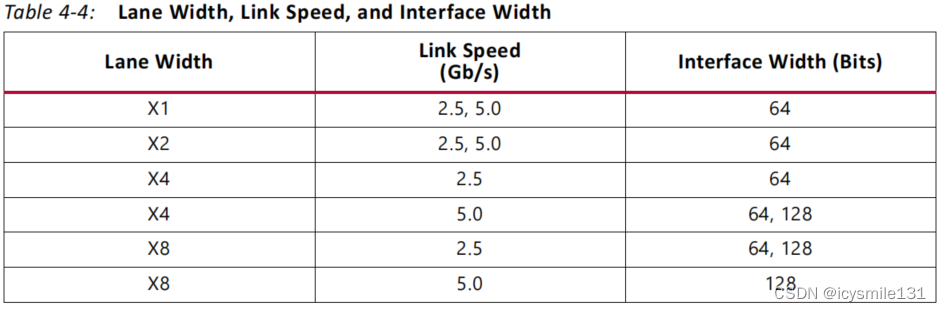

AXI Interface Width

择AXI接口的宽度,如表4-4所定义。默认接口宽度是可能的最低接口宽度。

根据需求选择合适的AXI接口宽度。较宽的AXI接口可以提供更高的数据传输带宽,但也会占用更多的FPGA资源。

Reference Clock Frequency

选择sys_clk上提供的参考时钟的频率。

Tandem Configuration(串联配置)

允许将两个FPGA设备配置为单一PCIe设备,提供更高的带宽或冗余。

选项:无(None)、Tandem PROM和Tandem PCIe。支持的设备包括K325T、K410T、K420T、V485T和K160T。对于Zynq 7Z030、7Z045和7Z100设备,仅支持Tandem PROM选项,不支持Tandem PCIe模式。

PIPE Mode Simulations(PIPE模式仿真)

- 无(None):默认选项,不提供PIPE模式仿真。

- 启用PIPE仿真(Enable Pipe Simulation):此选项会生成一个IP核,该IP核可以与连接的PIPE接口进行仿真。此选项仅在选择了示例设计中的共享逻辑(时钟)选项时(参见“Shared Logic”)才适用于Endpoint和Root Port配置。

- 启用外部PIPE接口(Enable External PIPE Interface):此选项允许外部的第三方总线功能模型(BFM)连接到PCIe集成块的PIPE接口。

Enable External GT Channel DRP

将外部GT通道(Gigabit Transceiver通道)的DRP(Dynamic Reconfiguration Port)端口引出到IP核顶层。DRP端口用于动态地重新配置GT通道的参数。

- ext_ch_gt_drpdo[15:0]:DRP输出数据端口。

- ext_ch_gt_drpdi[15:0]:DRP输入数据端口。

- ext_ch_gt_drpen[0:0]:DRP使能端口。

- ext_ch_gt_drwe[0:0]:DRP写使能端口。

- ext_ch_gt_drprdy[:0]:DRP就绪端口,指示外部GT通道DRP是否准备好使用且未被内部逻辑占用。

Enable External Startup Primitive

启用STARTUP基本单元。STARTUP基本单元通常用于在FPGA启动时执行一些特定的初始化操作。默认情况下,这个参数是禁用的。

Additional Transceiver Control and Status Ports

提供了对PCIe收发器的额外控制和状态访问。

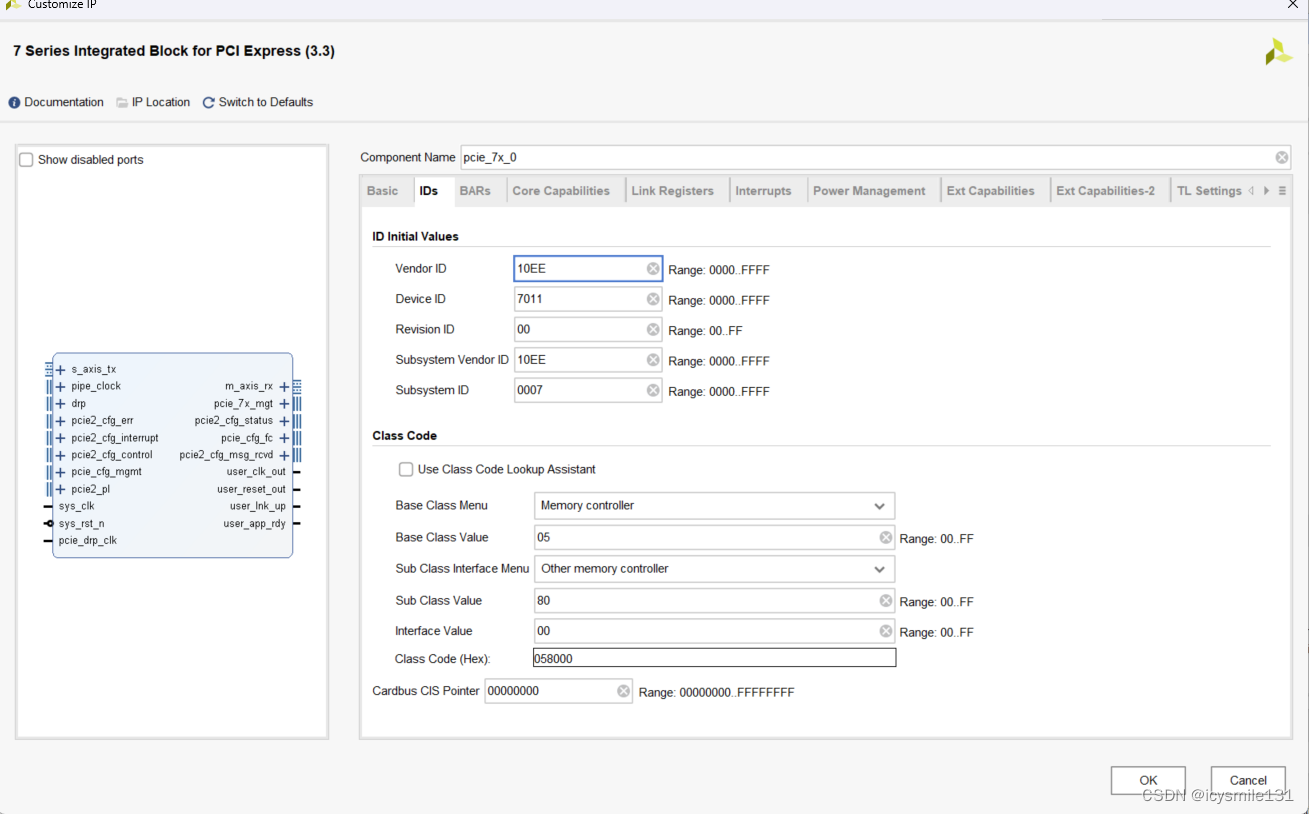

5 Identifiers (IDs)选项页

这个页面用于自定义IP的初始值、类代码和Cardbus CIS指针信息。

ID Initial Values

- Vendor ID:标识设备或应用的制造商。有效的标识符由PCI特殊兴趣小组(PCI Special Interest Group)分配,以确保每个标识符都是唯一的。默认值是10EEh,代表Xilinx的Vendor ID。你可以在这里输入一个厂商识别号。FFFFh是保留的。

- Device ID:应用的唯一标识符;默认值取决于所选的配置,通常是70<link speed><link width>h的形式。这个字段可以是任何值;根据你的应用需要更改这个值。

重要提示:由于Device ID参数是根据设备系列(7系列IP中为7)、EP或RP模式、链路宽度和链路速度来评估的,因此当这些参数中的任何一个发生变化时,Device ID都会发生变化。例如,如果你首先更改Device ID的值,然后更改链路速度、链路宽度、EP或RP中的任何一个,那么Device ID值将被重新评估并替换你之前设置的值。因此,Xilinx建议首先更改链路宽度、链路速度和Device Port类型,然后再更改Device ID值。

- Revision ID:指示设备或应用的版本;是Device ID的扩展。

- Subsystem Vendor ID:进一步指定设备或应用的制造商。通常与Vendor ID相同,但允许您为子系统(由多个组件组成的系统)指定一个不同的制造商ID。默认为10EE,代表Xilinx的Vendor ID。0000h是保留值。

- Subsystem ID:进一步指定设备或应用的制造商。这通常与Device ID相同,但在某些情况下,您可能希望为子系统(由多个组件组成的系统)指定一个不同的ID。默认值取决于所选的链路宽度和链路速度。0000h是保留值。

Class Code

用于标识设备的总体功能,并被分为三个字节大小的字段:基本类、子类和接口

- 基本类:广泛标识设备执行的功能类型。

- 子类:更具体地标识设备功能。

- 接口:如果存在,定义了一个特定的寄存器级编程接口,允许与设备无关的软件与设备进行交互。

Class Code Look-up Assistant

提供了一个选定的设备一般功能的基本类、子类和接口值。该查找助手工具仅显示选定功能的这三个值。

必须在类代码字段中输入这些值,以便它们被翻译成设备设置。

Cardbus CIS Pointer 是用于Cardbus系统的,它指向Cardbus卡的卡片信息结构。如果该字段非零,则必须在正确的位置存在适当的卡片信息结构。其默认值是0000_0000h,值范围是0000_0000H-FFFF_FFFFH。

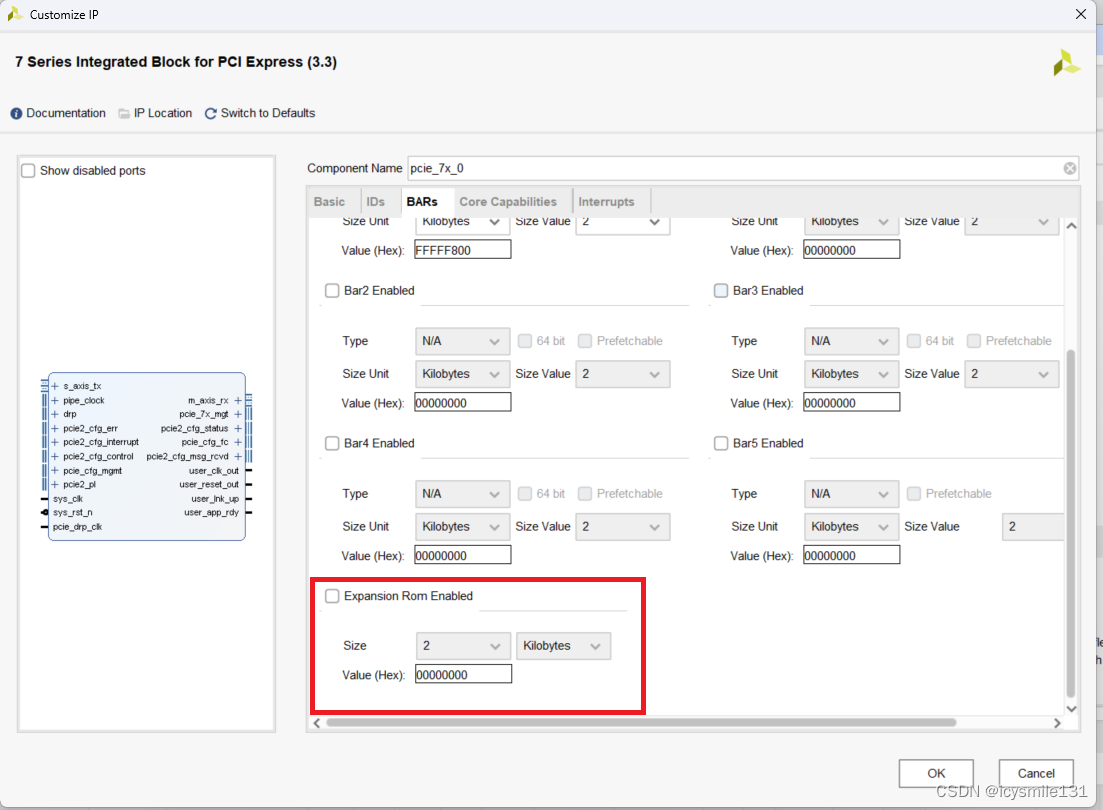

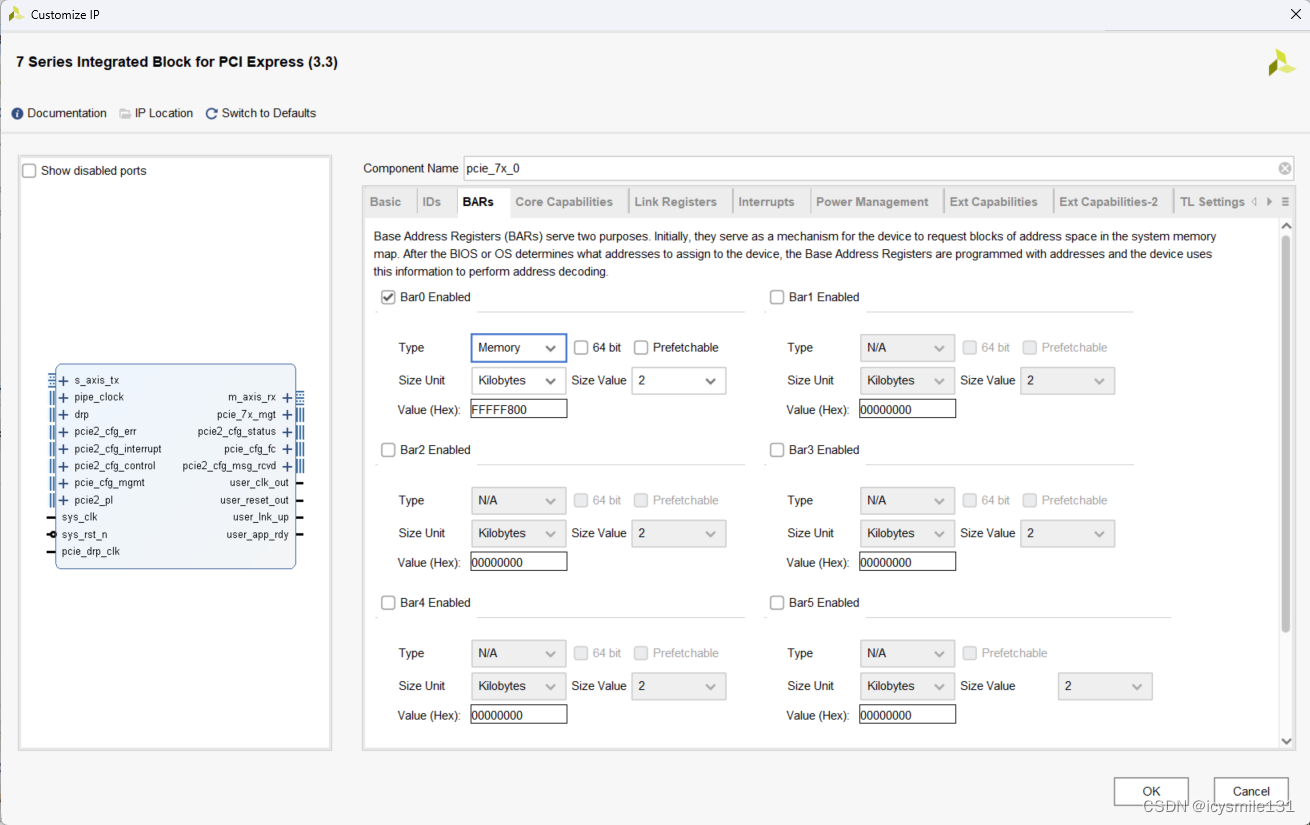

6 BARs 选项页

Base Address Registers (BARs) 是PCI和PCIe设备中的寄存器,用于描述设备所需的资源,如内存地址空间和I/O端口空间。它们提供了设备和操作系统之间的通信机制,使系统可以为设备分配实际的资源地址,并使设备能够在这些资源上进行操作。在PCI Express的Endpoint配置中,BARs可以设置为32位或64位,具体取决于板卡上的FPGA芯片资源。在Endpoint配置中,可以支持多达六个32位BARs或三个64位BARs,以及扩展ROM BAR。在Root Port配置中,可以支持多达两个32位BARs或一个64位BAR,以及扩展ROM BAR。

BARs可以有两种大小:

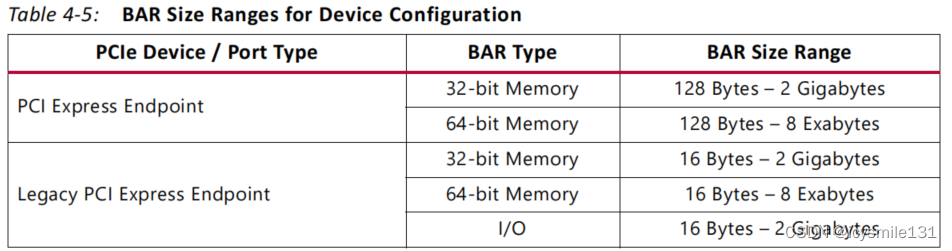

32位BARs:地址空间可以从128字节到2吉字节不等,通常用于内存到I/O的映射。

64-bit BARs: 地址空间可以非常小,只有128字节,也可以非常大,达到8 exabytes(2^63字节),仅用于内存映射,不用于I/O映射。

所有BAR寄存器的共同选项:

- 勾选框:勾选该框以启用BAR;取消勾选以禁用BAR。

- 类型:BAR可以是I/O或内存Memory。通常,应避免使用小于4 KB大小的Memory空间。允许的最小I/O空间是16字节;在所有新设计中应避免使用I/O空间。

- I/O:只能是32位;Prefetchable选项不适用于I/O BARs。I/O BARs仅对Legacy PCI Express Endpoint core启用。

- Memory:可以是64位或32位,并且可以是prefetchable的。当一个BAR被设置为64位时,它会使用下一个BAR作为扩展地址空间,并使下一个BAR不可访问。

- 大小:可用的Size范围取决于PCIe® Device/Port类型和所选的BAR类型。表4-5列出了可用的BAR大小范围。

- Prefetchable:标识内存空间是否可以被预取。如果读取操作没有副作用(即,读取时数据不会被破坏,如从RAM中读取),则该内存空间是可预取的。当适用时,字节写入操作可以合并为一个双字写入操作。

- Value(Hex):基于当前选择分配给BAR的值。

- 64位寻址:当将该IP核配置为PCIe(非Legacy)Endpoint时,对于设置了可预取位的所有BARs(除了BAR5),必须支持64位寻址。对于没有设置可预取位的所有BARs,允许使用32位寻址。与Legacy Endpoint相关的可预取位要求不适用。PCI Express Endpoint支持的BAR的最小内存地址范围是128字节,而Legacy PCI Express Endpoint支持的BAR的最小内存地址范围是16字节。

- 禁用未使用的资源:

为了获得最佳结果,建议禁用未使用的基地址寄存器以节省系统资源。当未使用的BAR被取消选择时,相应的基地址寄存器将被禁用。这有助于确保系统资源的有效利用,并减少不必要的硬件开销。

Expansion ROM Base Address Register

根据PCI 3.0 Local Bus Specification [Ref 2],Expansion ROM BAR最大不应大于16 MB。选择一个大于16 MB的地址空间可能会导致一个不符合规范的IP核。

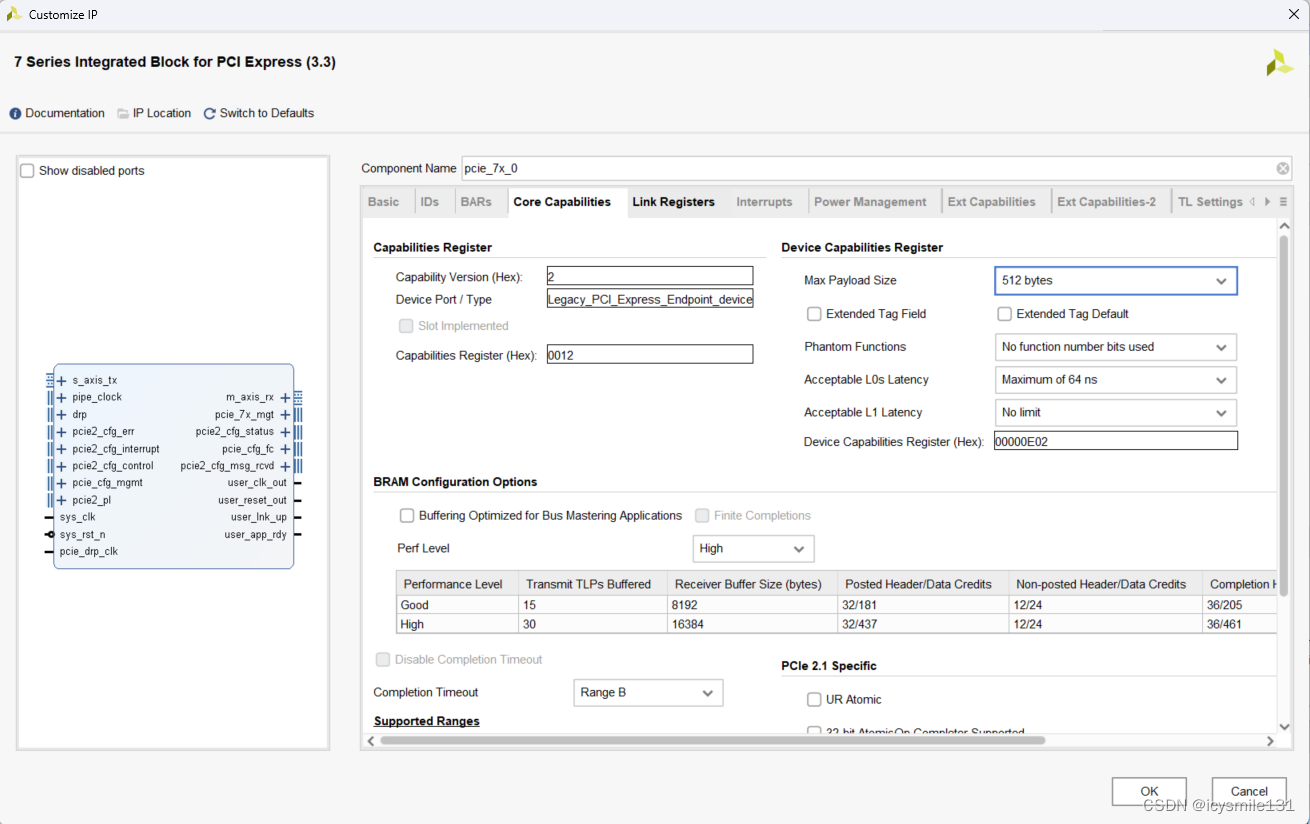

7 Core Capabilities

用于自定义IP的初始值、类代码(Class Code)和Cardbus CIS指针信息。这些参数主要涉及到PCI Express设备的一些基本属性和功能。

- Capability Version:指示PCI-SIG®定义的PCI Express功能结构版本号。不能更改。

- Device Port Type:指示PCI Express逻辑设备的类型。这决定了设备在PCIe系统中的角色和用途。

- Slot Implemented(插槽实现):指示与该端口关联的PCI Express链路是否连接到一个插槽。这个设置仅对PCI Express Root Complex的Root Port或PCI Express Switch的Downstream Port有效。

- Capabilities Register:显示由集成块提供的Capabilities寄存器的值,不能更改。

- Device Capabilities Register:显示由集成块提供的Device Capabilities寄存器的值,不能更改。

Block RAM 配置选项

Buffering Optimized for Bus Mastering Applications:使设备向其链路伙伴通告针对总线主控应用优化的信用设置。这有助于优化总线主控模式下的数据传输性能。

Performance Level:决定了接收器和发射器的大小。显示的表格指定了与所选最大有效载荷大小相对应的每个性能级别选项的接收器和发射器设置,包括在发射器中缓冲的TLP(事务层数据包)数量、接收器大小、核心向链路伙伴通告的信用数量以及配置所需的Block RAM数量。

Finite Completions:设备将向其链路伙伴通告接收器中实际可用于完成的空间量。对于Endpoint来说,这不符合PCI Express基础规范修订版2.1的要求,因为Endpoint需要通告无限量的完成空间。

Disable Completion Timeout :允许禁用某些情况下的完成超时机制。

Completion Timeout:指定了设备可以处理的完成超时范围。不要让完成超时机制在少于10毫秒的时间内过期,以确保系统稳定性和可靠性。

Device Capabilities2 Register:显示发送到IP核的Device Capabilities2寄存器的值,不能更改。

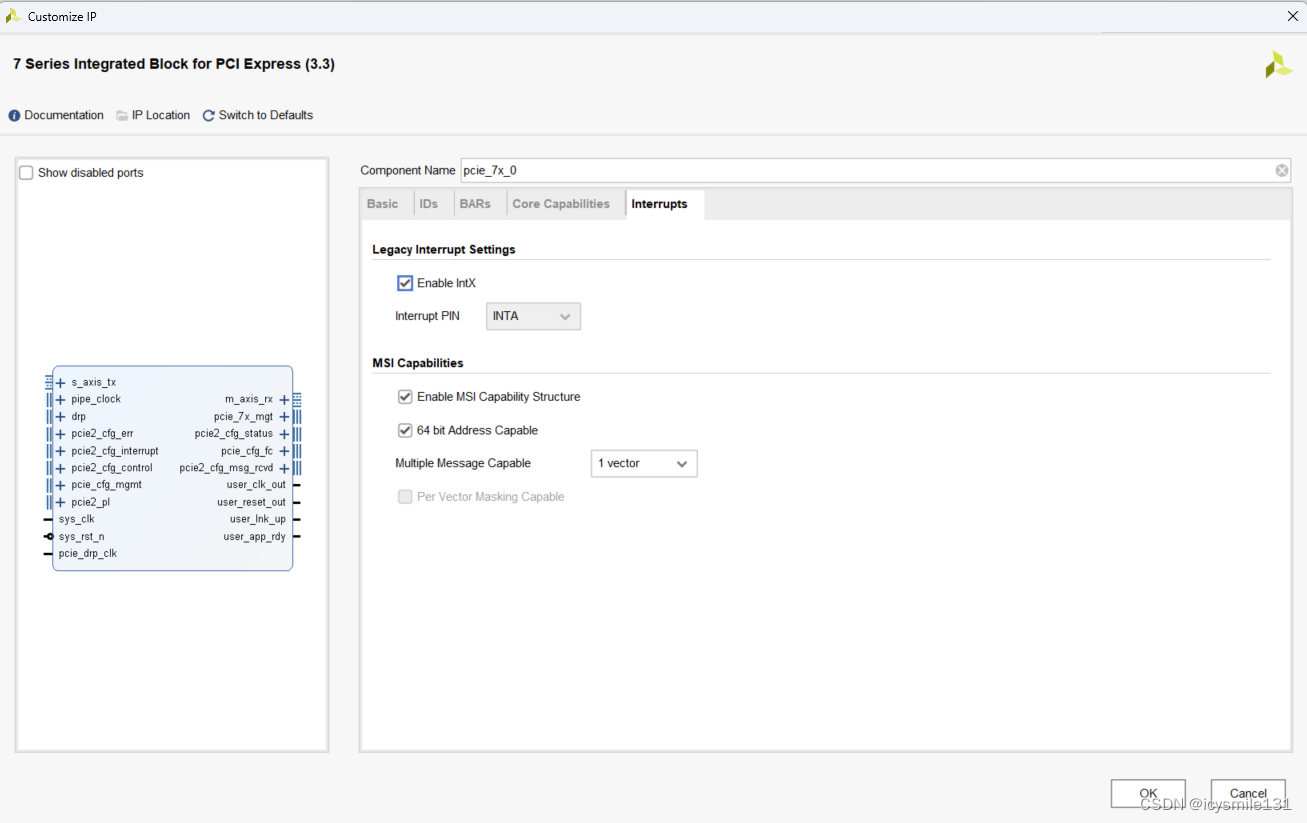

7 Interrupts选项页

如图4-5所示的中断参数设置包括传统的中断设置和MSI(Message-Signaled Interrupts,消息信号中断)能力。这些设置用于配置和管理PCIe设备的中断行为,以便在需要时通知主机系统。根据具体的应用需求和系统架构,可以选择适当的中断设置。

Legacy Interrupt Settings

Enable INTX:允许PCI Express设备使用INTx中断。INTx中断是传统的PCI中断机制,其中“x”可以是A、B、C或D,代表不同的中断线。

Interrupt PIN:如果设置为“None”,则表示不使用传统中断。这里提到“Only INT A is supported”,意味着只支持INT A中断线。

MSI Capabilities

MSI是PCI Express设备使用的一种中断机制,它比传统的INTx中断更高效。

Enable MSI Capability Structure:允许PCI Express设备使用MSI中断,而不是传统的INTx中断。

64 bit Address Capable:该PCI Express功能支持发送64位消息地址。这允许更大的地址空间,可能对于某些高级功能或大量MSI消息是必要的。

Multiple Message Capable:选择从Root Complex请求的MSI向量的数量。MSI向量是MSI消息的不同类型或类别,每个向量可以映射到不同的中断处理程序。

Per Vector Masking Capable:该功能支持MSI每向量屏蔽。这意味着你可以单独地启用或禁用每个MSI向量,从而更精细地控制中断处理。

传统的INTx中断机制简单但可能效率较低,而MSI则提供了更高的效率和灵活性。设计中应根据硬件和需求,选择最适合设置。