热门标签

热门文章

- 1android 快速亮暗屏_Android设备闪屏怎么办?手机屏幕一会亮一会暗怎么办

- 2CFAR原理详解及其matlab代码实现_cfar检测原理

- 3第六届工业人工智能国际会议(IAI 2024)征稿 截止日期:5月15日 EI检索_iai会议

- 4可路由计算引擎实现前置数据库

- 5《开源大模型与闭源大模型的数据隐私深度洞察》

- 6win10 android,Win10将原生兼容安卓App,但模拟器不会被打败

- 7BIT《Python语言程序设计》 python123题目:hw6-文件与数据格式_中文词语逆序python123

- 8sql日期格式转换_sql 日期转换

- 9springCloud Eureka注册中心配置详解_eureka配置中心

- 10专有软件不是唯一!试试54款开源服务器软件[转]

当前位置: article > 正文

【FPGA】正原子XC7A35T

作者:小小林熬夜学编程 | 2024-05-30 07:48:54

赞

踩

【FPGA】正原子XC7A35T

25_实战篇:时钟IP核MMCM(第一讲:时钟资源讲解)_哔哩哔哩_bilibili

25时钟IP核MMCM

7系列的时钟资源

bufferG

bufferR

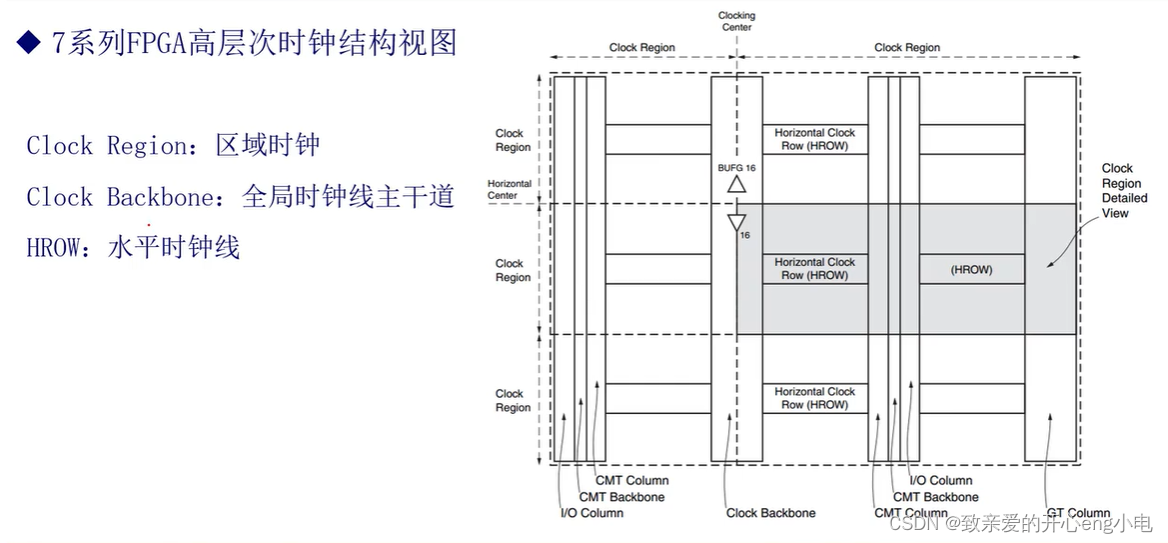

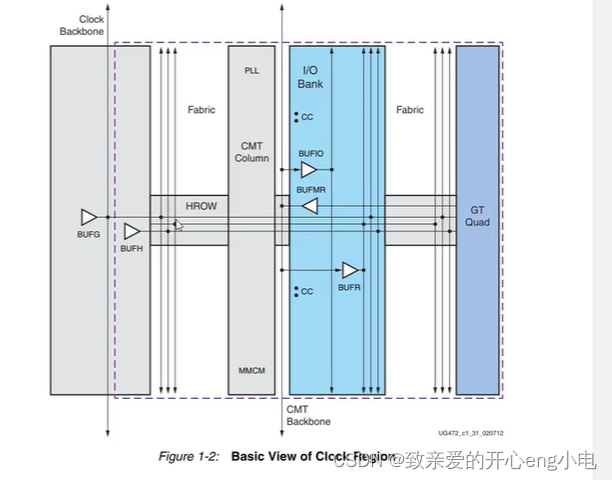

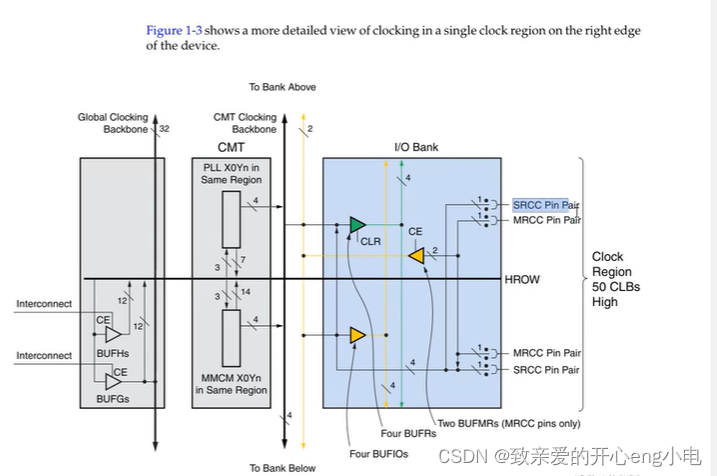

下图可视为一个FPGA(官方手册)

4

4

MRCC,SRCC

全局时钟:MRCC P

差分时钟:MRCC P,N

单时钟:接P

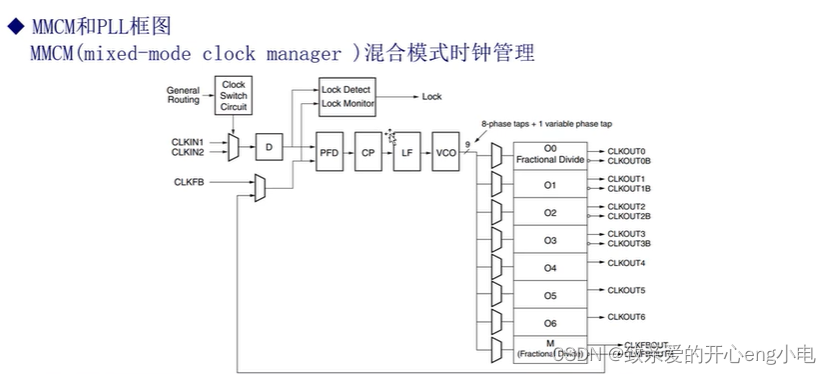

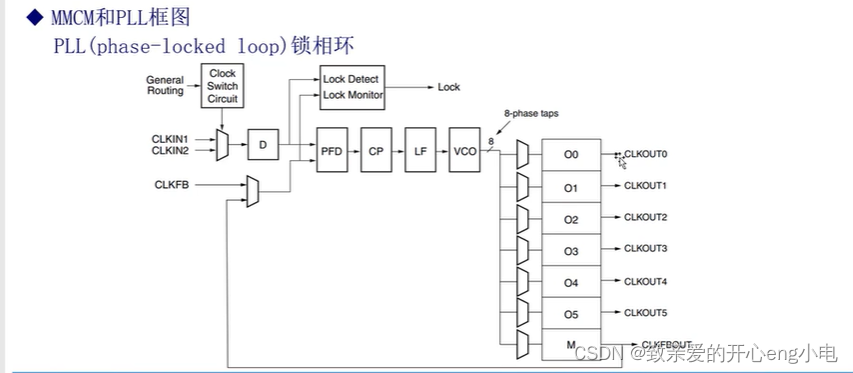

MMCM可以实现动态的调整,输出反向,PLL不行。除了这一点,两者完全相同

实战

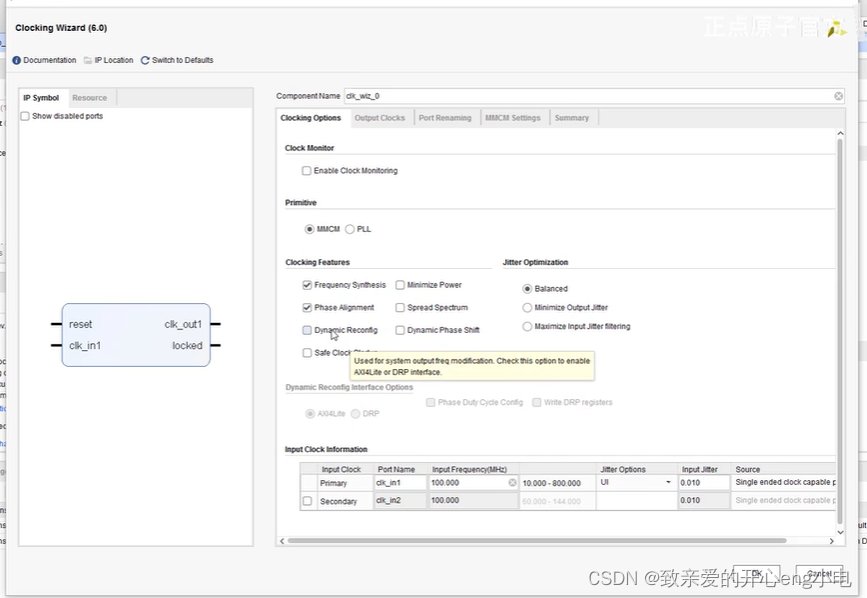

选项卡分析

frequency sythesis:输出不同频率的时钟

phase alignment:相位关系

dynamic recording:动态调整输出时钟频率

safe clock startup:只有在输出稳定的时候有时钟

minimize power:电源优化

dynamic phase shift:动态调整输出时钟相位

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小小林熬夜学编程/article/detail/645940

推荐阅读

相关标签