热门标签

热门文章

- 1企业—Docker容器之docker安全_mem限额

- 2ERROR: Could not find a version that satisfies the requirement pytest-runner (from versions: none)

- 3Android 修改home下的文件夹名称为英文_手机文件怎么改英文路径格式

- 4自然语言处理(NLP)——前馈网络_前馈神经网络在语言加工中的应用

- 5关闭和修改SpringBoot启动Logo_springboot启动只显示logo

- 6金仓数据库KingbaseES PIPELINE子句详解_kingbase 管道函数

- 7AIGC专题:Sora展示文生视频能力惊艳,重视内容生产工具层革新

- 8使用又拍云让网站实现https访问_又拍云访问例子

- 9Taro和uniapp的区别?_taro和uniapp对比

- 10Mac系统下PHP7.2和Yaf框架安装_设置yaf 环境变量

当前位置: article > 正文

xilinx开发过程中的ip核配置总结_xilinx spi ip核

作者:小小林熬夜学编程 | 2024-06-10 20:46:01

赞

踩

xilinx spi ip核

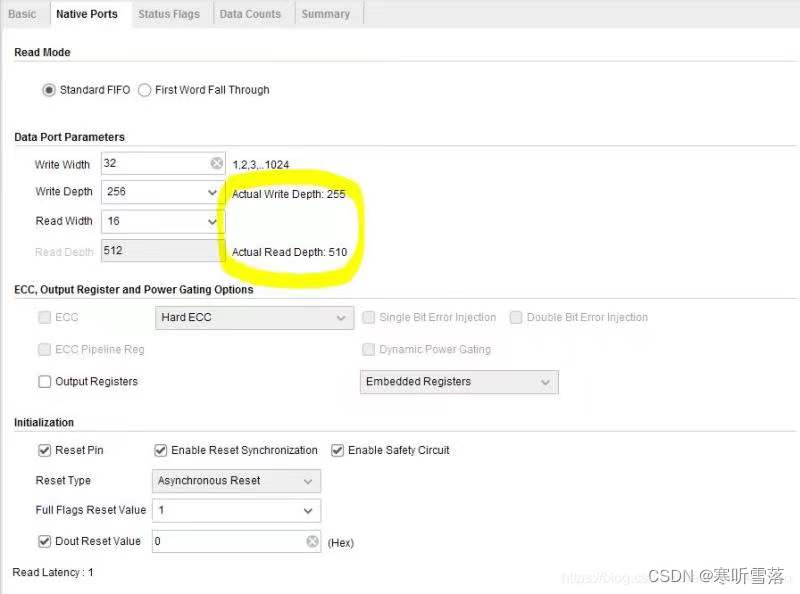

1,XILINX的FIFO,不同带宽输入输出,输出时,默认是先输出高位,再输出低位。这个能不能设置?先输出低位再到高位?答:在写入的时候,切换下位置就行了。

2,zynq7020 fpga启动了,但是ps没反应,ps灯不闪烁,程序直接ram运行,ps正常。

后续解答

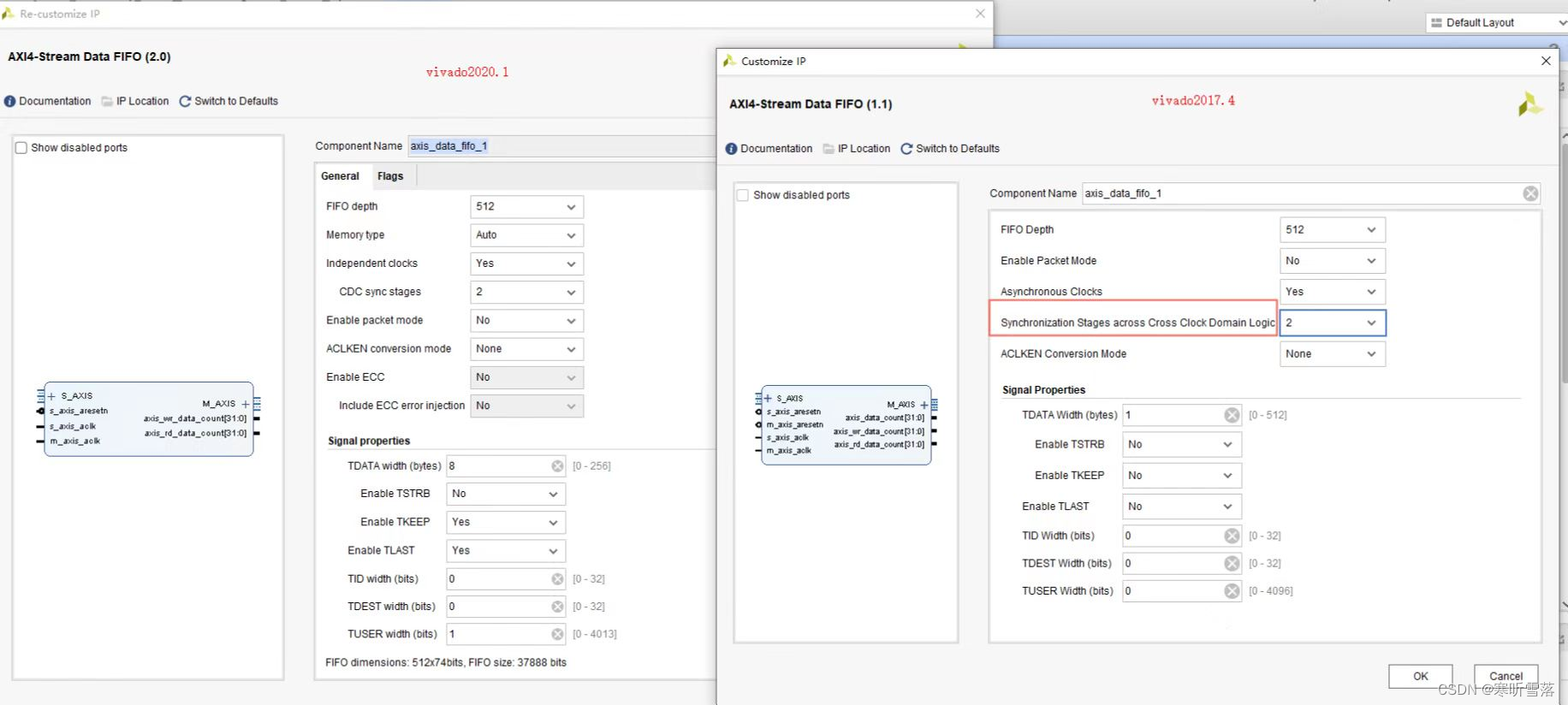

3, FIFO这种复位时钟个数有什么要求?

同步就是一个、异部就是两个,xilinx的板子没什么差异

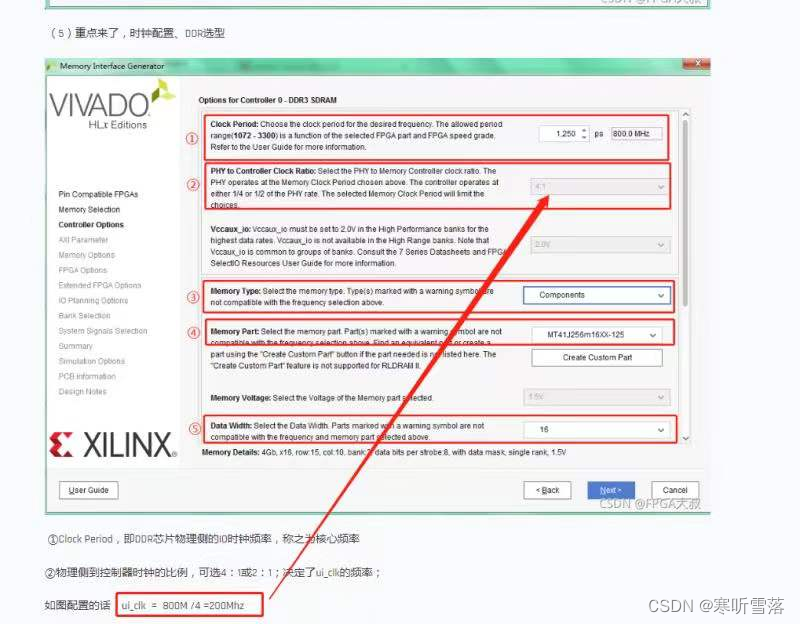

4, DDR3用什么运行频率?能不能用很低的频率让它工作呢?

K7的DDR可以跑到800M,用户逻辑可以跑到200M。

5,PS的以太网用emio经过gmii转rgmii后Txclk变成了2.5Mhz,而用mio输出则是125Mhz。

6,uiudp_stack这个协议栈能使用MDIO吗?不能

uiudp_stack这个协议栈,我的phy协商的是100M,协议栈能正常工作吗?现在app_tx_ack这个信号没有拉高。100m, rgmii不能工作,协议栈能正常工作。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小小林熬夜学编程/article/detail/700283

推荐阅读

相关标签