- 1Linux 驱动学习笔记

- 2xilinx fpga学习笔记3_srlc32e

- 3循环神经网络在生成对抗网络中的应用

- 4【论文阅读】LLM4GCL: CAN LARGE LANGUAGE MODEL EMPOWER GRAPH CONTRASTIVE LEARNING?

- 5XILINX FPGA中的SERDES_xilinx芯片选择有serdes的

- 6【粉丝福利】秋天的第一个雷蛇键盘_razer键盘

- 7使用Mybatis批量插入大量数据的实践

- 8C++ STL面试题(做梦都没想到,面试官居然让我这样做!!!!!!!!!!!!!!!!!!!!)_c++stl面试

- 9 Hexo进阶高级教程(二)

- 10星舆科技:打造智能网联汽车中的下一代定位技术_定位在网联汽车中的意义是什么

31-JTAG电路设计

赞

踩

视频链接

JTAG电路设计(JLINK&XILINX&ALTERA)_哔哩哔哩_bilibili

JTAG电路设计

1、JTAG简介

JTAG(Joint Test Action Group):联合测试工作组,是在名为标准测试访问端口和边界扫描结构的IEEE的标准1149.1的常用名称。

JTAG是一种国际标准测试协议,主要用于芯片内部测试;验证设计与测试生产出的印刷电路板。

现在多数的高级器件都支持JTAG协议,如DSP、FPGA、CPLD器件等。

JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP(Test Access Port测试访问口)通过专用的JTAG测试工具对内部节点进行测试。

程序代码的下载和调试。

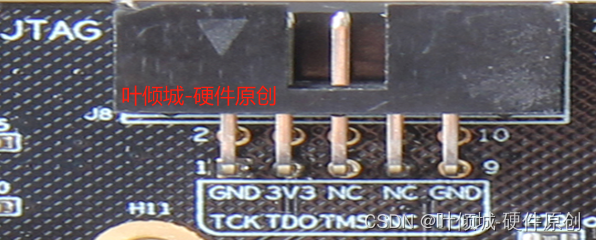

(对于板子上则对应的是(2.54 X2 X7或者X5 的防呆座子或者直接是2.54单排针)

2、JTAG接口解读及优点

JTAG的接口是一种特殊的4/5个接脚接口连到芯片上 ,在电路板上很多芯片可以将他们的JTAG接脚通过Daisy Chain(菊花链)的方式连在一起,并且集成电路只需连接到一个“JTAG端口”就可以访问一块PCB上的所有集成电路。这些连接引脚是:

TCK为测试时钟输入;

TDI为测试数据输入,数据通过TDI引脚输入JTAG接口;

TDO为测试数据输出,数据通过TDO引脚从JTAG接口输出;

TMS为测试模式选择,TMS用来设置JTAG接口处于某种特定的测试模式;

TRST为测试复位(可选)。输入引脚,低电平有效。

3、JTAG的电路时序

JTAG电路的时序如图所示,所有基于JTAG的操作都必须同步于JTAG时钟信号TCK。在TCK的上升沿读取或输出有效数据,有严格的建立、保持时间要求,因此一般情况下JTAG的时钟不会太高。

4、JTAG工作流程

5、JTAG工作原理

PC控制JTAG:用JTAG电缆连接PC的打印端口或者USB或者网口。最简单的是连接打印端口。

6、下载调试器-国际标准

下载调试器是将PC(例如通过USB协议)发送的命令转换为MCU(负责MCU内部外围设备)理解的语言(例如SWD或JTAG协议)的设备,加载代码并精确控制执行。

6.1、ARM调试器----STM32、全志H3等

JLINK V9 仿真器下载器STM32 ARM单片机 开发板烧录器J-LINK V9调试编程器 高配版+转接板【图片 价格 品牌 报价】-京东 (jd.com)

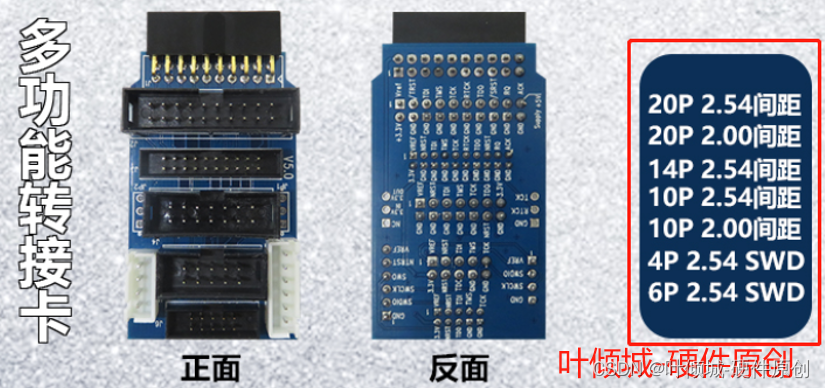

(2.54 X2 X10 )

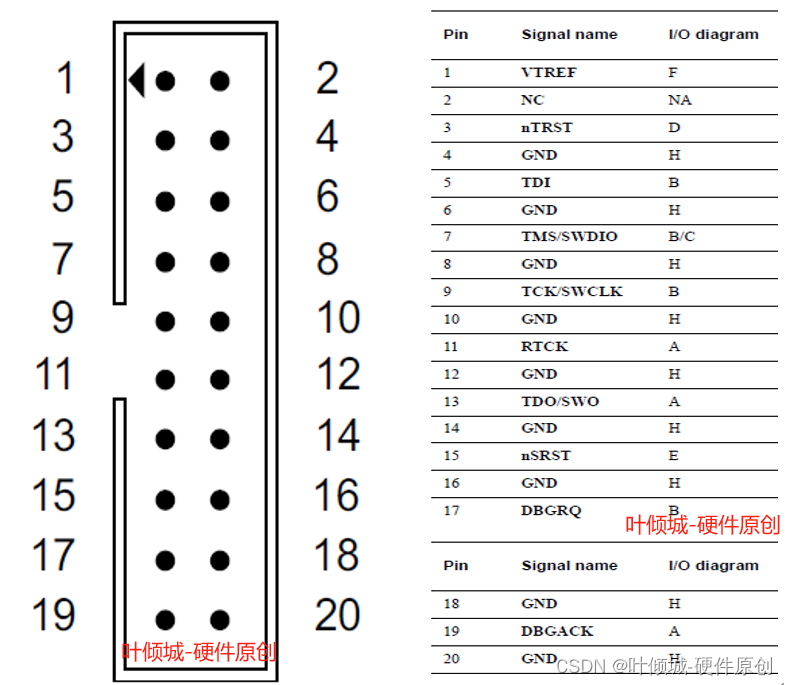

JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。

6.2、Xilinx(2.54 or 2 X2 X7 )

6.3、ALTERA ------USB blaster(2.54 X2 X5 )

出10根针

7、JTAG管脚定义

| 管脚符号 | 类型 | 描述 |

| TDI | 测试数据输入管脚 | Test Data Input(TDI) TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI输入端口串行输入的(由TCK驱动)。 TDI在IEEE 1149.1标准里是强制要求的。 |

| TDO | 测试数据输出管脚 | Test Data Output(TDO) TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO输出端口串行输出的(由TCK驱动)。 TDO在IEEE 1149.1标准里是强制要求的。 |

| TMS | 测试模式选择管脚 | Test Mode Selection Input(TMS) TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。TMS信号在TCK的上升沿有效。 TMS在IEEE 1149.1标准里是强制要求的。 |

| TCK | 测试时钟输入管脚 | Test Clock Input (TCK) TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。 TCK在IEEE 1149.1标准里是强制要求的。 |

| TRST | 测试复位输入管脚 | Test Reset Input(TRST) TRST可以用来对TAP Controller进行复位(初始化)。不过这个信号接口在IEEE 1149.1标准里是可选的,因为通过TMS也可以对TAP Controller进行复位(初始化)操作。 |

| VTREF | 接口信号电平参考电压一般直接连接Vsupply。 这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V,还是5.0V) | |

| RTCK | Return Test Clock: 可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。 | |

| nSRST | System Reset: 可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。 同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。 |

JTAG调试用到了TCK、TMS、TDI、TDO和TRST这几个脚。

其中,TRST不是必须的。TRST可以用来对TAP Controller进行复位(初始化)。不过这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。