热门标签

热门文章

- 1算法基础学习笔记----数据结构---KMP算法_董晓算法

- 2七道Android面试题,先来简单热个身_android开发面试题

- 3docker 本地部署大模型(ollama)_ollama 国内镜像

- 4企业国产操作系统选型适配实施方案_kylin-server-10-sp1-release-build10-2500-20201202-

- 5解决:PyCharm中找不到python打包工具_pycharm找不到python打包工具

- 6从码农到上岸公务员,到底是什么体验?工作感受真实分享!_程序员上岸事业编体验

- 7Python NumPy库详解:高效处理数组的利器

- 8内网渗透-内网穿透工具_python 自制内网穿透

- 9嵌入式学习笔记——STM32的时钟树_stm32时钟树

- 1080MHz~100MHz 频谱分析仪(E 题 本科组)-- 2015 年全国大学生电子设计竞赛试题_2015电子设计大赛e题

当前位置: article > 正文

ds & hdmi 原理_hdmi 驱动原理

作者:小惠珠哦 | 2024-08-18 09:01:17

赞

踩

hdmi 驱动原理

一、IDS 学习笔记

1、Overlay Controller

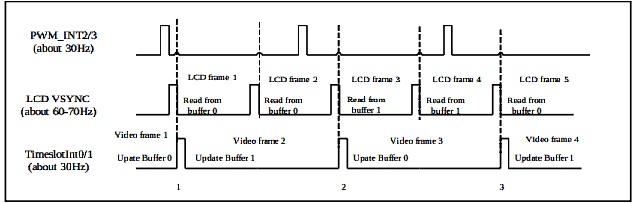

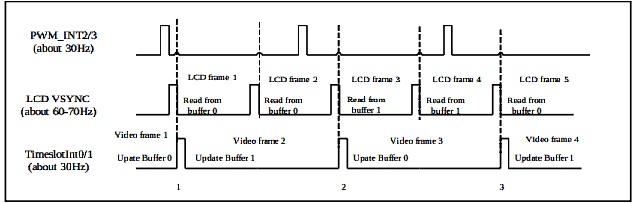

图像数据格式和4窗口融合由叠加控制器处理。叠加控制器可以根据窗口的中断生成一个窗口时隙,用户可以根据时隙中断更新帧缓冲的数据,比如:播放视频的时候。通常,视频的解码速度为 30 fps,LCD 的刷新率为 60-70 Hz,叠加控制器采用两路 PWM 定时器中断来避免潜在的风险。同步的过程如下图所示:

时隙中断同步于 PWM_INT2/3 和 VSYNC,在第一阶段:时隙中断产生后,下一帧的视频数据可以安全的解码并写入 buffer1,因为此时叠加控制器是从 buffer0 中读取视频数据到 LCD。同样的,在第二阶段 buffer0 的内容可以被更新。注:在使用窗口时隙中断时必须先设置好 PWM_INT2/3。

2、LCD Controller

LCD 控制器用于发送视频数据到外部的 TFT LCD 并生成必要的控制信号,如: VSYNC、HSYNC、VCLK等。LCD 控制器通过 16 个 24-bit RGB FIFO 与叠加控制器交换数据。LCD 控制器可以通过寄存器设置 LCD 电源引脚的状态。

3、TV Controller

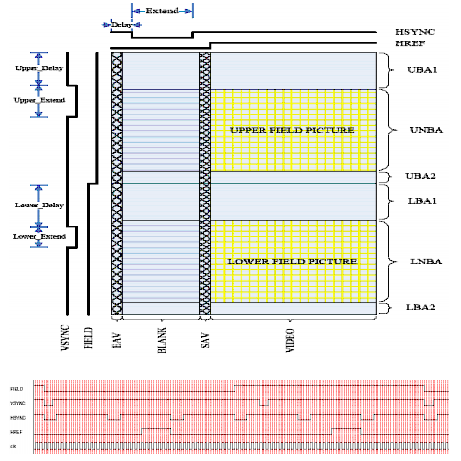

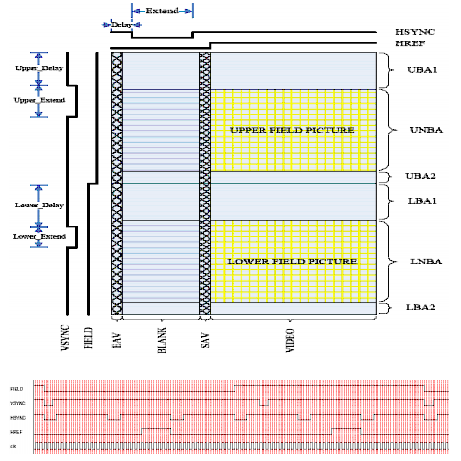

电视控制器将 RGB FIFO 中的 RGB 数据转换成 YCbCr 数据并发送到外部电视机的编码芯片,YCbCr 数据将被加入消隐区数据并打包,使之与 ITU-R BT 601/656 接口格式兼容。接口发送数据的频率依赖于图像的大小,接口信号由视频数据和必须的控制信号(VSYNC、HSYNC、HREF、FIELD等)组成。内部的 RGB -> YCbCr 颜色空间转换矩阵系数可以由软件配置。当前支持两种接口时序:一、行从消隐区开始,二、行从 EAV(有效视频结束) 开始。第二种时序如下图所示(SAV-有效视频开始):

TV 控制器支持 4 种类型的数据格式:ITU656 8-bit YCbCr422、ITU601 8-bit YCbCr422、ITU601 16-bit YCbCr422、ITU601 24-bit RGB888。当输出数据宽度为 8-bit 时,2 个时钟周期发送一个像素的数据。

4、双屏显示

当前支持4种工作模式:复制模式(本地显示为主,远程显示通过缩放获得)、高清模式(远程高清、本地为缩放所得)、扩展模式(将同一个 buffer 里面的内容分割显示)、独立模式(各自的不同内容)。

二、HDMI 学习笔记

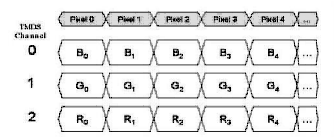

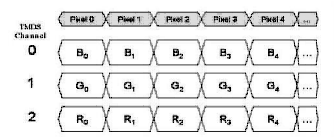

HDMI - 高清晰度多媒体接口 ,接口使用 5V 电压驱动,采用了 Silicon Image 公司发明的 TMDS (时间最小化差分信号)传输技术,视频信号的 R、G、B、H、V 五种信号都用 TDMS 技术编码。每一个标准的 HDMI 连接,都包含了 3 路用于传输数据的 TMDS 传输通道,还有 1 路独立的 TMDS 时钟通道。在一个时钟周期内,每个 TMDS 通道都能传送 10bit 的数据流,这个数据流可以由若干种不同的编码格式构成。TMDS 对每个像素点种的 RGB 三原色分别按 8bit 编码,如下图所示:

一般来说,HDMI 传输的编码格式中要包含 视频数据 (HDMI1.3版本前每个像素采用24bit)、 控制数据 和 数据岛 (数据岛中包含音频数据和附加信息数据,如纠错码等)。TDMS 每个通道在传输时要包含一个 2bit 的控制数据、8bit 的视频数据或者 4bit 的数据包,在 HDMI 信息传输过程中,可以分为 三个阶段 :视频数据传输周期、控制数据传输周期和数据岛传输周期,如下图所示:

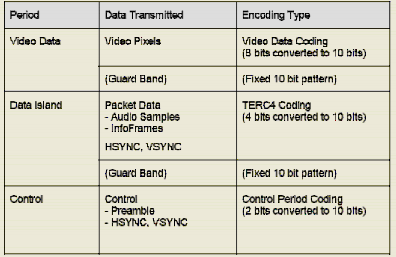

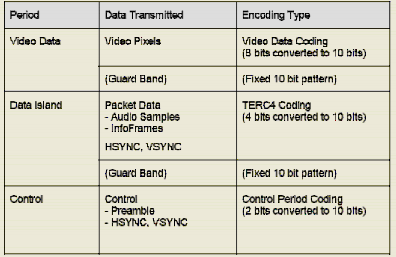

下表展示在数据传输中每种操作模式的编码类型

HDMI 1.0 的带宽为 4.96Gbps(25MHz - 165MHz),HDMI 1.3 为10.2Gbps(340M),计算公式如下:

在广播电视行业使用的 TV 格式中,支持标清格式的 480i、480p(含 16:9 格式)、576i、576p规格以及高清 HDTV 中的 720p、1080i、1080p 规格。 在 HDMI 中还加入了版权保护机制 - HDCP (高带宽数字内容保护),是在使用数字格式进行传输信号的基础上,再加入一层版权认证保护技术。

HDMI Source 和 Sink 的 上电协商过程 :

a、 Source 设备上电后会检测 HPD 引脚是否被上拉到 2V 以上

b、 Source 设备通过 DDC(显示数据通道) 读取 EDID(增强扩展显示识别数据) 的信息以确定 Sink 能支持的分辨率

c、 Source 设备检测 TMDS 信号是否被上拉到 3.3V

d、 Source 设备输出目前设置的分辨率的信号到 Sink 端

TMDS 技术差分信号上拉电压为 +3.3V(由 Sink 提供),差分信号的逻辑摆幅在 800-1200mV 之间,实际电压摆幅可以在 150-1200mV 之间变化。CEC 引脚为消费电子控制通道,用于控制视听设备工作。

* synopsys - IP 核提供商,为大多数芯片公司节省了大量的时间和资源,其 IP 核包括:HDMI、DDR、MIPI、PCIe、SATA、USB、Ethernet 等,并提供了相应的验证软件包。平台 HDMI 接口就是采用的 synopsys 公司的 IP 核,编程指南 《DesignWare Cores HDMI Transmitter Controller Databook》 - DWC_hdmi_tx。软件流程主要为两个阶段:

1、Initialization

a、Wait for Hot Plug Detect(HPD)

b、Configure VGA DVI Video Mode

c、Read Sink's E-EDID

2、Configuration

d、Configure Video Mode

e、Configure Audio Mode

f、Configure Infoframes

g、Configure HDCP

在 a 阶段,通过向寄存器 PHY_CONF0.PDZ 写 1 让 HDMI TX PHY HPD Detector 上电,然后检测 HPD 状态位,当 HPD = 1 时,即代表检测到了 Sink 设备,便可进入 b 阶段。

在 b 阶段,需要先用 DVI 模式 向接收器发送视频数据,因为 读取 E-EDID 的操作需要视频数据来提供准确的时钟源,发送数据的分辨率为 VGA(640 x 480p),所有的发送器和接收器都必须支持这个分辨率,因为这个分辨率的数据率最低。HDMI TX PHY 有一个 内部 PLL 用于产生 TMDS 信号的时钟 。

在 c 阶段,发送器将会通过 E-DDC 通道从接收器读取 E-EDID 数据,这个数据包含了接收器支持的音频和视频功能,并保存在接收器的存储器中。E-DDC 通道基于 I2C 协议 ,所以发送器有一个 I2C 主控制器。E-DDC 扩展读 操作流程 如下:设置从设备 I2C 地址 -> 设置 I2C 段地址 -> 设置 I2C 段指针 -> 开启扩展读功能 -> 读取结果寄存器。

在 d 阶段,将会 匹配发送器和接收器 都支持的视频模式,然后首先关闭 HDMI TX PHY Detector 以免接收器产生异常行为,接着开始配置发送器的视频模式(选择视频输入映射模式 -> 设置视频信号时序 -> 选择 HDMI 或者 DVI 模式 -> 使能 PHY 内部 PLL -> 复位 PHY -> 通过读取 TX_PHY_LOCK 判断配置是否正确完成)

在 e 阶段,将会为 HDMI 输出配置 音频模式 (DVI 模式没有音频输出),可选的模式有:I2S、S/PDIF、HBR、DMA、GPA 。

HDMI 功能单元

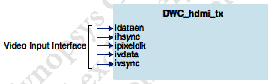

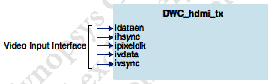

a、Video Input Interface - 视频输入接口,接收来自 IDS 的视频数据,其引脚如下图所示:

其中 ivdata 为 48bits,其他都为 1bit,可以看到这是一个典型的视频信号接口。

b、Audio Input Interface - 音频输入接口,接收来自处理器的音频数据

c、System and Slave Register Interface - 系统和从设备寄存器接口,控制内部寄存器的读写

d、E-DDC Interface - 扩展显示数据通道接口,该功能通过 I2C 协议实现,这个接口就是 I2C 时钟和数据读写引脚

e、CEC Interface - 消费电子控制接口,使用 32.768 KHz 的时钟

f、HDCP Encryption Engine - 高带宽数字内容保护加密引擎

g、Scan Test Interface - 扫描测试接口

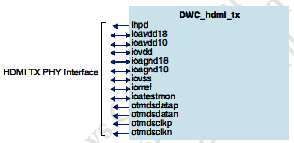

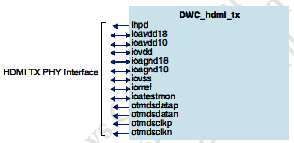

h、HDMI TX PHY Interface - HDMI 发送器物理接口,大部分信号将会连接到外部引脚,示意图如下:

其中 ihpd 连接到 HPD 引脚,otmdsdatap、otmdsdatan 连接到外部的 3 路数据传输引脚,otmdsclkp、otmdsclkn 连接到外部时钟引脚。

i、HDMI 3D TX PHY Interface - HDMI 3D 发送器物理接口

j、HDMI HEAC PHY Interface - HDMI 以太网和音频回传通道物理接口

HDMI 函数解析

* 初始化阶段

hdmi_probe() - hdmi 探测函数,建立了内核线程 hdmi_wk 以及4个工作队列 hdmi_handler_wk(中断后续处理)、hpd_wk(热插拔检测)、edid_wk(E_EDID读取和解析)、check_wk(当前状态检测),可以设置 items - P_HDMI_DIRECT 是否直接输出 hdmi 信号

hdmi_initialize() - hdmi 内存、中断等资源管理

api_Initialize() - 初始化 VGA 显示参数,以及 hdmi 模块内的寄存器、PHY 等

* 连接检测阶段

hdmi_handler() - 中断函数,当 HPD 引脚状态变化时启动,然后启动 hdmi_handler_wk()

hdmi_handler_wk() - 处理 hpd_on、hpd_off、ddc_i2c 等事件,如果是 hpd_on,则开始读取 E-EDID

api_EventHandler() - api 层事件处理器,根据 api_mCurrentState 即当前状态做出相应处理,当 E-EDID 读取完成后,启动 edid_EventHandler() 解析,其中重要的函数有 edid_ParseBlock()、dtd_Parse()、dtd_Fill(),解析完成后设置 api_mCurrentState = API_EDID_READ

hdmi_update_strategy() - E-EDID 解析完成后根据 PHY 和 sink 支持的分辨率选取合适的输出格式

hdmi_config() - 根据输出格式通过 hdmi_params_config() 配置视频、音频等参数,然后通过 api_Configure() 配置相关寄存器打开 hdmi 信号输出

1、Overlay Controller

图像数据格式和4窗口融合由叠加控制器处理。叠加控制器可以根据窗口的中断生成一个窗口时隙,用户可以根据时隙中断更新帧缓冲的数据,比如:播放视频的时候。通常,视频的解码速度为 30 fps,LCD 的刷新率为 60-70 Hz,叠加控制器采用两路 PWM 定时器中断来避免潜在的风险。同步的过程如下图所示:

时隙中断同步于 PWM_INT2/3 和 VSYNC,在第一阶段:时隙中断产生后,下一帧的视频数据可以安全的解码并写入 buffer1,因为此时叠加控制器是从 buffer0 中读取视频数据到 LCD。同样的,在第二阶段 buffer0 的内容可以被更新。注:在使用窗口时隙中断时必须先设置好 PWM_INT2/3。

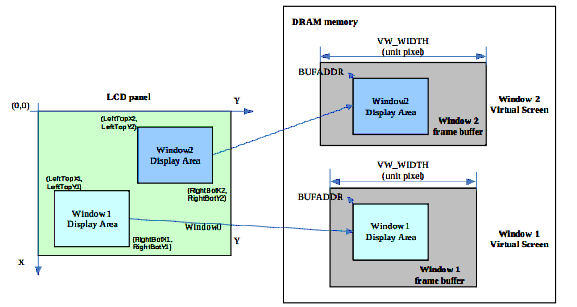

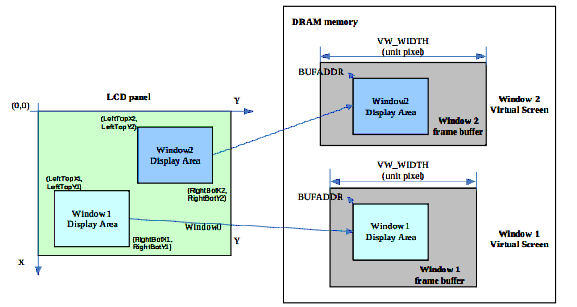

窗口坐标和虚拟显示示意图如下:

2、LCD Controller

LCD 控制器用于发送视频数据到外部的 TFT LCD 并生成必要的控制信号,如: VSYNC、HSYNC、VCLK等。LCD 控制器通过 16 个 24-bit RGB FIFO 与叠加控制器交换数据。LCD 控制器可以通过寄存器设置 LCD 电源引脚的状态。

3、TV Controller

电视控制器将 RGB FIFO 中的 RGB 数据转换成 YCbCr 数据并发送到外部电视机的编码芯片,YCbCr 数据将被加入消隐区数据并打包,使之与 ITU-R BT 601/656 接口格式兼容。接口发送数据的频率依赖于图像的大小,接口信号由视频数据和必须的控制信号(VSYNC、HSYNC、HREF、FIELD等)组成。内部的 RGB -> YCbCr 颜色空间转换矩阵系数可以由软件配置。当前支持两种接口时序:一、行从消隐区开始,二、行从 EAV(有效视频结束) 开始。第二种时序如下图所示(SAV-有效视频开始):

TV 控制器支持 4 种类型的数据格式:ITU656 8-bit YCbCr422、ITU601 8-bit YCbCr422、ITU601 16-bit YCbCr422、ITU601 24-bit RGB888。当输出数据宽度为 8-bit 时,2 个时钟周期发送一个像素的数据。

4、双屏显示

当前支持4种工作模式:复制模式(本地显示为主,远程显示通过缩放获得)、高清模式(远程高清、本地为缩放所得)、扩展模式(将同一个 buffer 里面的内容分割显示)、独立模式(各自的不同内容)。

二、HDMI 学习笔记

HDMI - 高清晰度多媒体接口 ,接口使用 5V 电压驱动,采用了 Silicon Image 公司发明的 TMDS (时间最小化差分信号)传输技术,视频信号的 R、G、B、H、V 五种信号都用 TDMS 技术编码。每一个标准的 HDMI 连接,都包含了 3 路用于传输数据的 TMDS 传输通道,还有 1 路独立的 TMDS 时钟通道。在一个时钟周期内,每个 TMDS 通道都能传送 10bit 的数据流,这个数据流可以由若干种不同的编码格式构成。TMDS 对每个像素点种的 RGB 三原色分别按 8bit 编码,如下图所示:

一般来说,HDMI 传输的编码格式中要包含 视频数据 (HDMI1.3版本前每个像素采用24bit)、 控制数据 和 数据岛 (数据岛中包含音频数据和附加信息数据,如纠错码等)。TDMS 每个通道在传输时要包含一个 2bit 的控制数据、8bit 的视频数据或者 4bit 的数据包,在 HDMI 信息传输过程中,可以分为 三个阶段 :视频数据传输周期、控制数据传输周期和数据岛传输周期,如下图所示:

下表展示在数据传输中每种操作模式的编码类型

HDMI 1.0 的带宽为 4.96Gbps(25MHz - 165MHz),HDMI 1.3 为10.2Gbps(340M),计算公式如下:

带宽 = 系统时钟频率 x 数据量 = 340MHz x 10bit = 3.4Gbit x 3 = 10.2Gbit

* 典型的 720p@60Hz 时钟频率为 74.25MHz,1080p@60Hz 时钟频率为 148.5MHz

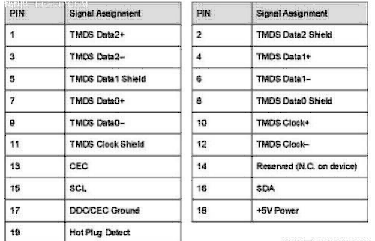

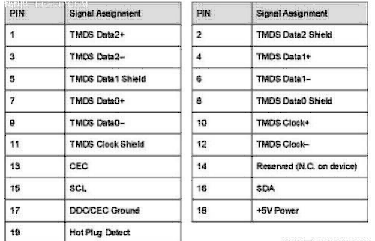

Type A 型 HDMI 接口引脚定义如下图所示:

在广播电视行业使用的 TV 格式中,支持标清格式的 480i、480p(含 16:9 格式)、576i、576p规格以及高清 HDTV 中的 720p、1080i、1080p 规格。 在 HDMI 中还加入了版权保护机制 - HDCP (高带宽数字内容保护),是在使用数字格式进行传输信号的基础上,再加入一层版权认证保护技术。

HDMI Source 和 Sink 的 上电协商过程 :

a、 Source 设备上电后会检测 HPD 引脚是否被上拉到 2V 以上

b、 Source 设备通过 DDC(显示数据通道) 读取 EDID(增强扩展显示识别数据) 的信息以确定 Sink 能支持的分辨率

c、 Source 设备检测 TMDS 信号是否被上拉到 3.3V

d、 Source 设备输出目前设置的分辨率的信号到 Sink 端

TMDS 技术差分信号上拉电压为 +3.3V(由 Sink 提供),差分信号的逻辑摆幅在 800-1200mV 之间,实际电压摆幅可以在 150-1200mV 之间变化。CEC 引脚为消费电子控制通道,用于控制视听设备工作。

* synopsys - IP 核提供商,为大多数芯片公司节省了大量的时间和资源,其 IP 核包括:HDMI、DDR、MIPI、PCIe、SATA、USB、Ethernet 等,并提供了相应的验证软件包。平台 HDMI 接口就是采用的 synopsys 公司的 IP 核,编程指南 《DesignWare Cores HDMI Transmitter Controller Databook》 - DWC_hdmi_tx。软件流程主要为两个阶段:

1、Initialization

a、Wait for Hot Plug Detect(HPD)

b、Configure VGA DVI Video Mode

c、Read Sink's E-EDID

2、Configuration

d、Configure Video Mode

e、Configure Audio Mode

f、Configure Infoframes

g、Configure HDCP

在 a 阶段,通过向寄存器 PHY_CONF0.PDZ 写 1 让 HDMI TX PHY HPD Detector 上电,然后检测 HPD 状态位,当 HPD = 1 时,即代表检测到了 Sink 设备,便可进入 b 阶段。

在 b 阶段,需要先用 DVI 模式 向接收器发送视频数据,因为 读取 E-EDID 的操作需要视频数据来提供准确的时钟源,发送数据的分辨率为 VGA(640 x 480p),所有的发送器和接收器都必须支持这个分辨率,因为这个分辨率的数据率最低。HDMI TX PHY 有一个 内部 PLL 用于产生 TMDS 信号的时钟 。

在 c 阶段,发送器将会通过 E-DDC 通道从接收器读取 E-EDID 数据,这个数据包含了接收器支持的音频和视频功能,并保存在接收器的存储器中。E-DDC 通道基于 I2C 协议 ,所以发送器有一个 I2C 主控制器。E-DDC 扩展读 操作流程 如下:设置从设备 I2C 地址 -> 设置 I2C 段地址 -> 设置 I2C 段指针 -> 开启扩展读功能 -> 读取结果寄存器。

在 d 阶段,将会 匹配发送器和接收器 都支持的视频模式,然后首先关闭 HDMI TX PHY Detector 以免接收器产生异常行为,接着开始配置发送器的视频模式(选择视频输入映射模式 -> 设置视频信号时序 -> 选择 HDMI 或者 DVI 模式 -> 使能 PHY 内部 PLL -> 复位 PHY -> 通过读取 TX_PHY_LOCK 判断配置是否正确完成)

在 e 阶段,将会为 HDMI 输出配置 音频模式 (DVI 模式没有音频输出),可选的模式有:I2S、S/PDIF、HBR、DMA、GPA 。

在 f 阶段,将会为 HDMI 输出设置辅助信息,以告知接收器收到的视频和音频数据的格式等信息。

HDMI 功能单元

a、Video Input Interface - 视频输入接口,接收来自 IDS 的视频数据,其引脚如下图所示:

其中 ivdata 为 48bits,其他都为 1bit,可以看到这是一个典型的视频信号接口。

b、Audio Input Interface - 音频输入接口,接收来自处理器的音频数据

c、System and Slave Register Interface - 系统和从设备寄存器接口,控制内部寄存器的读写

d、E-DDC Interface - 扩展显示数据通道接口,该功能通过 I2C 协议实现,这个接口就是 I2C 时钟和数据读写引脚

e、CEC Interface - 消费电子控制接口,使用 32.768 KHz 的时钟

f、HDCP Encryption Engine - 高带宽数字内容保护加密引擎

g、Scan Test Interface - 扫描测试接口

h、HDMI TX PHY Interface - HDMI 发送器物理接口,大部分信号将会连接到外部引脚,示意图如下:

其中 ihpd 连接到 HPD 引脚,otmdsdatap、otmdsdatan 连接到外部的 3 路数据传输引脚,otmdsclkp、otmdsclkn 连接到外部时钟引脚。

i、HDMI 3D TX PHY Interface - HDMI 3D 发送器物理接口

j、HDMI HEAC PHY Interface - HDMI 以太网和音频回传通道物理接口

HDMI 函数解析

* 初始化阶段

hdmi_probe() - hdmi 探测函数,建立了内核线程 hdmi_wk 以及4个工作队列 hdmi_handler_wk(中断后续处理)、hpd_wk(热插拔检测)、edid_wk(E_EDID读取和解析)、check_wk(当前状态检测),可以设置 items - P_HDMI_DIRECT 是否直接输出 hdmi 信号

hdmi_initialize() - hdmi 内存、中断等资源管理

api_Initialize() - 初始化 VGA 显示参数,以及 hdmi 模块内的寄存器、PHY 等

* 连接检测阶段

hdmi_handler() - 中断函数,当 HPD 引脚状态变化时启动,然后启动 hdmi_handler_wk()

hdmi_handler_wk() - 处理 hpd_on、hpd_off、ddc_i2c 等事件,如果是 hpd_on,则开始读取 E-EDID

api_EventHandler() - api 层事件处理器,根据 api_mCurrentState 即当前状态做出相应处理,当 E-EDID 读取完成后,启动 edid_EventHandler() 解析,其中重要的函数有 edid_ParseBlock()、dtd_Parse()、dtd_Fill(),解析完成后设置 api_mCurrentState = API_EDID_READ

hdmi_update_strategy() - E-EDID 解析完成后根据 PHY 和 sink 支持的分辨率选取合适的输出格式

hdmi_config() - 根据输出格式通过 hdmi_params_config() 配置视频、音频等参数,然后通过 api_Configure() 配置相关寄存器打开 hdmi 信号输出

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小惠珠哦/article/detail/996862

推荐阅读

相关标签