热门标签

热门文章

当前位置: article > 正文

基于FPGA的画面分割器_fpga hdmi 分割

作者:空白诗007 | 2024-08-17 06:28:54

赞

踩

fpga hdmi 分割

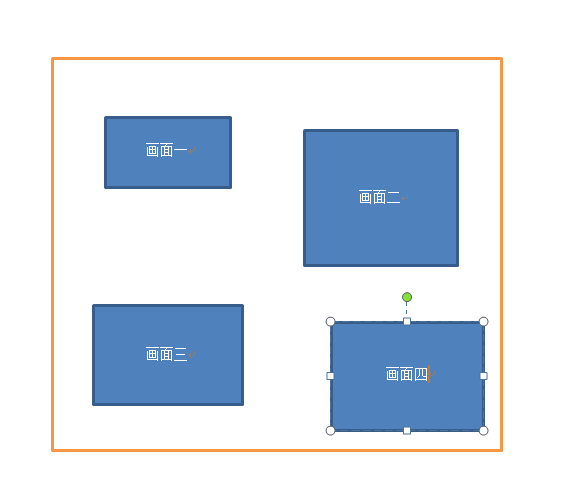

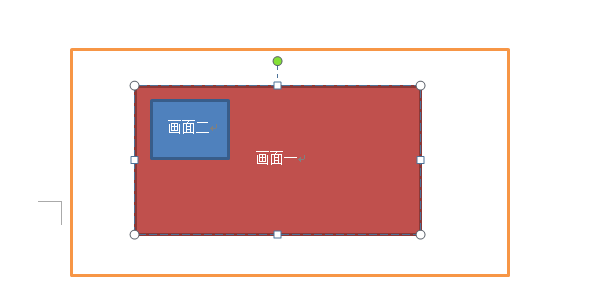

为了在一个显示器上看到多个 画面,可以将任何 四路 最高分辨率为 1080P的视频以任意方式组合为一路1080p@60hz高清输出。有下面几种场景:

四画面:

画中画:

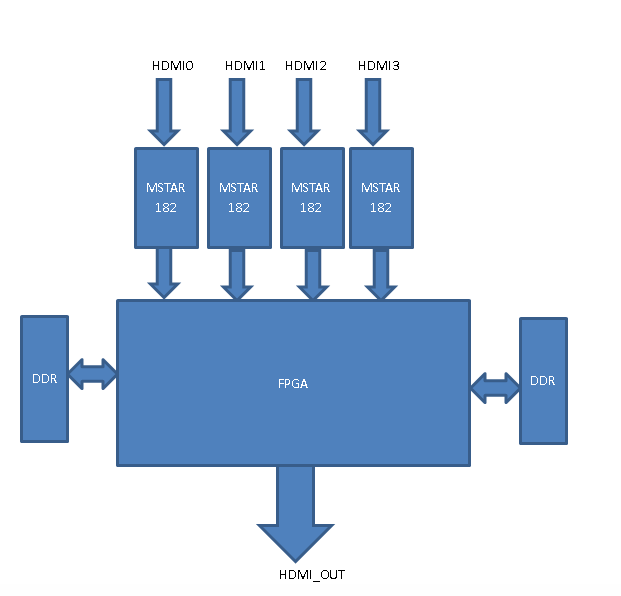

然后分析一下本产品的架构:

四路 HDMI 信号 经过 PHY转为 TTL到FPGA , FPGA 接收到数据后, 先缩放进入到DDR, 然后根据相应的位置去读DDR, 根据屏幕的位置去显示视频信号。这样就可以实现 多画面。当然也可以实现画中画。

当用DDR1 的时候 ,DDR1 跑 170MHZ. 两片 16位的DDR 合成一片32位的DDR.因为 进来的 视频信号是 1920 x 1080 @60hz. 它的时钟频率为 148.5MHZ.

我们来算一下DDR的利用效率。

视频信号的带宽 = 148.5 MHZ X 4 X 2 X16 = 19008Mhz.

DDR的带宽 = 170MHZ X 32 X 2 X 2 = 21760MHZ.

所有 利用效率 = 19008 / 21760 = 87.3%.

这样DDR的利用效率还是可以的

本文内容由网友自发贡献,转载请注明出处:【wpsshop博客】

推荐阅读

相关标签