热门标签

热门文章

- 1细品以太坊的“四棵树”——Merkle Patricia Trie_merkle patricia tree (mpt)

- 2AI智能缺陷检测系统_ai模型 文字缺陷检测

- 3应急学院物联网应急安全产教融合基地解决方案

- 4代码随想录-二叉树

- 5【软件测试面试】要你介绍项目-如何说?完美面试攻略..._测试面试怎么讲项目内容

- 6如何使用Java开发Android应用?_安卓java

- 7WebRTC源码之摄像头视频数据采集源码分析_网络摄像头项目 源码

- 8MongoDB 基础浅谈

- 9php取图片格式,php判断图片格式的简单方法

- 10【嵌入式】基于STC89C52RC的51单片机学习(五)——感应开关盖垃圾桶_stc89c52rc项目

当前位置: article > 正文

【FPGA创新设计竞赛——2022紫光同创杯】1、“基于 RISC-V 处理器的软硬件系统设计”赛题介绍_fpga创新设计大赛 简介

作者:小蓝xlanll | 2024-05-14 16:41:02

赞

踩

fpga创新设计大赛 简介

一、 开发方向

基于 RISC-V 处理器的软硬件系统设计

设计要求

本赛题要求在紫光同创 PGL22G 开发板上设计实现基于RISC-V 指令集架构的处理器,充分利用板卡硬件资源以提高CPU 运行性能。鼓励在软件生态上对设计进行适配和支持。

设计指标

- (1) CoreMark 跑分作为测试基准程序,参赛团队可通过优化 CPU 微架构或编译器,以提升跑分结果。依据 CPU 设计复杂度、支持的指令集数和跑分结果综合考量作品。

- (2) 加分项:运行操作系统(可以是开源的 RTOS,也可以自行设计)。

- (3) 加分项:鼓励移植适配 MicroPython 和 Arduino 进行开发。

- (4) 加分项:鼓励自行设计 IDE,集成全套 RISC-V 工具链,实现从 C 语言带汇编链接的全部功能,并实现下载和调试功能。

作品提交注意事项

提供项目设计报告, 至少包含以下内容:

- (1) 硬件设计的完整工程文件和设计报告

- (2) CoreMark 跑分结果和 PPA 等关键技术指标

- (3) 扩展部分的设计报告

- (4) 演示作品

二、 考核标准

鼓励创新,根据设计复杂度(包括系统架构、外围接口丰富性等)、实用性、应用范围、商业价值等进行综合评分。

三、 平台借用

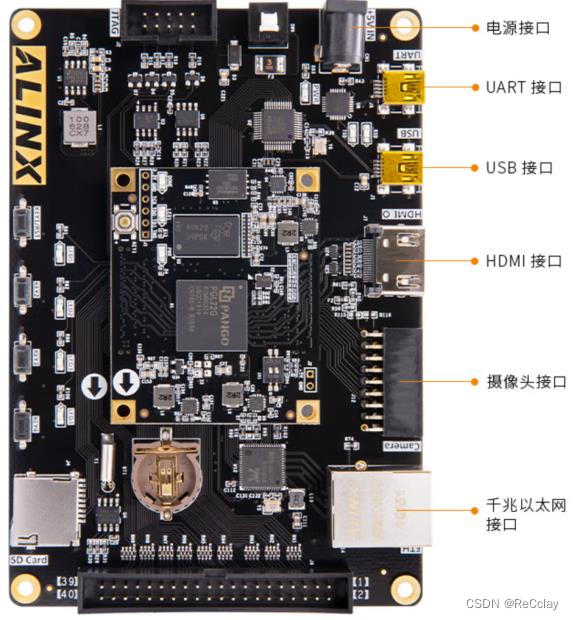

- 1、 初审通过队伍紫光同创提供 PGL22 为核心的开发板(如下);

- 2、 参赛队伍可采用自制或自备第三方以紫光同创 FPGA芯片为核心的开发板。

四、 竞赛支持

FPGA 紫光同创指导 QQ 群: 906793557

为更好的支持参赛选手,除开发板配套的教程和 QQ 群支持以外,紫光同创还将持续更新配套教学视频, 部分目录如下:

- 1.1、 PDS 开发技巧——从零入门

- 1.2、实战紫光 FPGA——PDS 集成开发环境

- 1.3、 PDS 工程仿真技巧——行为仿真

- 1.4、基于 PDS 的在线逻辑分析调试

- 1.5、 Logos2 系列 IO 资源介绍

- 1.6、 Logos2 系列 ADC 资源介绍

- 1.7、 Logos2 系列 Clock 资源介绍

- 1.8、 Logos2 系列 Serdes 资源介绍

- 1.9、 Logos2 系列硬件设计指南

- ···

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/569265

推荐阅读

相关标签