- 1高手过招, 为什么 Redis Cluster 是16384个槽位?_redis16384个槽

- 2android约束布局ConstraintLayout_constraintlayout 比例

- 3oracle常见单词_数据库中常用的英文单词

- 4Python与Excel的完美结合:操作技巧与自动化应用

- 5完全卸载Android Studio的方法_android studio卸载

- 6【前端Vue3】——JQuery知识点总结(超详细)

- 7(openstack搭建)openstack云平台部署-详细完整教程_openstack部署

- 8往届生和应届生、同等学历复试材料有什么区别?

- 9文本识别综述 <软件学报_王建新等、中国图象图形学报_刘崇宇等>

- 10探索FTP:原理、实践与安全优化_ftp s3存储

FPGA必备基础7:verilog的6种延迟操作_fpga仿真中使用的延迟

赞

踩

目录

(1)定义

顾名思义,就是FPGA语句的延迟问题。在这里,有三种赋值方式:连续赋值、阻塞赋值、非阻塞赋值;有两种延迟方式:正规延迟、内定延迟。两者相乘则共有6种方式延迟。

(2)延迟种类

2.1 连续赋值

2.1.1 正规延迟

1)代码

assign #5 C = A +B。

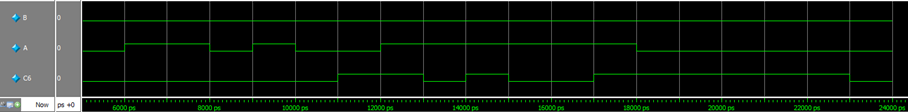

2)波形图

在 T 时刻执行到该语句时,等待 5 个时间单位,然后计算等号右边的值赋给 C,5个时刻后C的值是T+5 时刻 A、B 的值。

注意,若在等待过程中 A、 B 的值发生变化再次触发 assign 块,根据 assign块的门级时序模型特点,仿真器会撤销先前的等待事件,然后重新执行语句。但当变化脉冲小于 5 个时间单位时,等待事件会被撤销,该脉冲将不起作用。(这里的图使用的是别的博主的图,侵权删)

2.1.2 内定延迟

1)代码

assign C = #5 A +B。

2)波形图

在 T 时刻执行到该语句时,计算等号右边的值,等待 5 个时间单位后赋给 C。使用的 A 、B 的值是 T 时刻的值。

若在等待过程中 A 、B 的值发生变化再次触发 assign块,根据 assign块的门级时序模型特点,仿真器会撤销先前的等待事件,然后重新执行语句。

但当变化脉冲小于 5 个时间单位时,等待事件会被撤销,该脉冲将不起作用。该种方式有记忆属性,与连续赋值原则不符,为非法语句,编译不能通过。

2.2 阻塞赋值

2.2.1 正规延迟

1)代码

always @(*) #5 C = A +B;

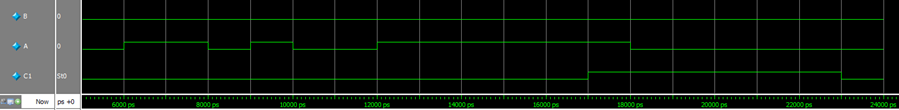

2)波形图

在 T 时刻执行到该语句时,等待5个时间单位,然后计算等号右边的值阻塞赋给 C。使用的 A B 的值是 T+5 时刻的值。

注意,若在等待过程中 A 、B 的值发生变化再次触发 always 块,根据 always块的过程时序模型特点,此时还在等待过程,always 语句还未执行结束,不会开始新一轮的事件,仿真器不会对敏感列表反应。仿真器会忽略延迟时间段的数据变化。(这里的图使用的是别的博主的图,侵权删)

2.2.2 内定延迟

1)代码

always @(*) C = #5 A +B;

2)波形图

在 T 时刻执行到该语句时,计算等号右边的值,等待 5 个时间单位后赋给 C。使用的 A、 B 的值是 T 时刻的值。

若在等待过程中 A、B 的值发生变化再次触发 always块,根据 always块的过程时序模型特点,由于赋值方式为阻塞赋值,此时 always 语句还未执行结束,不会开始新一轮的事件,仿真器不会对敏感列表反应。仿真器忽略延迟时间段的数据变化。(这里的图使用的是别的博主的图,侵权删)

2.3 非阻塞赋值

2.3.1 正规延迟

1)代码

always @(*) #5 C <= A +B;

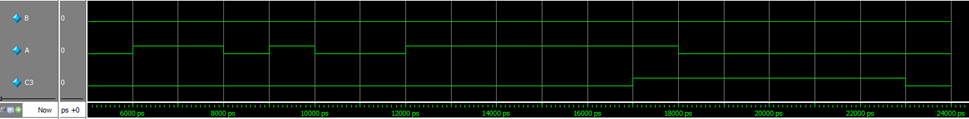

2)波形图

在 T 时刻执行到该语句时,等待 5 个时间单位,然后计算等号右边的值阻塞赋给 C。使用的 A、B 的值是 T+5 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 always块,根据 always块的过程时序模型特点,此时还在等待过程,always 语句还未执行结束,不会开始新一轮的事件,仿真器不会对敏感列表反应。仿真器忽略延迟时间段的数据变化。(这里的图使用的是别的博主的图,侵权删)

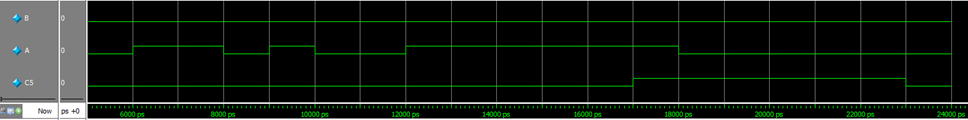

2.3.2 内定延迟

1)代码

always @(*) C <= #5 A +B;

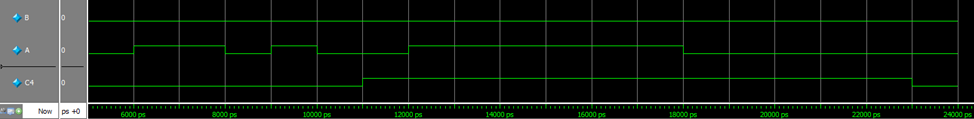

2)波形图

在 T 时刻执行到该语句时,计算等号右边的值,等待 5 个时间单位后赋给 C。使用的 A、B 的值是 T 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 always块,根据 always块的过程时序模型特点,由于赋值方式为非阻塞赋值,将赋值事件放进事件队列后,always 语句执行结束,等待下一次的触发,触发来到时开始新一轮的事件。同时,仿真器接受延迟时间段的数据变化,输入的变化延迟会全部反应在输出上。(这里的图使用的是别的博主的图,侵权删)