热门标签

热门文章

- 1yolo v5显示中文标签乱码解决_yolo检测标签乱码与只显示编号

- 2JAVA项目【仿牛客网面试总结】【分章节】_仿牛客网面试笔记

- 3使用Qt Creator进行代码分析_qt 代码分析

- 4Unknown host ‘dl.google.com‘. You may need to adjust the proxy settings in

- 5def __init__(self)和def __init__(self, 参数1,参数2,···,参数n)的用法详解

- 6vue中如何使用富文本详细讲解_vue 富文本

- 7高中毕业从汽修转行自学Python,月薪翻了三倍,我有一份转行秘籍分享给你_高中毕业自学python

- 8python类型转换方法_Numpy数据类型转换astype,dtype的方法

- 9Java关键字大冒险:深入浅出地理解Java的精髓

- 10啥移动硬盘格式能更好兼容Windows和Mac系统 NTFS格式苹果电脑不能修改 paragon ntfs for mac激活码_mac os 和windows系统都能用的硬盘格式

当前位置: article > 正文

[FPAG开发]使用Vivado创建第一个程序_vivado的main源文件

作者:小蓝xlanll | 2024-06-16 02:16:18

赞

踩

vivado的main源文件

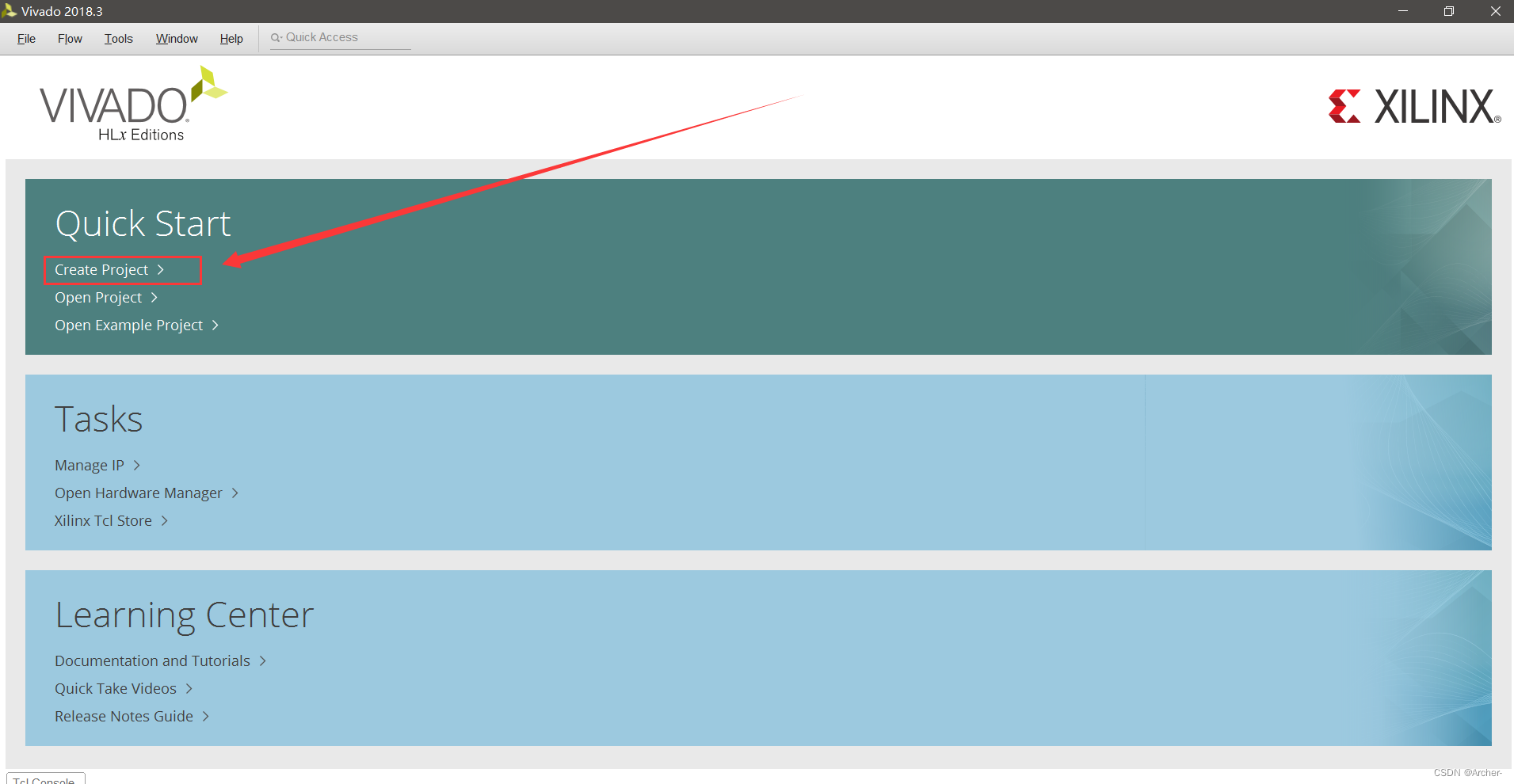

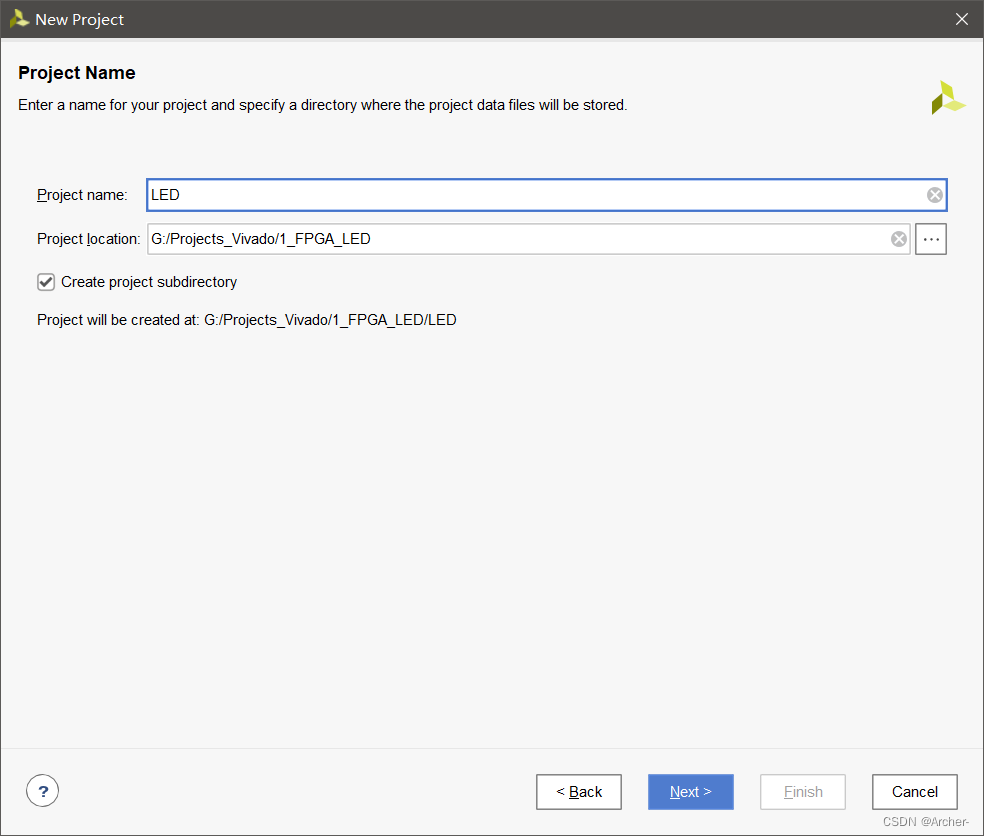

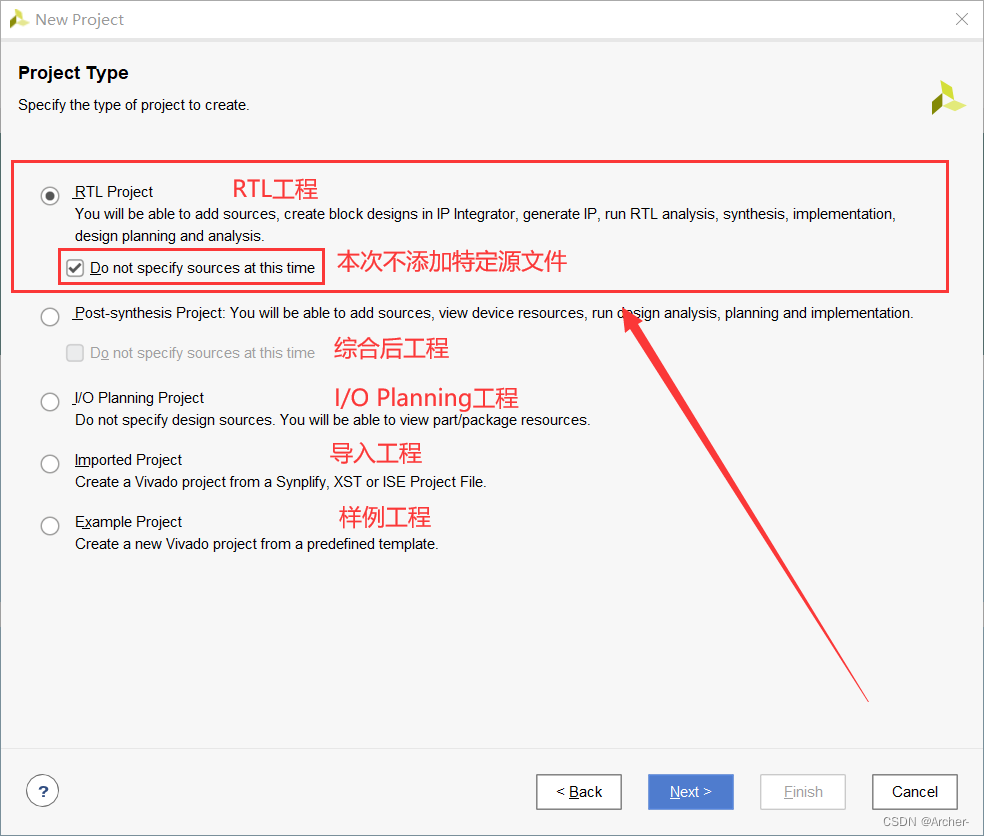

1 打开Vivado软件,新建项目

选择一个纯英文路径

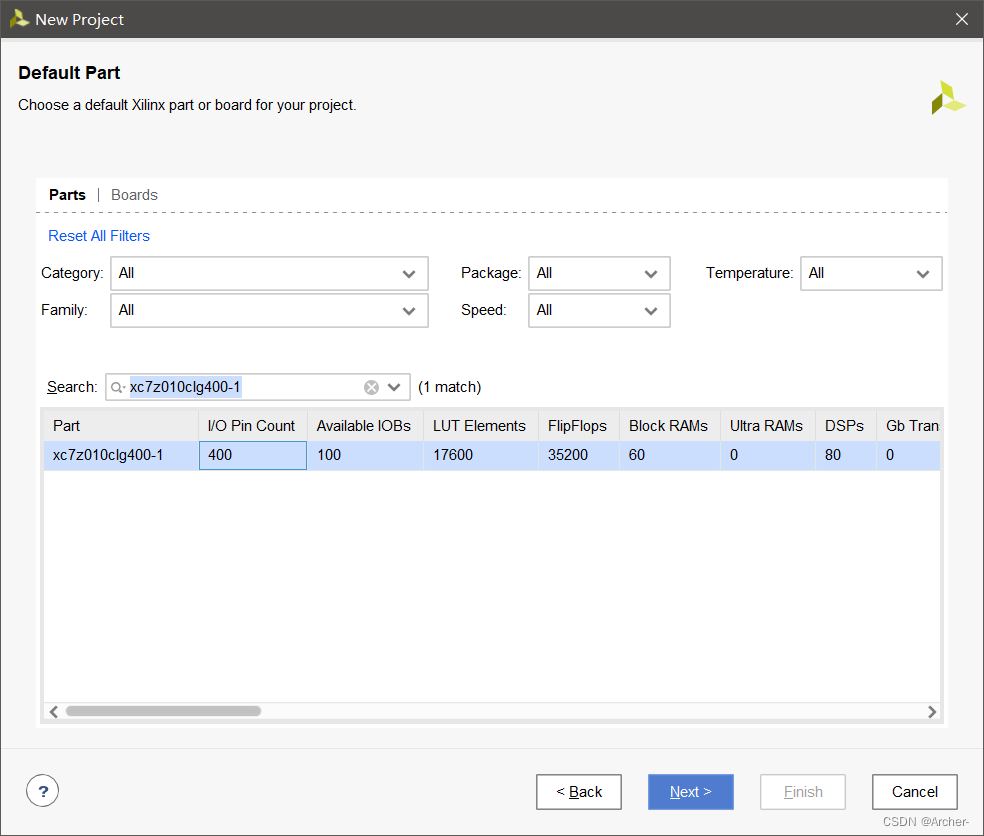

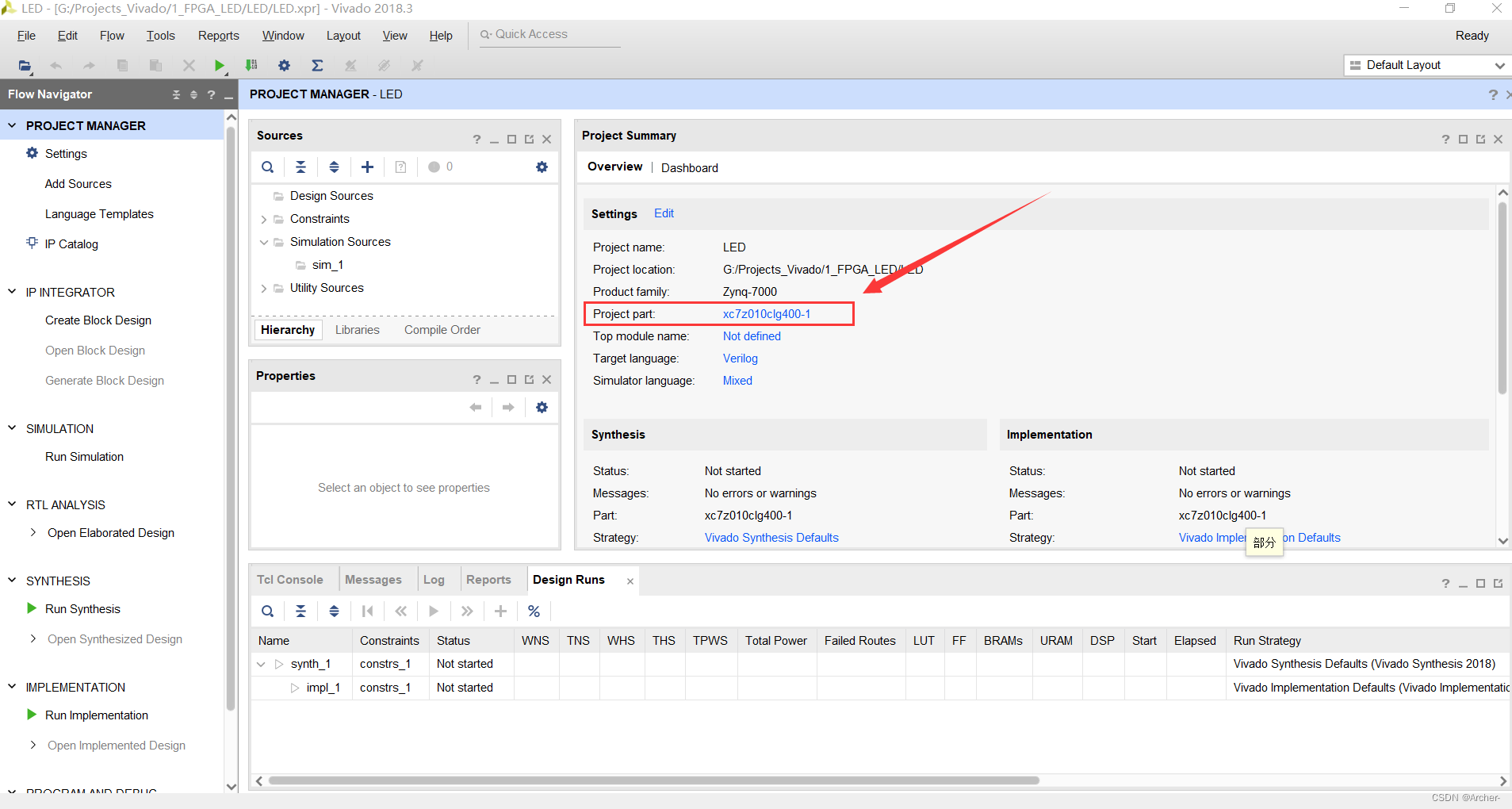

选择合适的型号

| 产品 | 型号 |

|---|---|

| ZYNQ-7010 | xc7z010clg400-1 |

| ZYNQ-7020 | xc7z010clg400-2 |

如果型号选错,可以单击这里重新选择

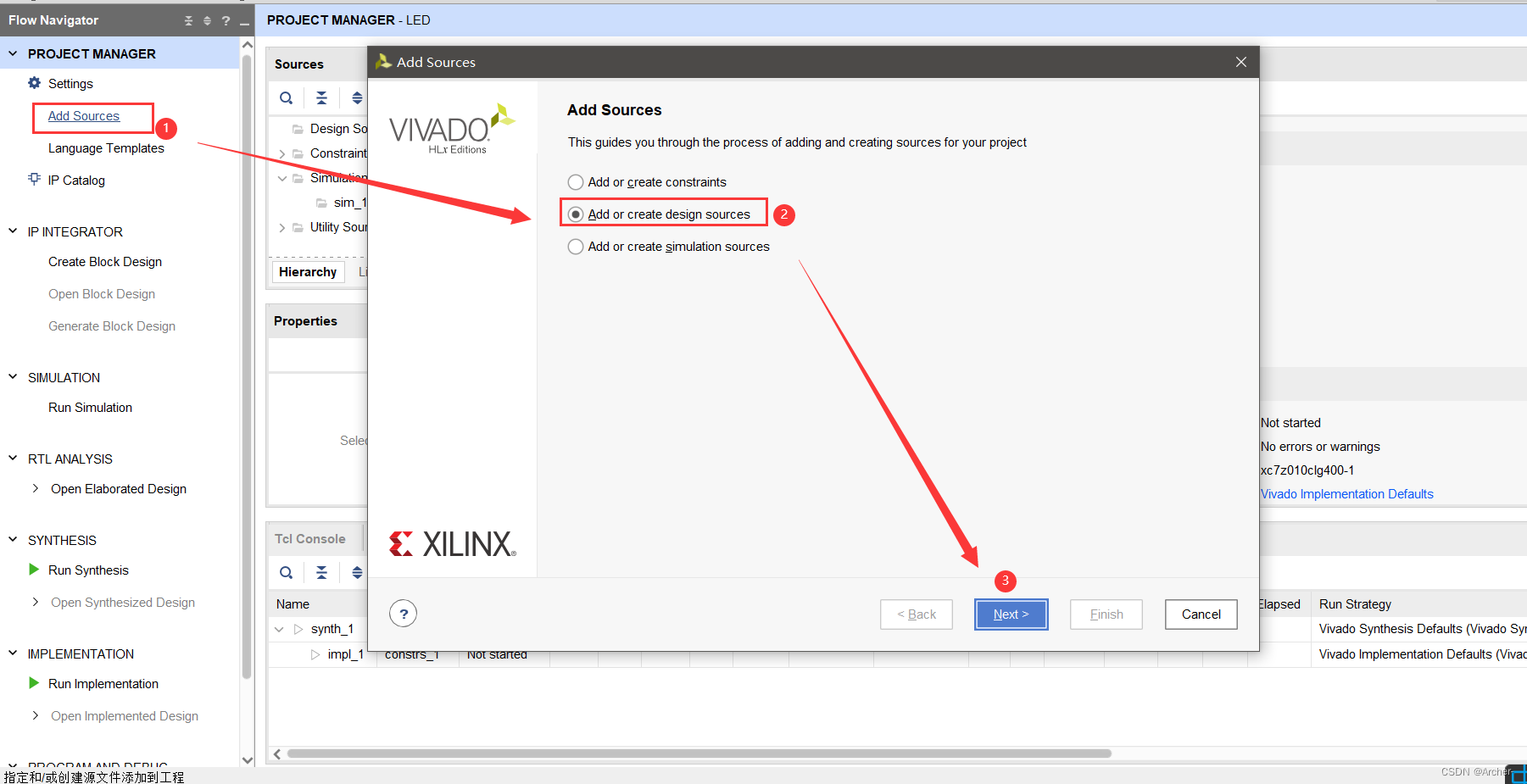

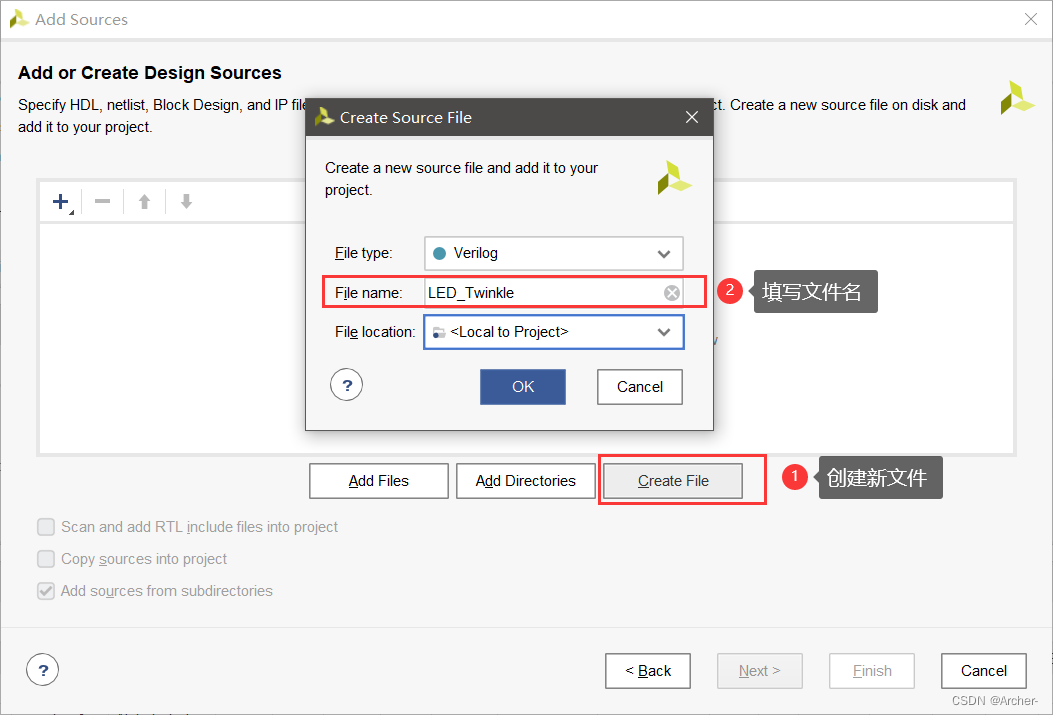

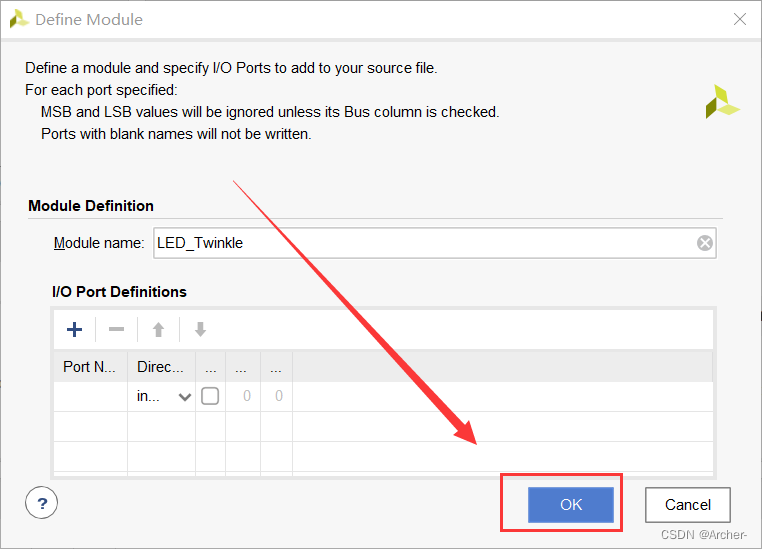

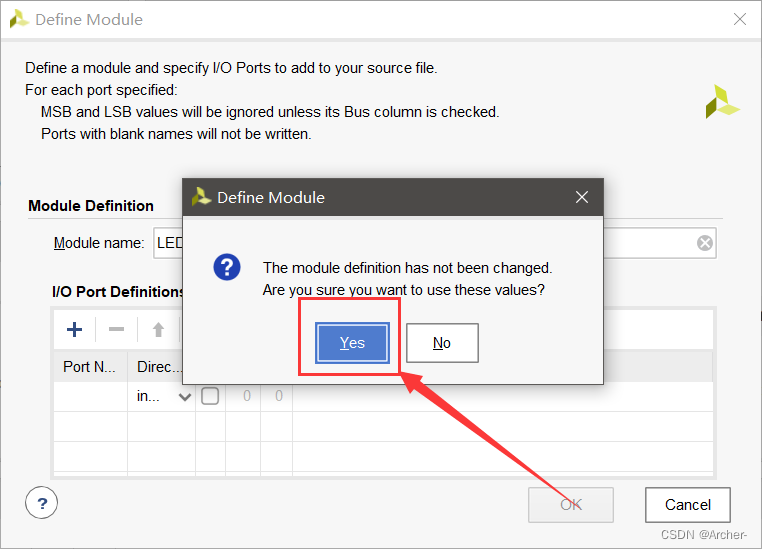

2 创建工程源文件

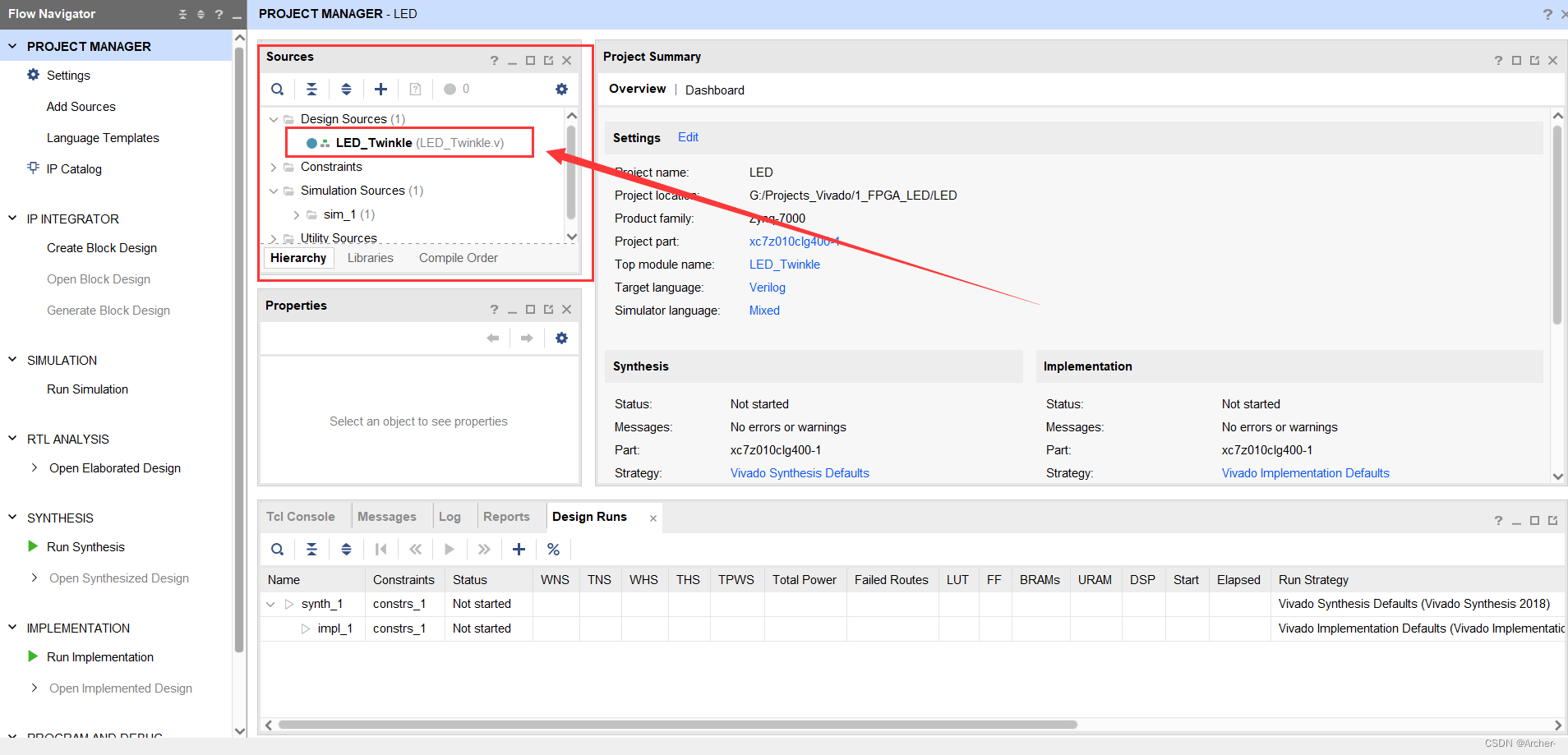

可以看到文件创建成功

双击文件打开,插入代码

module led_twinkle( input sys_clk , //系统时钟 input sys_rst_n, //系统复位,低电平有效 output [1:0] led //LED灯 ); //reg define reg [25:0] cnt ; //***************************************************** //** main code //***************************************************** //对计数器的值进行判断,以输出LED的状态 assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ; //assign led = (cnt < 26'd5) ? 2'b01 : 2'b10 ; //仅用于仿真 //计数器在0~5000_000之间进行计数 always @ (posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) cnt <= 26'd0; else if(cnt < 26'd5000_0000) // else if(cnt < 26'd10) //仅用于仿真 cnt <= cnt + 1'b1; else cnt <= 26'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

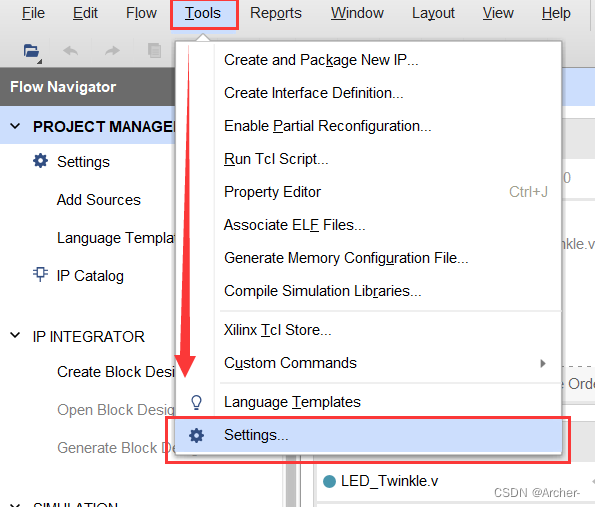

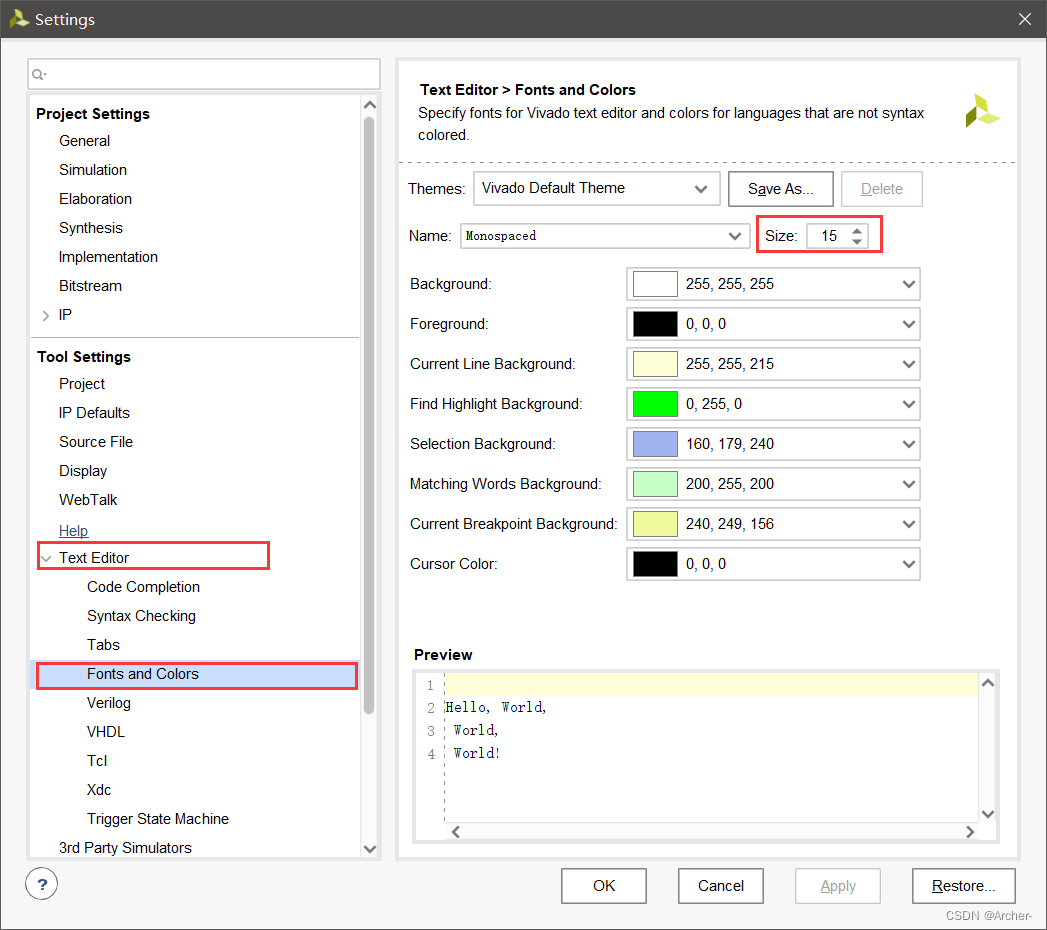

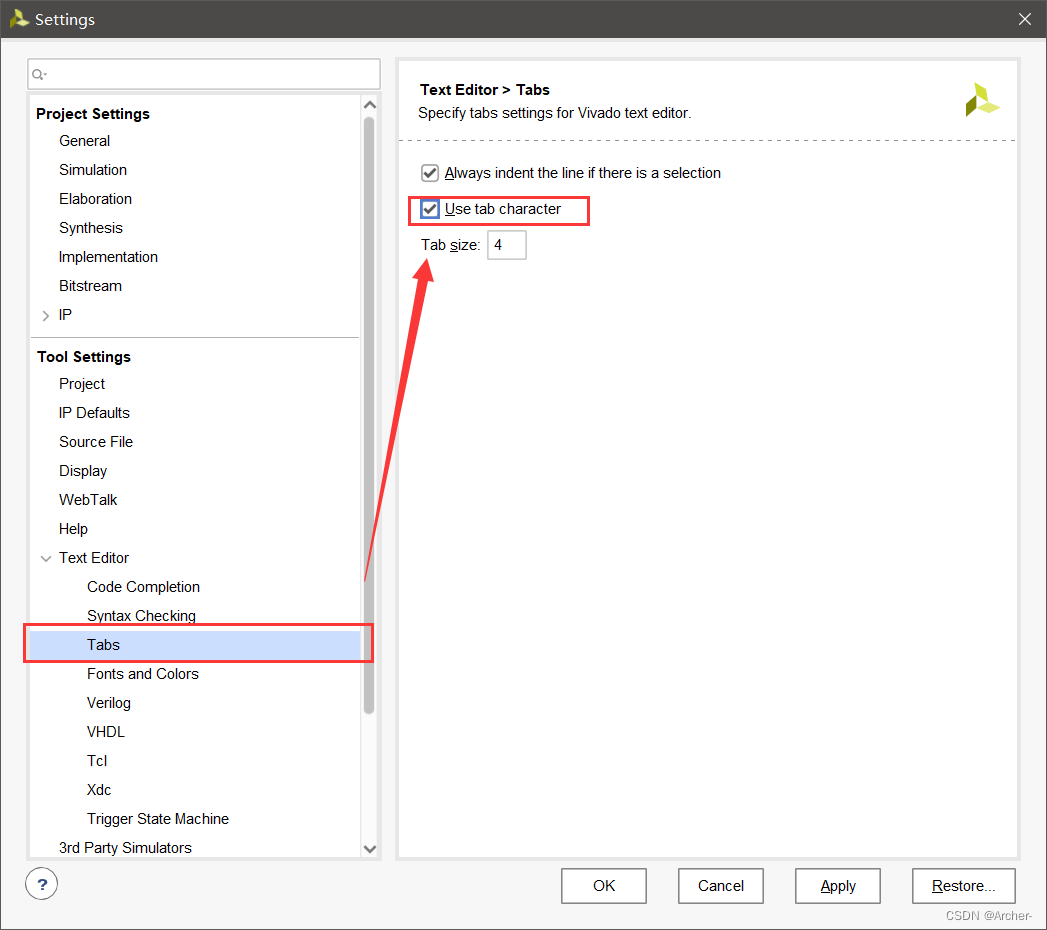

设置字体和缩进

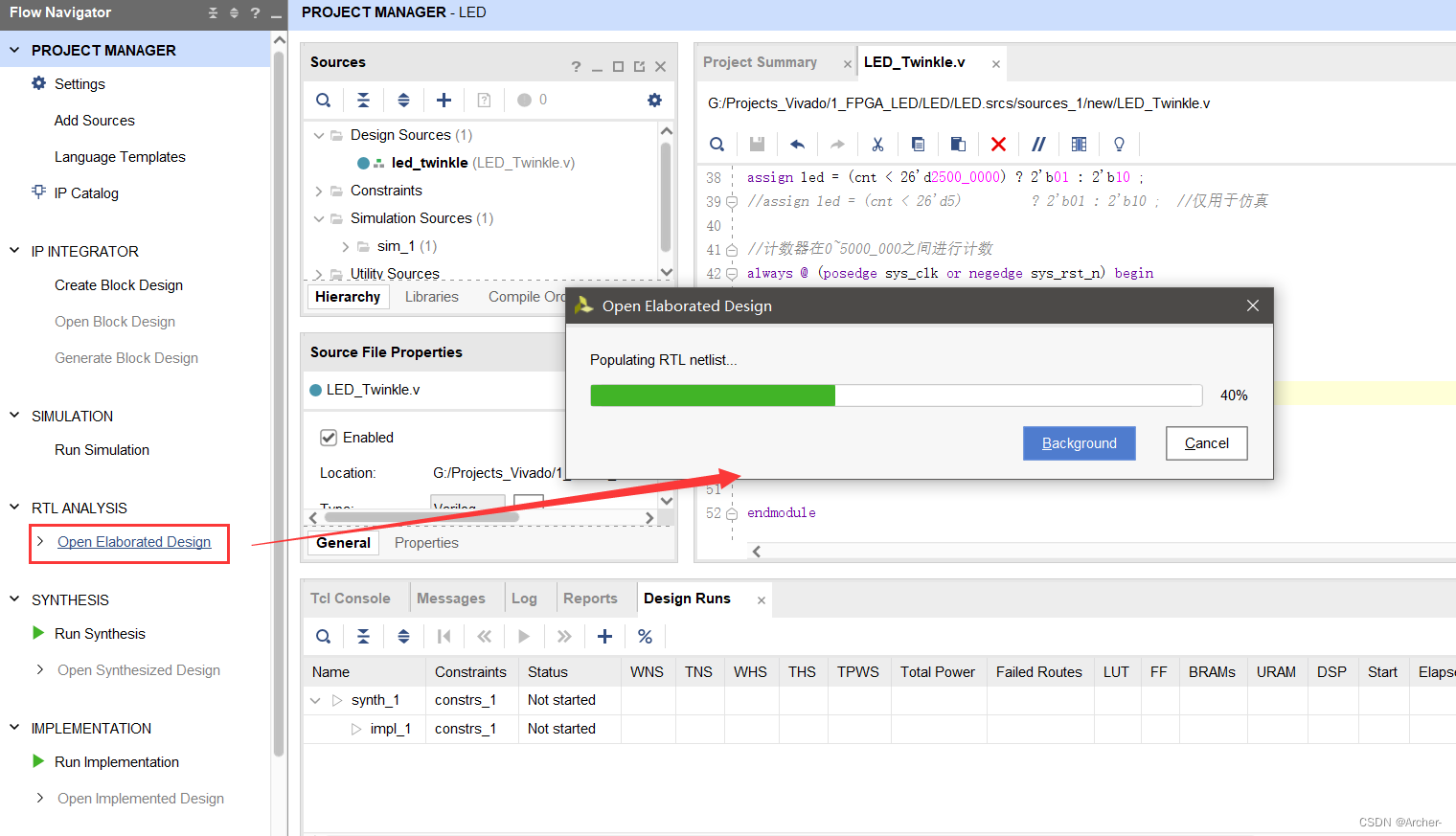

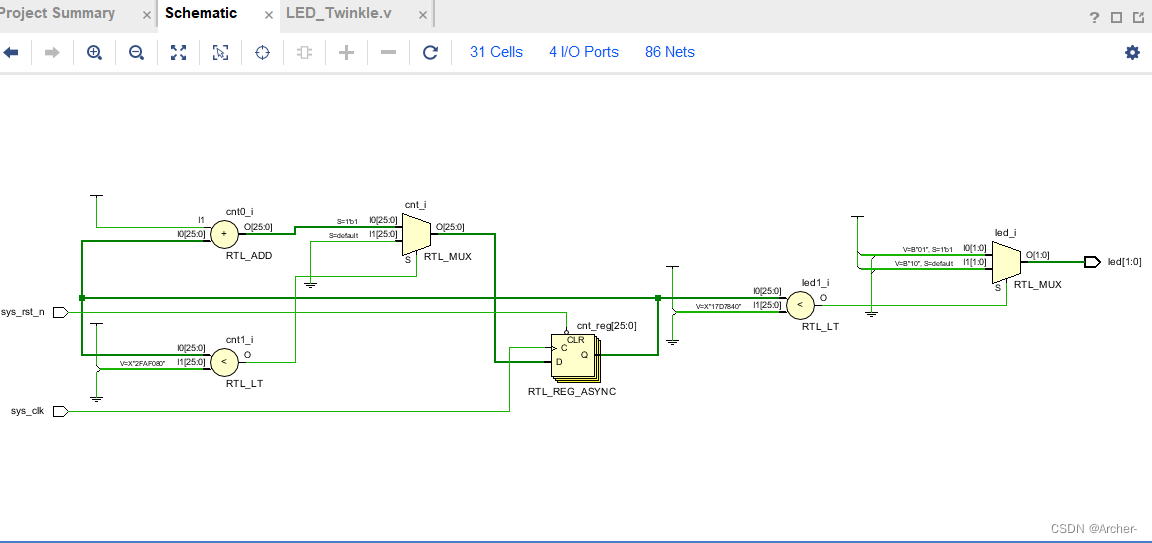

3 RTL分析综合

软件会生成一个原理图

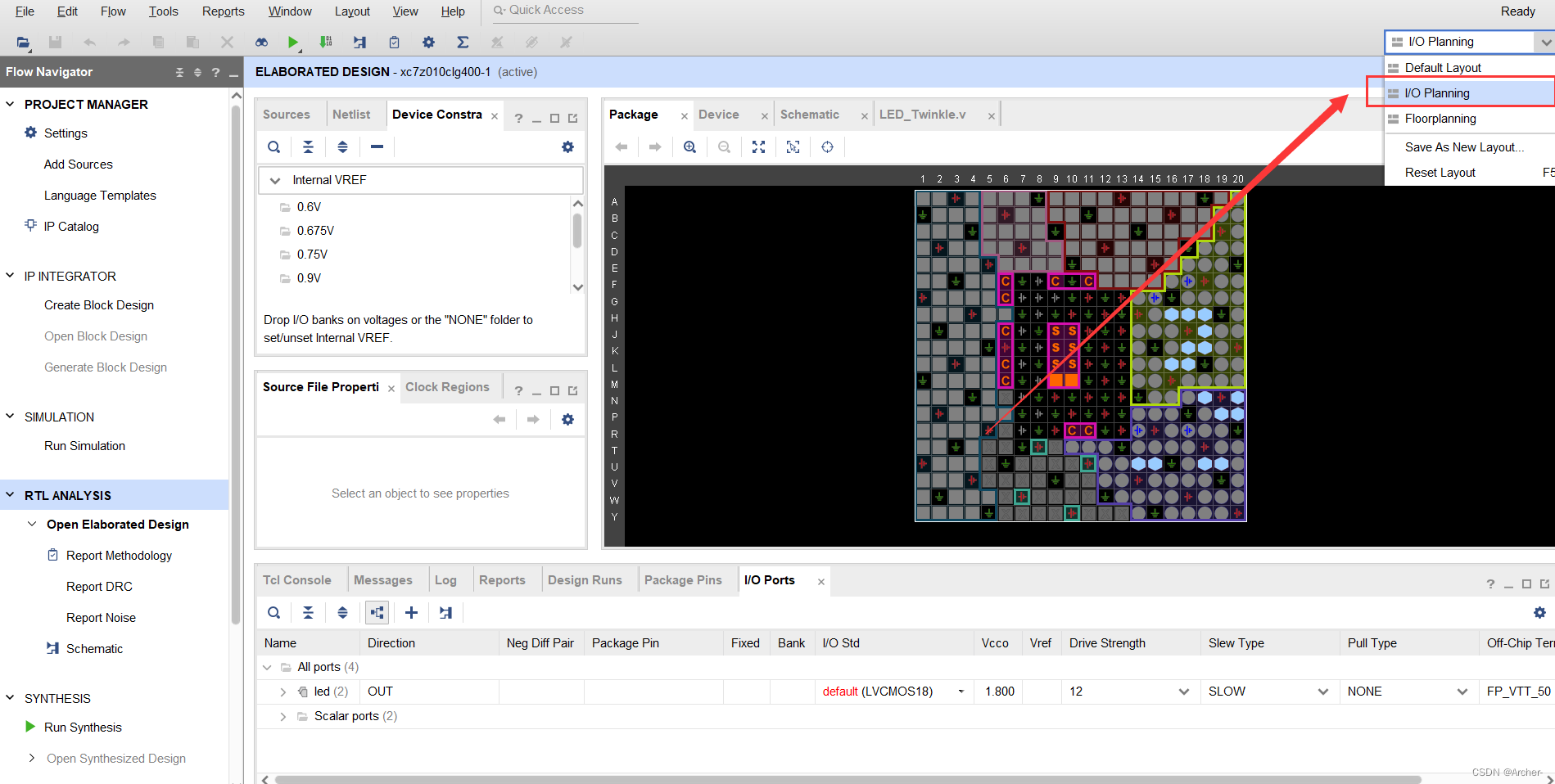

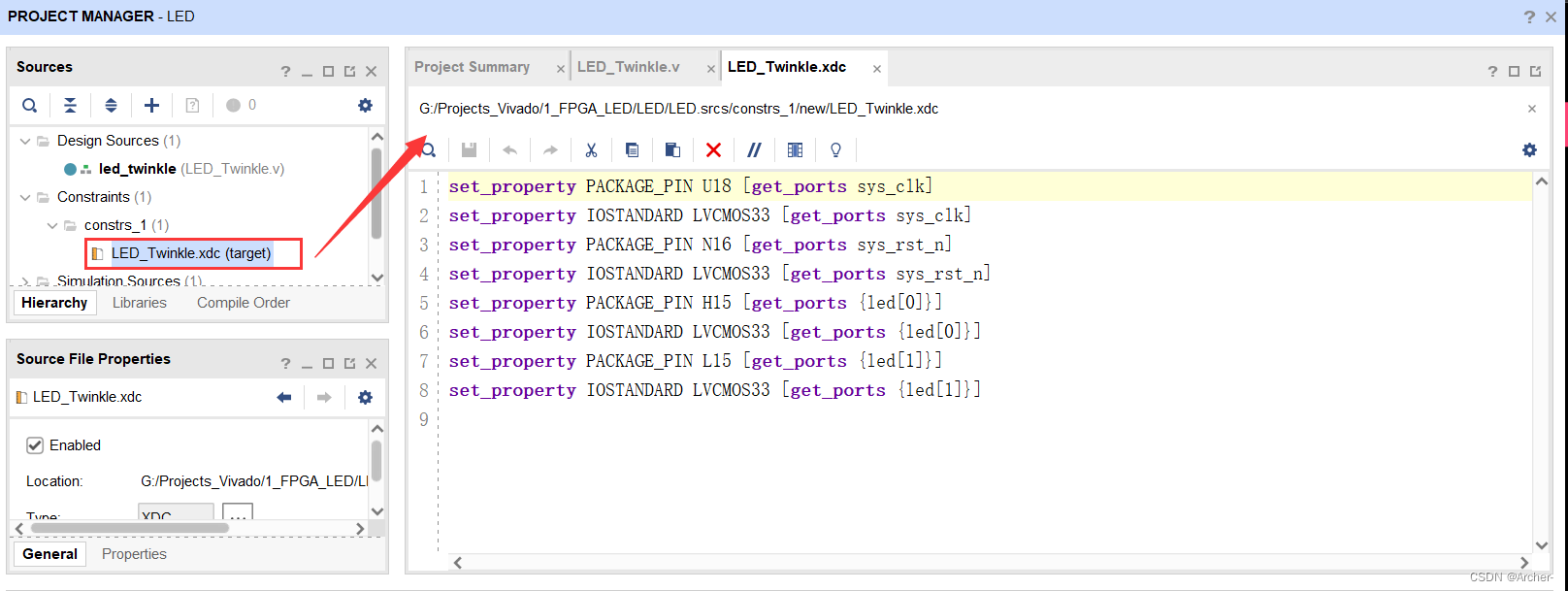

4 引脚约束

| 参数 | 类型 | 对应的FPGA引脚 | I/O std | 备注 |

|---|---|---|---|---|

| sys_clk | IN | U18 | LVCMOS33 | 3.3V电平 |

| sys_rst_n | IN | N16 | LVCMOS33 | 3.3V电平 |

| led[0] | OUT | L15 | LVCMOS33 | 3.3V电平 |

| led[1] | OUT | H15 | LVCMOS33 | 3.3V电平 |

配置如图所示

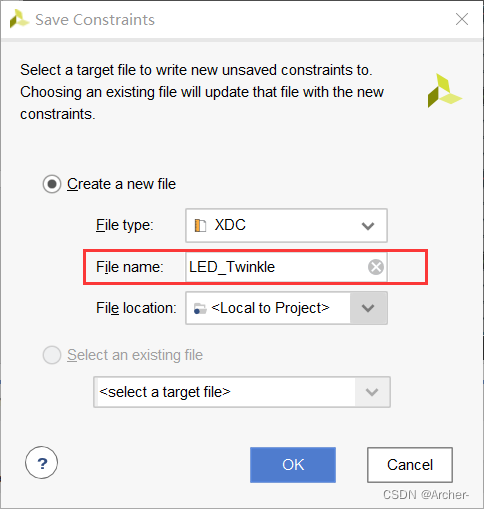

然后使用Ctrl+S保存

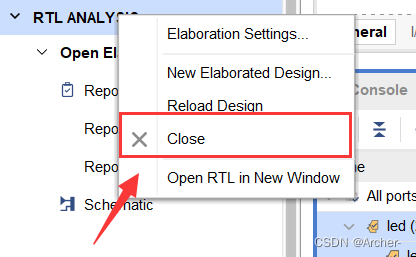

关闭界面

XDC文件保存了I/O约束的信息

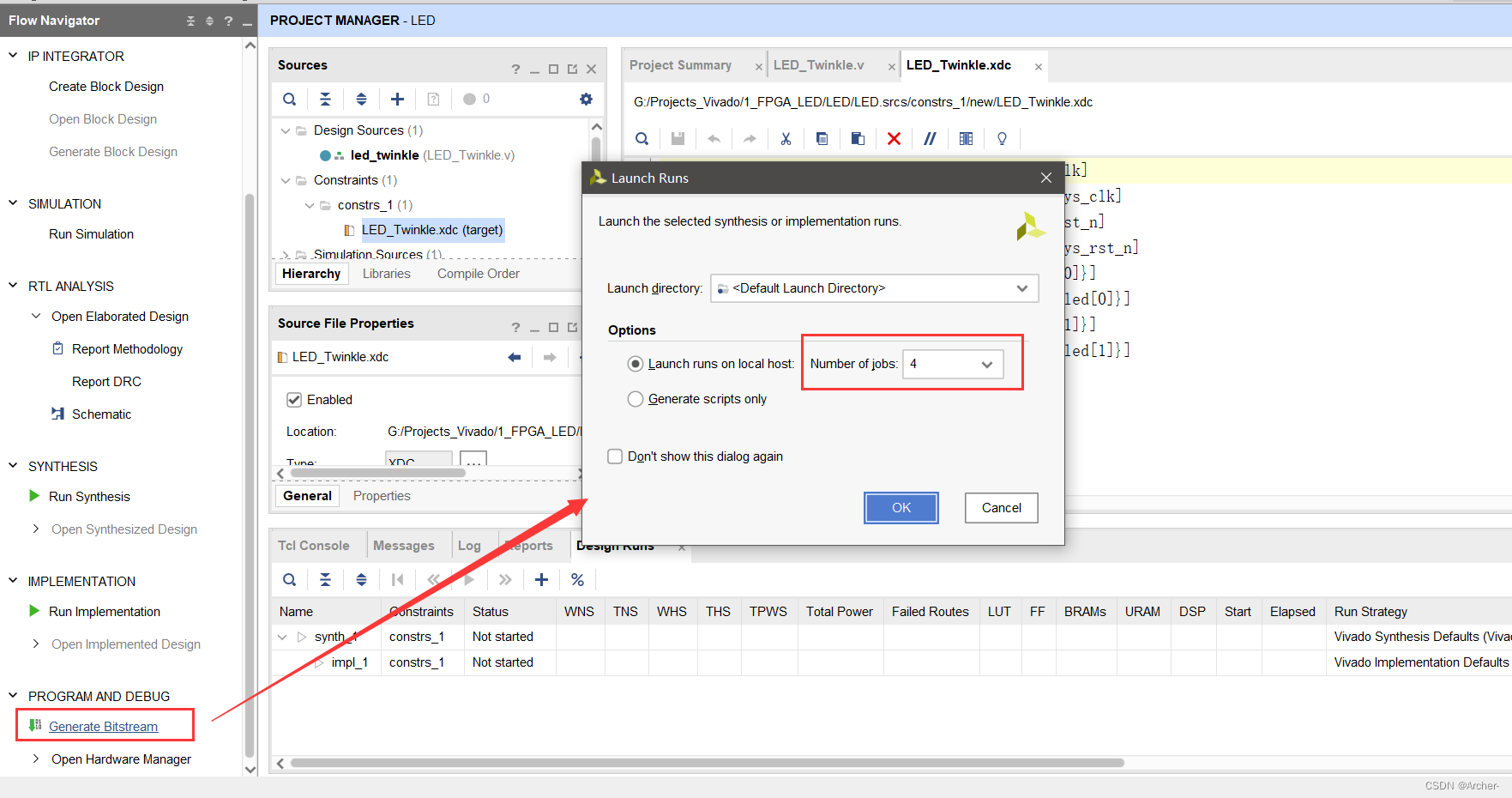

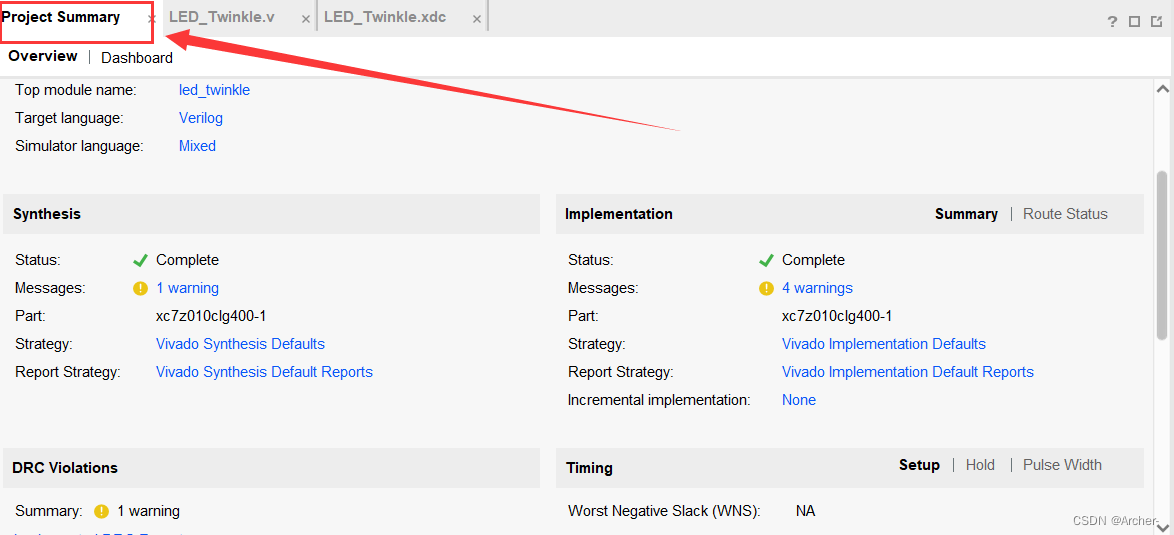

5 生成比特流

在这里可以看到进度

完成之后会出现一个框框,点击Cancel即可

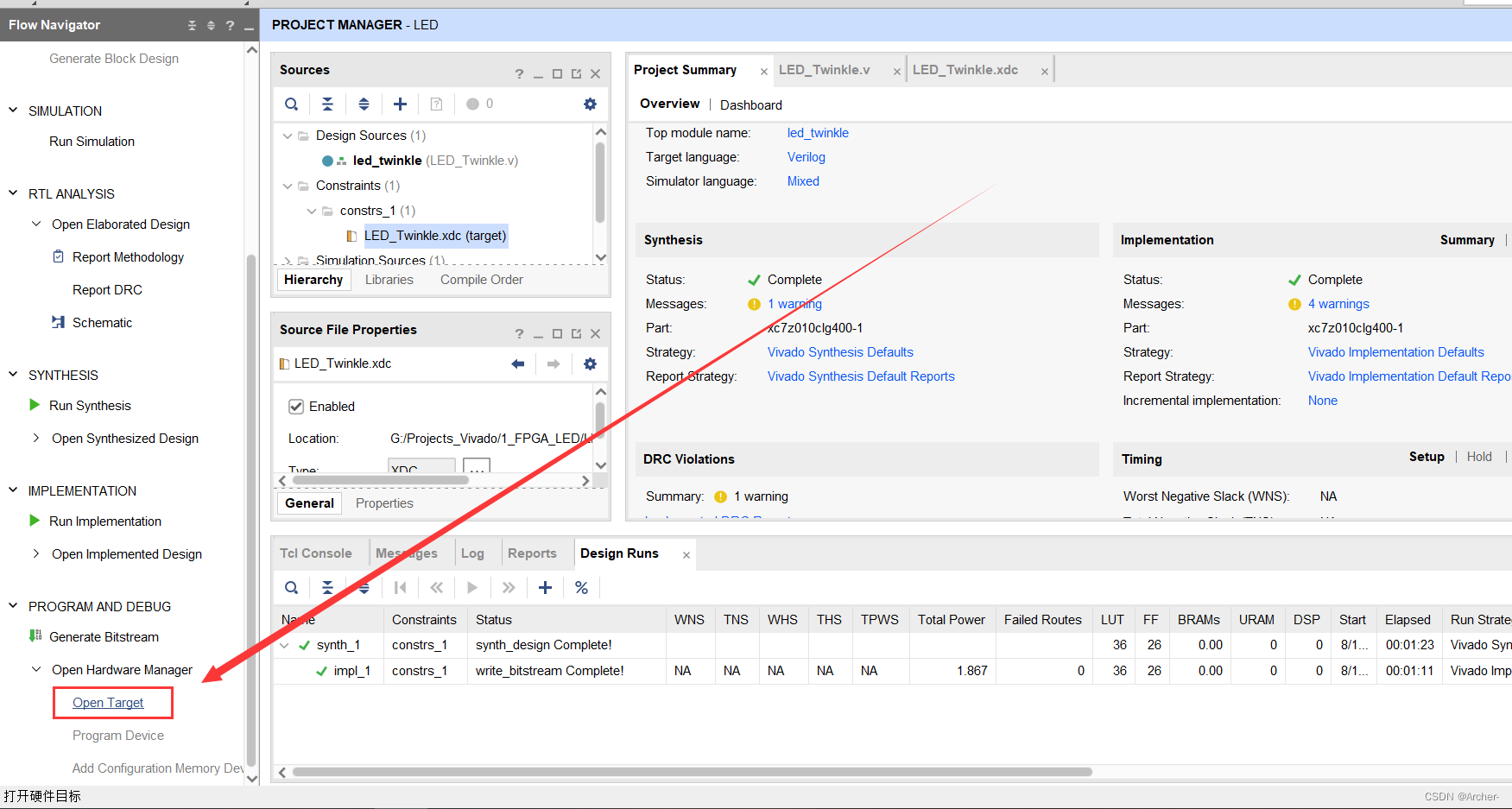

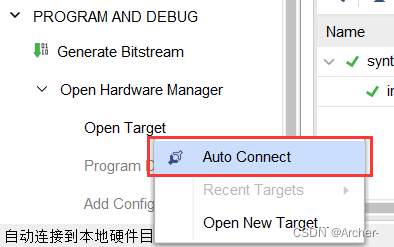

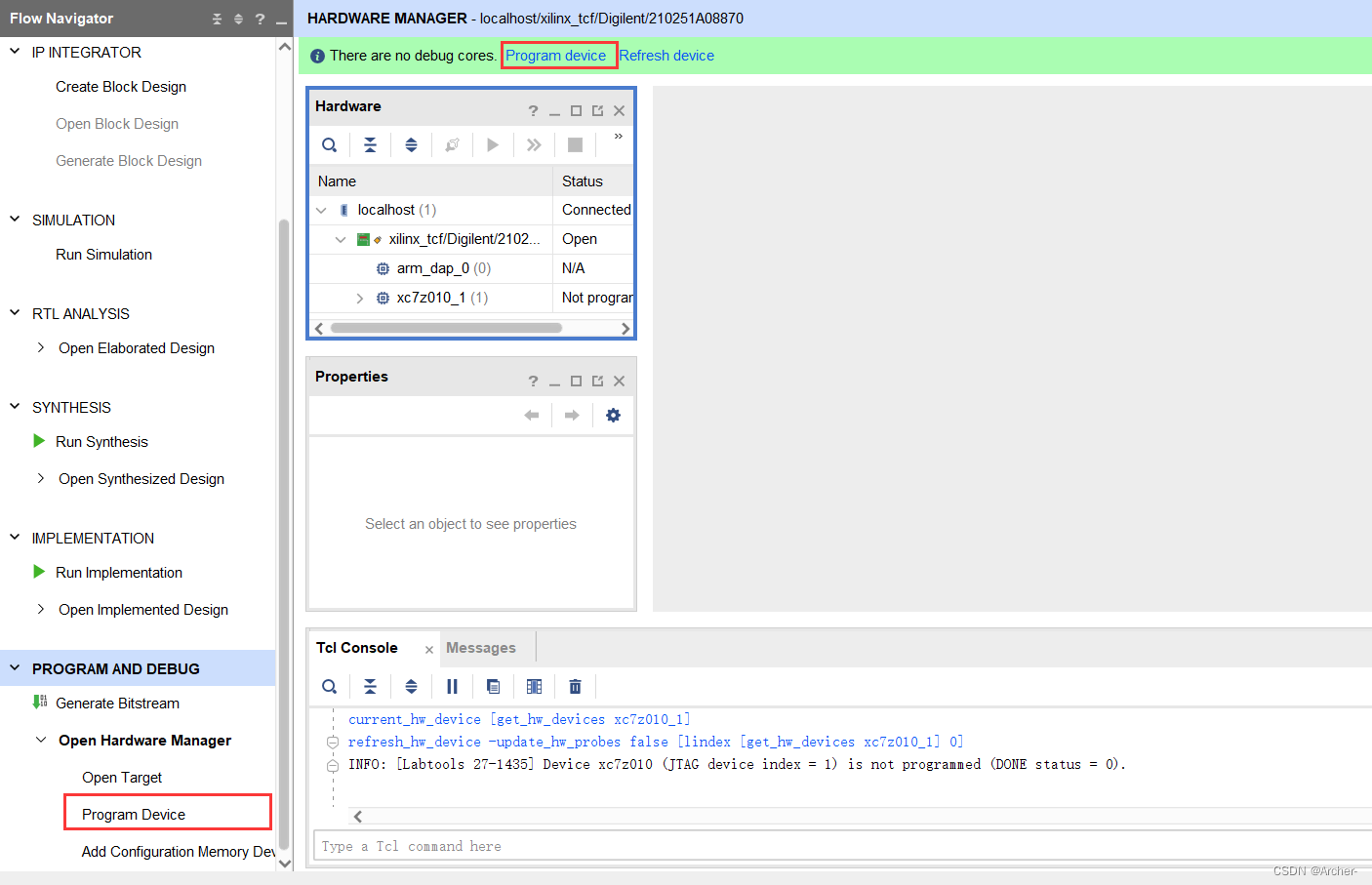

6 下载

点击这两个地方可以下载程序

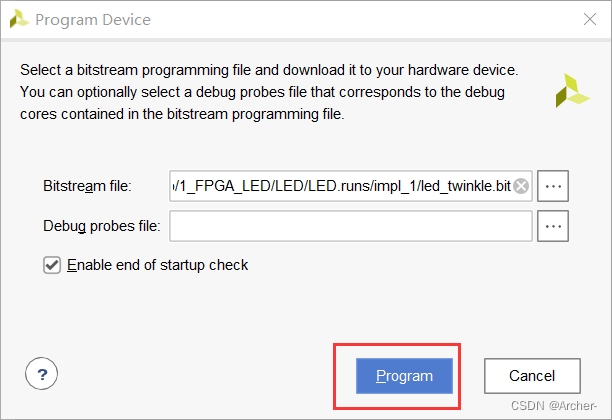

点击Program

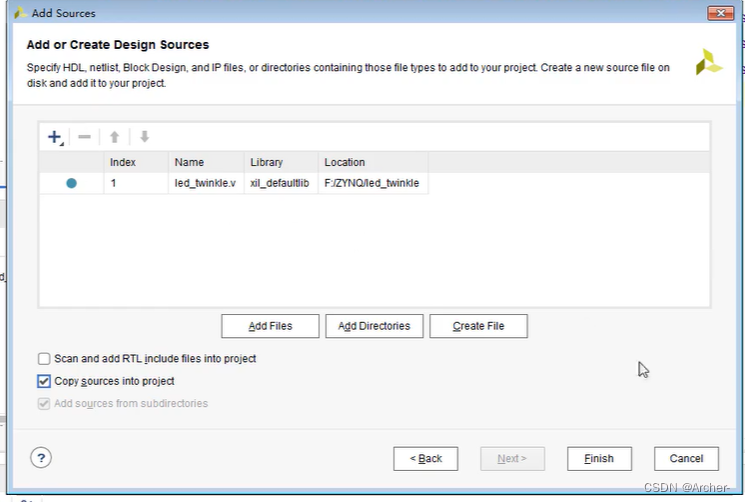

此外可以添加已有的文件到工程中

注意点击Copy source into project

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小蓝xlanll/article/detail/724741

推荐阅读

相关标签