- 1mysql 变量定义与赋值_MySQL变量的定义与赋值

- 24.Apache-Zookeeper 命令操作_zk delete deleteall rmr

- 3使用scrapy框架抓取手机商品信息(1)_scarpy爬取京东数据

- 4L1正则化和L2正则化的区别_l1正则化和l2正则化的区别是

- 5Polar码的编码思想以及SC译码算法

- 6大学化学比较好的搜题软件?完整适配大学课程的搜题工具 #其他#媒体#学习方法

- 7多.net环境下, 配置C#运行与对应的.net版本环境

- 8centos7系统上安装kafka消息集群_centos虚拟机 kafka集群的通信

- 9深度研究DSNeRF代码(慢慢更新)

- 10Python爬虫详解_link = re.findall(findlink, item)

计算机接口74LS138,用74ls138设计全加器

赞

踩

用74ls138设计全加器

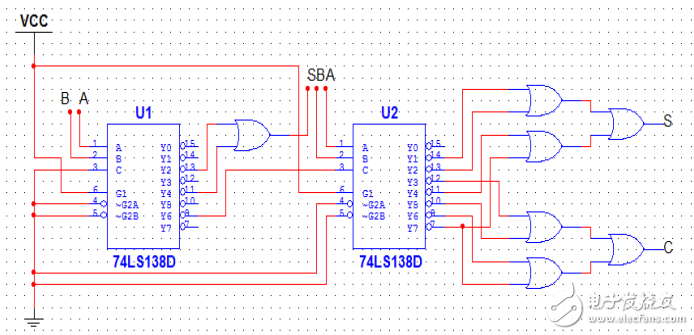

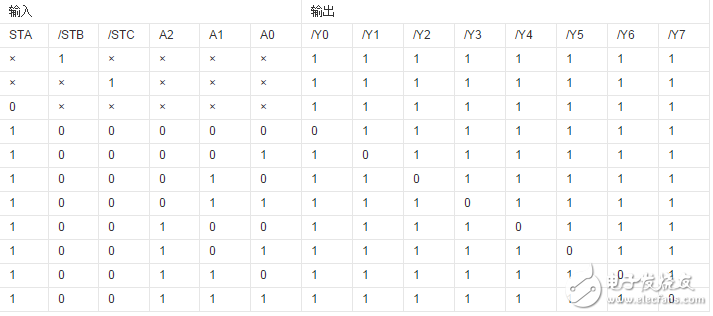

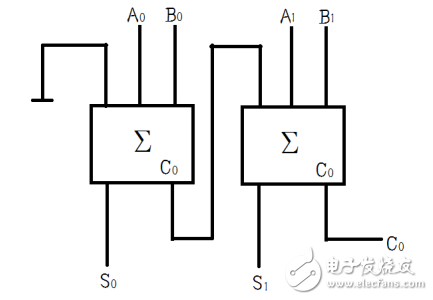

两个二进制数之间的算术运算无论是加、减、乘、除,目前在数学计算机中都是化作若干步加法运算进行的。因此,加法器是构成算术运算器的基本单元。在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位3个数相加。这种运算称为全加,所用的电路称为全加器。用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理为:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。根据以上特性,设计制作出一个全加器。

74LS138有三个附加的控制端。当输出为高电平(S=1),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平。带控制输入端的译码器又是一个完整的数据分配器。如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

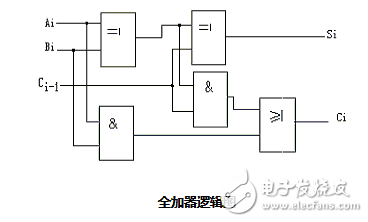

用门电路实现两个二进数相加并求出和的组合线路,称为一个全加器。

全加器原理图

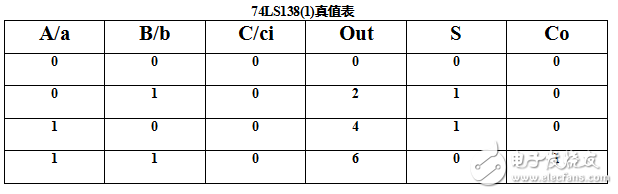

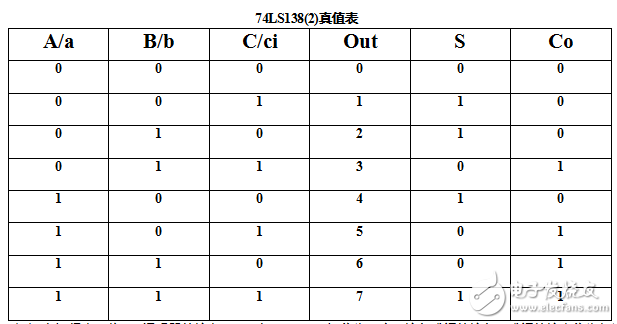

A/a B/b C/c为全加器和译码器的输入,OUT为译码器的输出(0 ~7),S为加法器的和,Co为加法器进位输出。PS:假定译码器输出高电平有效。

由表74LS138(2)得出:将3/8译码器的输出OUT(1,2,4,7)作为一个四输入或门的输入,或门的输出作为加法器的和;将3/8译码器的输出OUT(3,5,6,7)作为一个四输入的或门的输入,或门的输出作为加法器的进位输出。