热门标签

热门文章

- 1mybatis的mapper映射配置文件、个别场景记录_mybatis配置文件mapper映射

- 2python课程作业——第1章 起步_python第一章作业初级

- 3【面试题】做了一份前端面试复习计划,保熟~

- 4Git使用中关于rebase 、stash 、reflog、reset的一些注意点_git reflog rebase

- 5Docker07——镜像构建案例_docker制作镜像经典案例

- 6mysql restart fail_2019-01-31 MySQL 的一次启动失败的问题定位

- 7NLP预训练模型超大规模探索_大模型drop操作

- 8二分法的时间复杂度计算_二分法时间复杂度

- 92024年Linux最新Sourcetree安装教程及使用_sourcetree 安装使用,2024年最新实战解析_sourcetree linux

- 10给hexo博客的NEXT主题添加一个云日历

当前位置: article > 正文

FPGA时序分析与约束(3)——TimeQuest Timing Analyzer软件使用_quartus13.0三种工况下时序分析

作者:很楠不爱3 | 2024-05-26 02:29:40

赞

踩

quartus13.0三种工况下时序分析

FPGA时序分析与约束(2)——TimeQuest Timing Analyzer软件使用

本文中时序分析使用的平台: quartusⅡ13.0

芯片厂家:Inter

约束的作用:1、指导EDA软件对设计的布局布线进行合理的优化以尽量满设计的约束需求,2、给时许分析工具提供一个具体的分析时钟的参考

如何告知时序分析软件我们的时钟频率是多少呢?

约束:时序约束,怎么约束呢?软件:(TTA)TimeQuest Timing Analyzer

约束步骤:

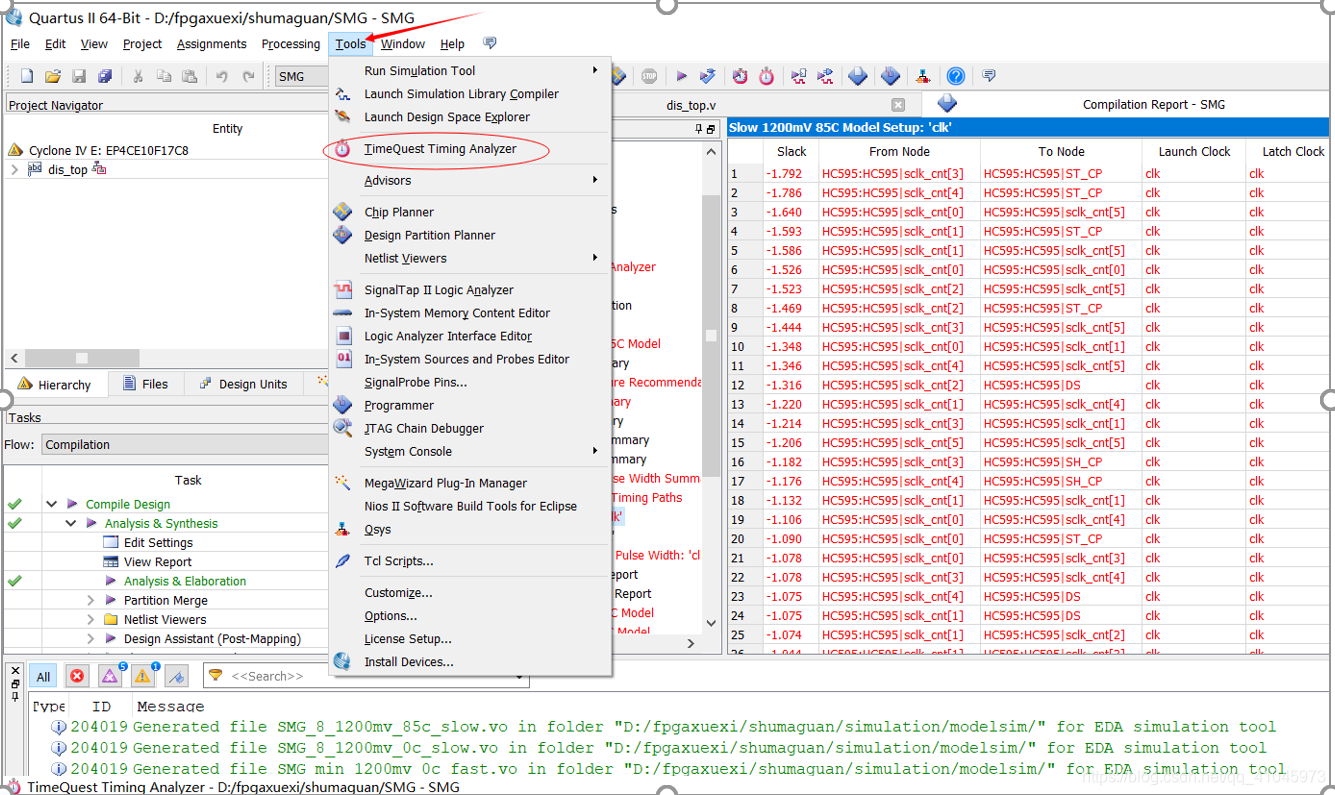

1、打开TTA软件

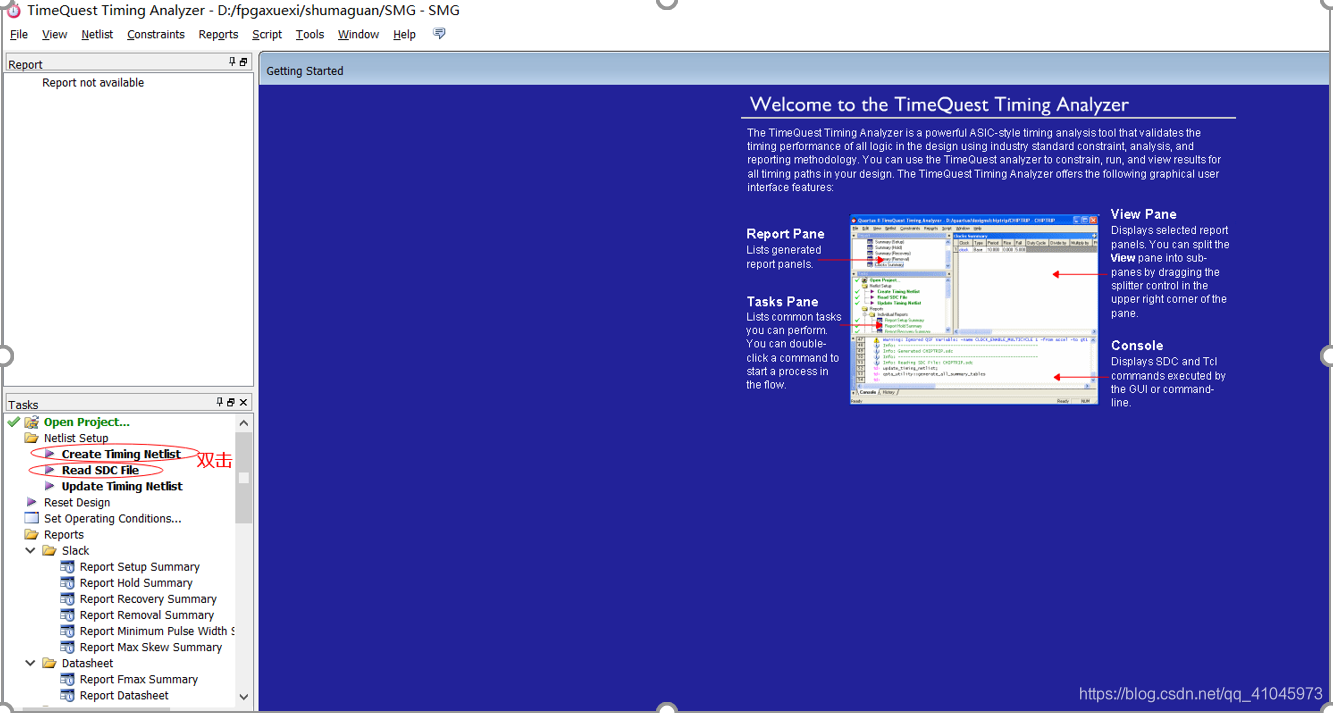

2、创建时序网表

3、读取SDC文件

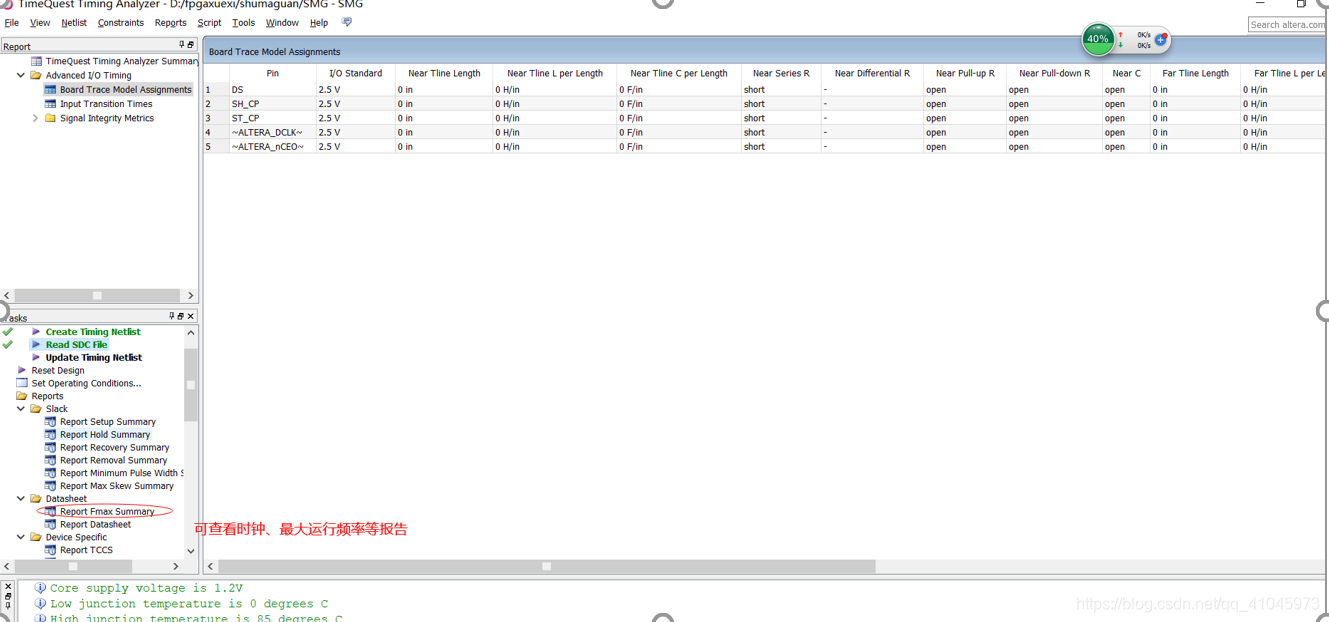

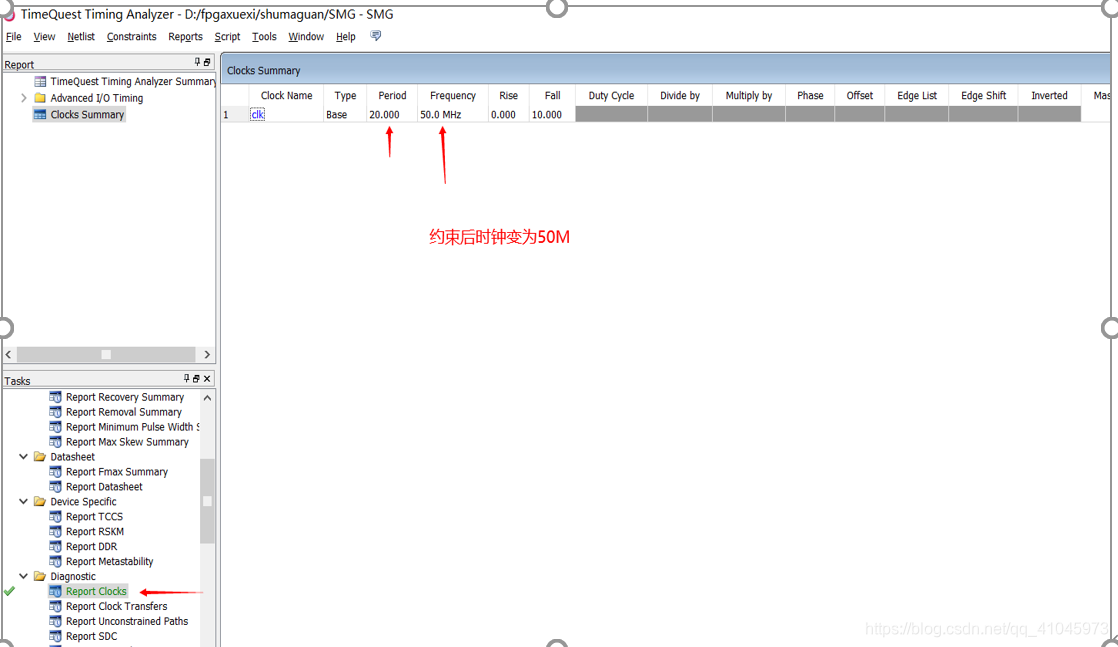

4、查看时钟报告

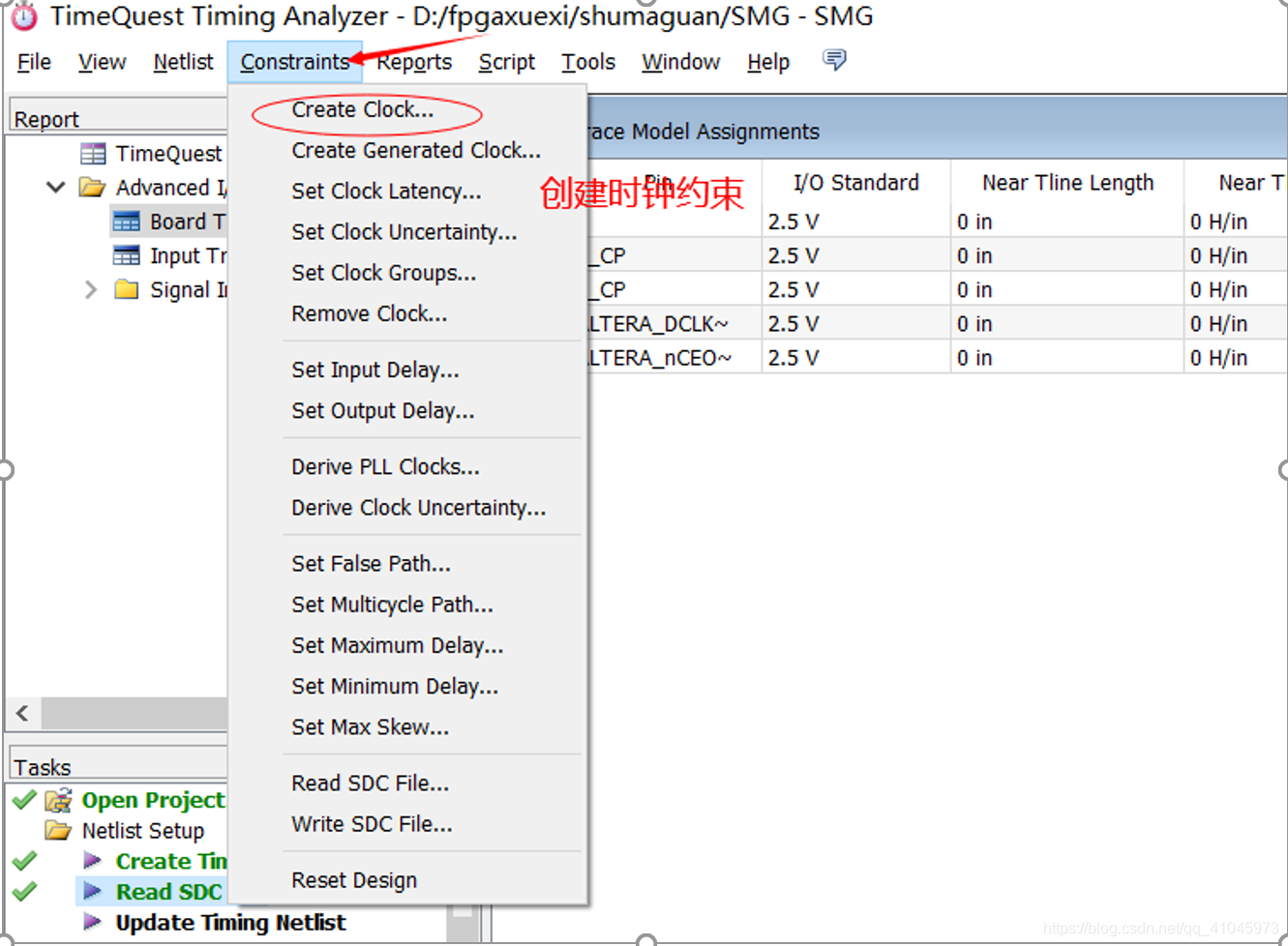

5、加入时钟约束

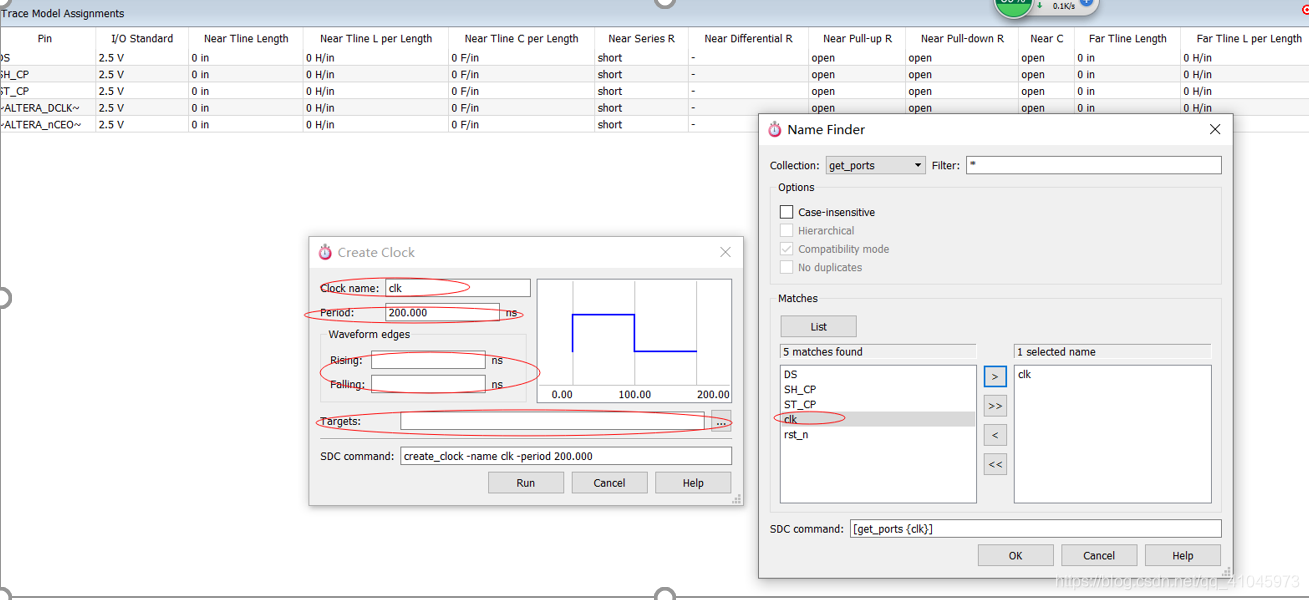

这里加入频率为50M、占空比为50%的时钟信号

写完SDC文件之后就可关掉TTA软件。

重新编译工程查看时钟、最大运行频率等参数已改变为50M时钟下的结果。

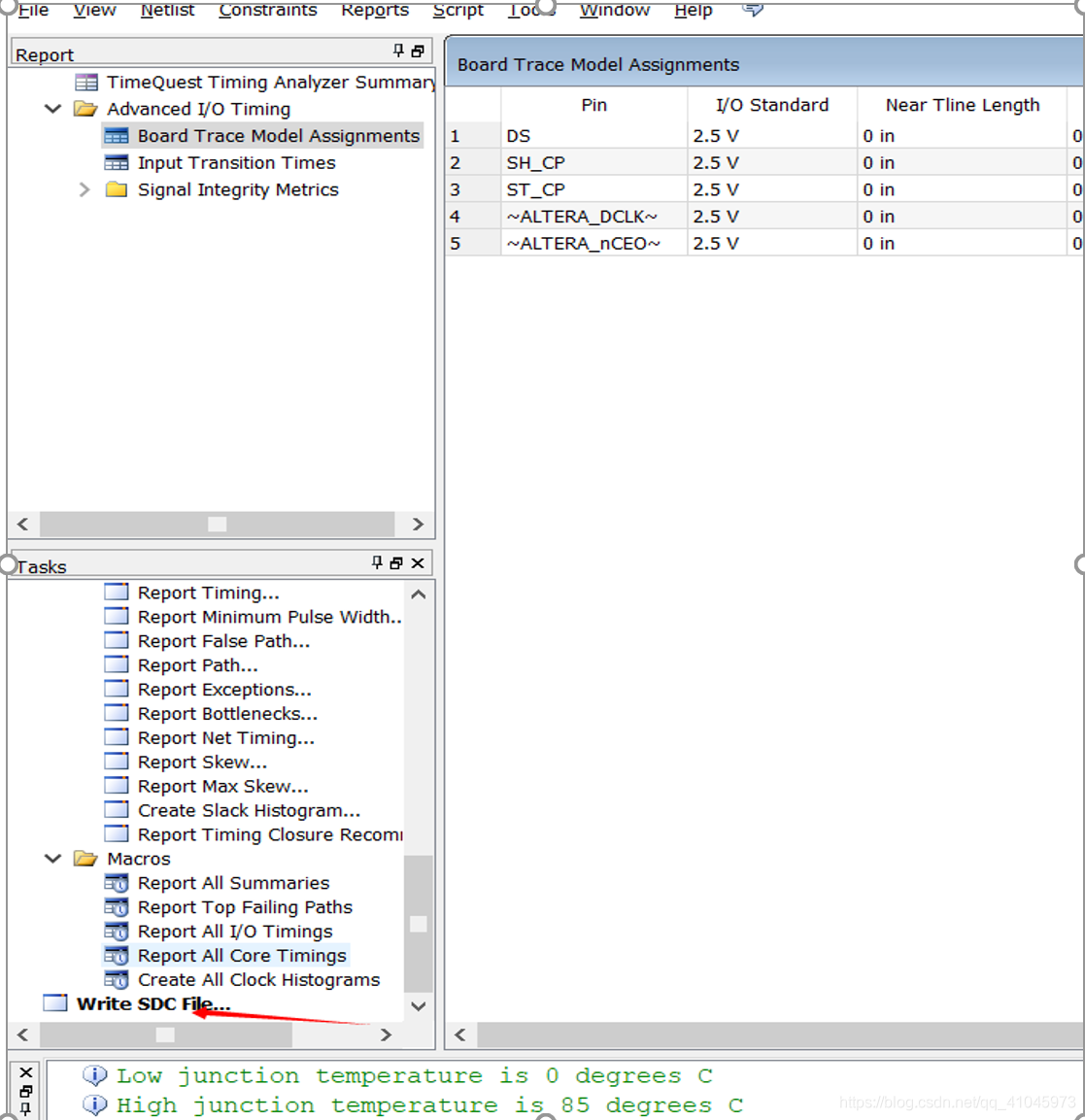

Create-clock:被创建约束的时钟代号

时序分析不是对代码进行分析,而是对具体的门级传输路径进行分析,所有约束操作完成之后,需要执行写SDC文件的操作,这个操作会生成包含所有约束的SDC文件,EDA软件会根据约束需求去布局布线以达到约束要求,但是,不会每次编译都会按照最优的情况去编译,所以说设计中一定要最起码加入合理的约束

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/很楠不爱3/article/detail/624781

推荐阅读

相关标签