- 1MSBulid、IncrediBuild命令行接口实现自动化编译_klsp.fn

- 2uniapp 写安卓app,运行到手机端 调试_uniapp 运行到app

- 3爬取豆瓣电影Top250和数据分析_怎么爬排名前十的电影

- 4二维数组的定义和引用_二维数组的定义与使用

- 5自然语言处理之智能问答系统

- 6transfomer中Multi-Head Attention的源码实现_nn.multiheadattention 官方源码

- 7ORCLE函数学习方法

- 8键盘数字键打不出来怎么解锁?收藏好这4个简单方法!

- 92021-01-05_2021-01-05t07:00:00+08:00是什么日期格式

- 10使用阿里云微调chatglm2_model.stream_chat

第二章 FPGA OTA升级方案的分析及简单用例测试

赞

踩

1.FPGA配置更新基础介绍

1.1 FPGA的运行方式

FPGA程序运行的方式有两种方式:

(1)加载到本地RAM(掉电不保存)

(2)将程序固化到FLASH中(掉电保存),FPGA上电后自动从地址0加载固件

1.2 FPGA Multiboot介绍

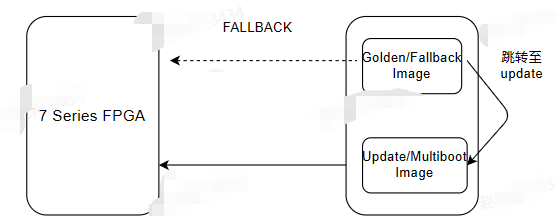

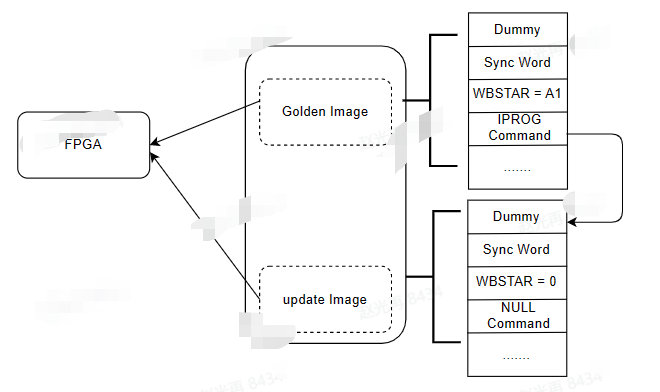

Xilinx 7系列有Multiboot设计,这种设计允许在应用现场支持FPGA在线加载多种不同应用,并可支持回退。但是需要说明的一点,Virtex®-7 HT FPGAs 是不支持回退的。 Multiboot设计在配置过程出现错误,FPGA触发回退,确保FPGA不变砖。

Multiboot设计支持FPGA将bitstream 文件下载到指定的地址。通过一个内部生成的脉冲信号(IPROGRM)初始化跳转逻辑,地址在Golden bitstream WBSTAR寄存器。如果配置错误,回退到Golden Image加载。

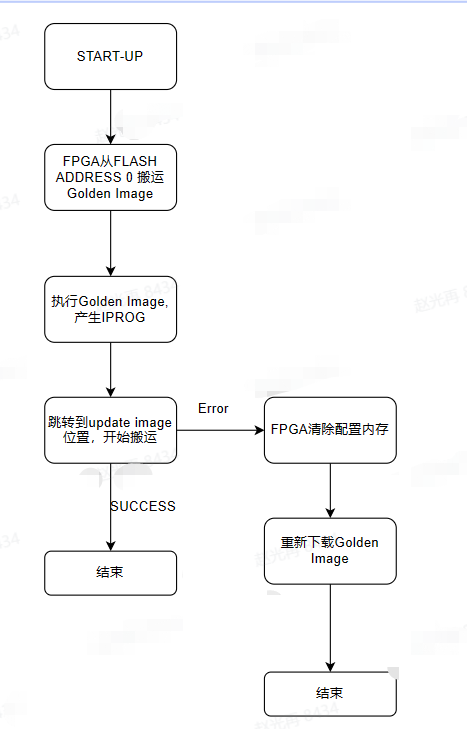

Mulitboot详细的实施逻辑如下:

1.3 FPGA加载程序的流程

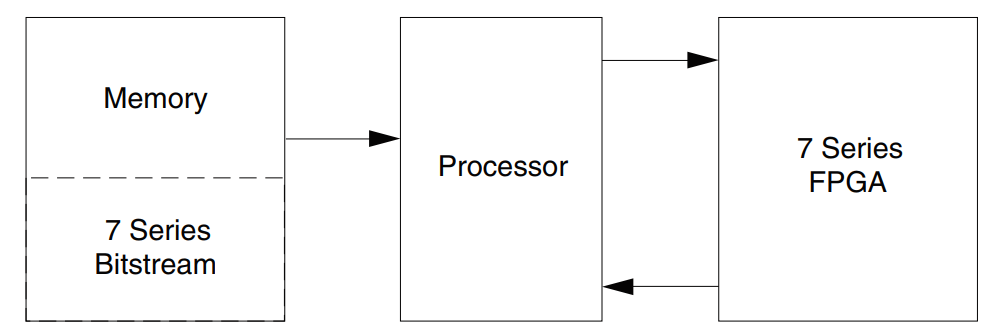

(1) 通过MCU配置FPGA,我们认识下FPGA的配置流程

如下图所示,是MCU配置FPGA的示意图,通过MCU将程序下载到FPGA上。

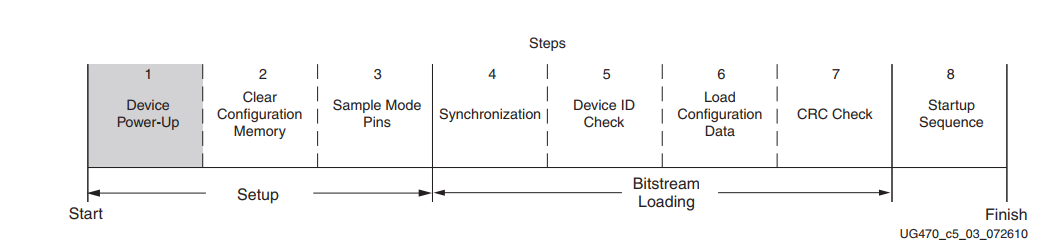

(2)配置流程

① 上电或者配置复位

配置复位:PROGRAM_B管脚生效

② 器件初始化

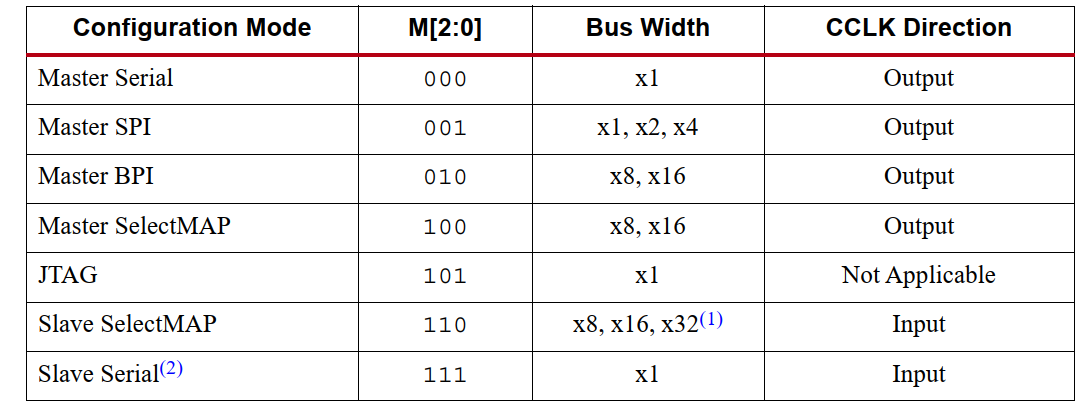

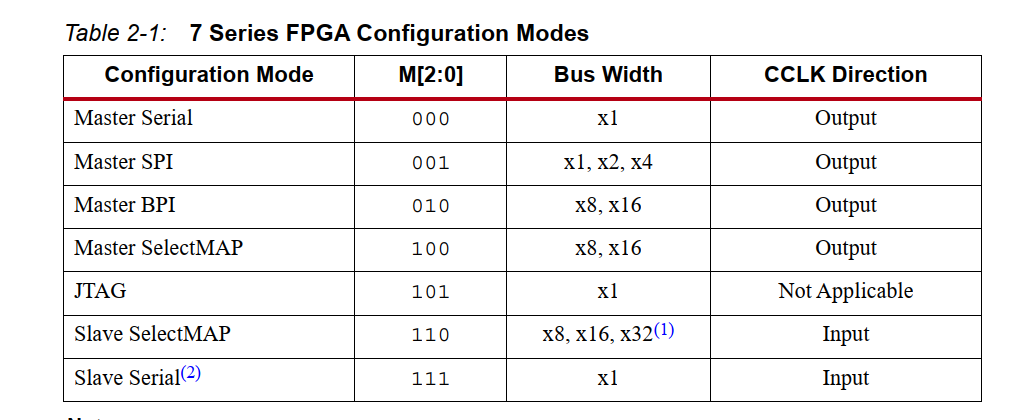

上电或者配置复位触发配置内存初始化,初始化阶段,FPGA会将INIT_B拉低,并复位内部配置状态机,并且清除配置内存;初始化完成时,FPGA释放INIT_B,INIT_B成为高阻态。当INIT_B释放成高阻态,外部上路电阻将INIT_B拉高。当INIT_B 变高,FPGA采用配置模式管脚M[2:0]状态,配置管脚决定FPGA配置模式。

M[2:0] = 111时,FPGA设置为Slave Mode; 当M[2:0] = 110时,FPGA设置为SLAVE SelectMAP模式。采样完引脚的模式后,FPGA准备接收配置数据(bitstream)

③ 配置下载:如果FPGA是配置成Slave Mode时,外部MCU能够将bitstream下载到FPGA。 对于Slave串行模式来说,通过FPGA_D01_DIN 引脚将bitstream下载进去,每个CCLK上升沿下载一个bit。

如果是Slave SelectMAP模式,当FPGA_CSI_B和RDWR_B管脚为低时,数据通过FPGA D[31:0]在CCLK上升沿下载

1.4 FPGA配置bitstream文件的组成

bitstream文件分为两部分,一部分是将基础版本,为Gold image;另一部分是更新程序,为最新程序版本update image。

FLASH的大小,FLASH大小必须是bitstream文件的两倍以上。目前开发板采用的是Artix-7系列的7A35T,bitstreams长度是17536096bits约等于16Mb,那么FLASH最小大小为32Mb.具体怎么计算,可以按照下列的流程进行。

FPGA配置文件称为“Bitstream”,FPGA的“Bitstream”长度是一定的,它的组成如下:

Sync Word: 0xAA995566 (32bit)

Device Identification: A device ID for checking the appropriate device is receiving the bitstream

CRC check: 数据校验

1.5 FPGA配置模式

FPGA配置模式如下,其中主从模式的区别主要是时钟的来源。主模式的时候,来源于FPGA。

其中,Slave SelectMAP x16和x32 bus Widths不支持AES-encrypted bitstreams;

当管脚悬空的时候,默认模式时Slave Serial,因为FPGA内部有上拉电阻。

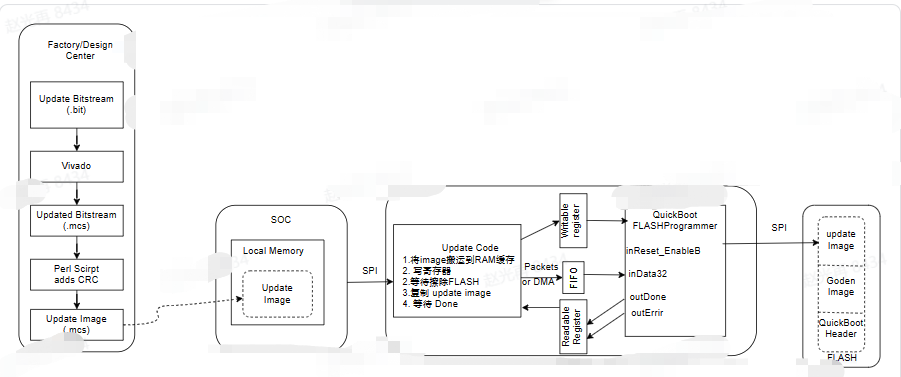

2 FPGA OTA方案实施

2.1 FPGA在线配置的实施架构

如下图所示,云端FPGA的bitstream文件通过SOC获取,SOC通过SPI将bitstream文件传给FPGA,FPGA通过SPI将bitstream文件写入FLASH。更新完后,SOC可以复位FPGA,FPGA重新加载程序即可。

2.2 FPGA在线配置的硬件需求

2.2.1 BOOT 模式的选择

根据官方Datasheet的建议,选择主模式,CLK由FPGA产生,接口两种形式,分别为“SPI接口”和“BPI接口”,我们选择SPI接口,硬件配置如下图所示。

几点说明如下:

DONE是开漏,接上拉电阻;

INIT_B是开漏,支持双向,需要上拉

Bitstream启动时钟一定需要配置为SPI的CLOCK

CCLK的信号完整性非常关键,需要终端匹配。

DOUT不支持菊花链

FPGA和FLASH的数据线有必要加上串联电阻,减少过冲

7系列的FPGA的VCCO_0的供电需要与SPI的I/o的VCC吻合

为确保FPGA复位的时候,FLASH也复位,FLASH的复位信号应该连接到FLASH的复位信号(防止FLASH正在擦写时候FPGA复位,导致FPGA配置失败)

2.3 FPGA在线配置功能模块详解

要实现FPGA在线配置的功能,首先需要FPGA举要BootLoader模块,这个模块就是Golden Image;其次就是应用程序,即Update Image。当然需要说明的一点就是,Golden Image是通过JTAG下载到FLASH里面,是初始化的第一步。

2.3.1 Golden Image模块的功能拆解

(1)SPI接口通信功能:SOC与FPGA的通信

(2)搬运功能的使能和关闭:SPI接收SOC的指令启动搬运功能,将update image搬运到FPGA的RAM中

(3)FLASH通信功能:FPGA与FLASH通信,对FLASH进行擦除、写和读

(4)跑马灯功能:指示Golden Image运行正常

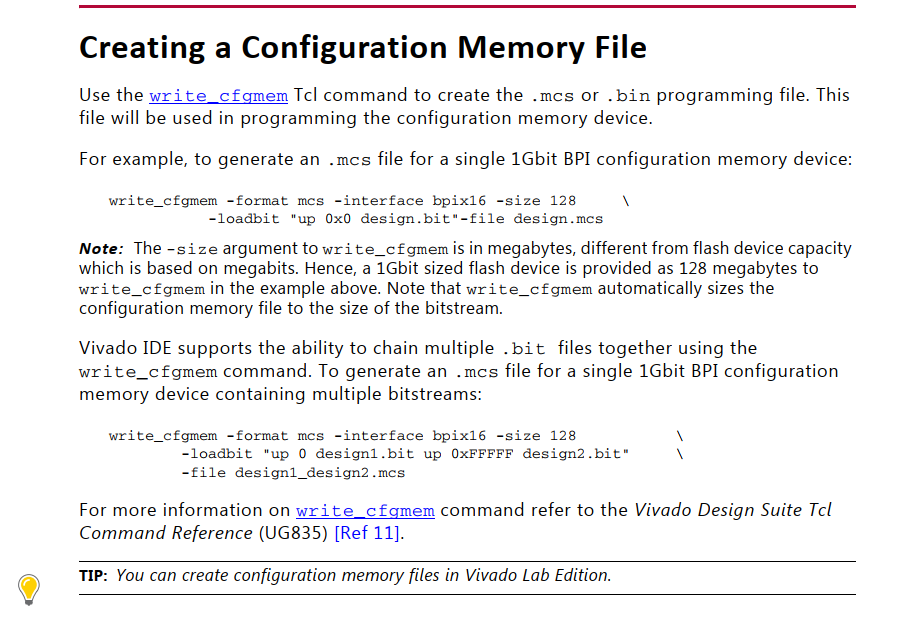

2.3.2 Golden Image和update Image的配置 流程<ug908>

(1)通过Vivado编译生成bitstreams文件

(2)创建可配置文件.msc

(3)连接JTAG

(4)设置配置FLASH型号

(5)下载程序

(6) BOOT FPGA

2.3.3 Golden Image和update Image的配置实例

采用的FPGA是ALINX的开发板,FPGA型号是:ARTIX-XC7A35T-2FGG484

(1)确定配置方式,其中7系列的配置模式如下,主要分为两大类,分别为MASTER和SLAVE模式,主要区别就是数据驱动的CLK从哪里来。MASTER模式就是FPGA提供时钟,SLAVE模式时外部提供时钟。参考手册《UG470》

(2) 通过VIVADO配置Gold Image,其中GOLD 程序需要定位next boot address ,参考手册《xapp1247》

注意:由于我们选用的128Mbits的ROM,而非是128MBytes的ROM。因此在生成.mcs,地址设置是根据Byte计算。

比如我们将update Image的地址配置在ROM的中间位置,地址应该是 0x0040000,而非0x0400000.

VIVADO生产MCS 的脚本如下:

write_cfgmem -format mcs -size 16 -interface SPIx4 -loadbit {up 0x00000000 "E:/xapp1247-multiboot-spi/Vivado/Golden/Golden.runs/impl_2/Top_mudule.bit" } -loaddata {up 0x00400000 "E:/xapp1247-multiboot-spi/Vivado/Update/Update.runs/impl_2/update_module.bit" } -file "E:/xapp1247-multiboot-spi/Vivado/gold_update"。

同时为了有效跳转update,我们需要将在golden image的XDC文件设置如下:

A. 设置SPI接口和模式

#set_property CONFIG_MODE SPIX1 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

B. 设置压缩模式,节省传输时间

#Compress the bitstream to fit on 128M QSPI

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

C. 在Golden image设置好update image地址

#BITSTREAM PROPERTIES REQUIRED FOR GOLDEN IMAGE:

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x0400000 [current_design]

为了在update image出现错误的时候,能够有限跳转回去golden image,我们需要将update image的文件设置如下:

A. 设置FALLBACK 使能

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

B. 设置压缩模式,节省传输时间

#Compress the bitstream to fit on 128M QSPI

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

C. 设置SPI接口和模式

#set_property CONFIG_MODE SPIX1 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

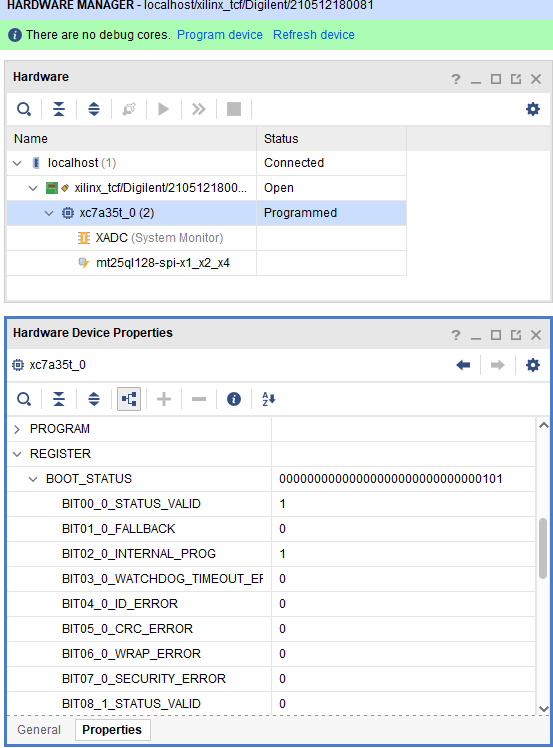

(3)配置后查看是否成功

Hardware Device Properties可以监测Register BOOT_STATUS的状态,如下图所示,配置成功,成功跳转到update image执行

为了判断是否可以跳转,我们可以人为的制造CRC错误,用hex editor打开update 的bitstreams文件,强制修改CRC,可以实现FALLback.