热门标签

热门文章

- 1xv6项目开源—05

- 2tensorflow contrib_深度学习算法优化系列五 | 使用TensorFlow-Lite对LeNet进行训练后量化

- 3基于单片机电子硬币储存器的设计

- 4人工智能——与或树的有序搜索_与或搜索树

- 5Mac环境下Homebrew的安装指南:步骤解析与常见问题解决_mac homebrew 安装网络问题

- 6【Nginx】负载均衡的配置(内网)_php nginx负载均衡 server 可以使用内网ip吗

- 7Flutter3引用原生播放器-IOS(Swift)篇_flutter ios videoplayer

- 8为什么要学 Flink,Flink 优势在哪?_flink优势

- 9GitHub 开源!AI 最全干货超级大列表,100+ 张速查表全了!

- 10花了我一个晚上时间整理的Python魂斗罗小游戏源代码_github魂斗罗游戏

当前位置: article > 正文

西南科技大学数字电子技术实验二(SSI逻辑器件设计组合逻辑电路及FPGA实现 )FPGA部分_ssi组合逻辑电路实验

作者:我家小花儿 | 2024-04-10 08:17:38

赞

踩

ssi组合逻辑电路实验

一、实验目的

1、掌握用SSI(小规模集成电路)逻辑器件设计组合电路的方法。

2、掌握组合逻辑电路的调试方法。

3、学会分析和解决实验中遇到的问题。

4、学会用FPGA实现本实验内容。

二、实验原理

包括:原理图绘制和实验原理简述

1、1位半加器

2、1位全加器

3、三变量多数表决器

4、1位二进制数比较器

当A>B,L1=1,L2=L3=0;

当A<B,L3=0,L1=L2=0;

当A=B,L2=1,L1=L2=0;

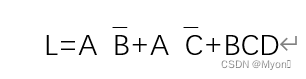

5、四变量多数表决器

三、程序清单(每条语句必须包括注释或在开发窗口注释后截图)

提示:多个设计按以下格式(打印时删除)

1、1位半加器

module halfadder

(

input A,B,

output S,Co

);

assign S = A^B;

assign Co = A*B;

endmodule

2、1位全加器

module fulladder

(

input A,B,C,

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家小花儿/article/detail/397551

推荐阅读

相关标签