热门标签

热门文章

- 1XGBoost模型调参:GridSearchCV方法网格搜索优化参数_xgboost网格搜索

- 2数据结构 顺序表的查找_1.输入一个值,查找该值在顺序表中的位置。2.输入一个位置,查找该位置上元素的值。

- 3投资_风险和比例成正比,所以应该尽可能选择风险大的项目吗

- 4C++【unordered_map/set的底层实现-哈希表】—含有源代码_unordered_map底层实现

- 5redis requires Ruby version >= 2.2.2 系统默认 ruby 版本过低,导致 Redis 接口安装失败_redis requires ruby version >= 2.2.2.

- 6架构师核心-云计算&云上实战(云计算基础、云服务器ECS、云设施实战、云上高并发Web架构)

- 7GitLab跨版本升级

- 8几款开源 Redis 可视化管理工具_连接redis的开源工具

- 9Java List集合取交集的八种不同实现方式_java list 交集

- 10基于Arduino IDE开发的ESP8266(ESP-12F)项目4 ——中断及高级输入输出_esp8266 esp-12f

当前位置: article > 正文

【FPGA】基于Verlog的IIC协议2-IIC时序和控制器件写入_verilog iic驱动模块时序

作者:笔触狂放9 | 2024-04-21 07:07:36

赞

踩

verilog iic驱动模块时序

基于Verlog的IIC协议2-IIC时序和控制器件写入

笔者学到IIC控制eeprom中,发现iic完成一次读必须写一次,根据提供eeprom的iic读写图判断需要满足特定的格式。

举eeprom的格式:

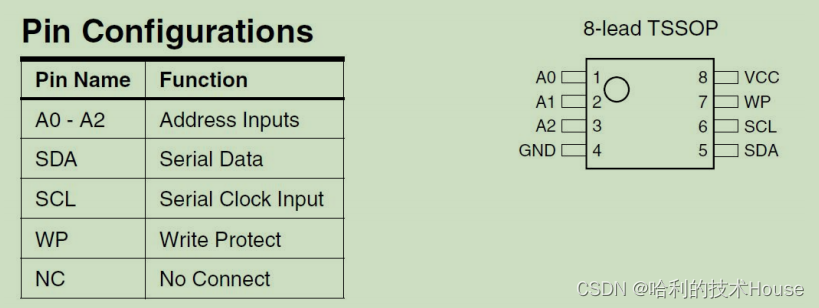

eeprom的器件引脚:

A0-A2:eeprom器件号地址

SDA:输入sda 串行数据(内存地址通过SDA传入,数据通过SDA传入)

SCL:时钟

WP:写保护

NC:不连接

eeprom的写时序

支持单个字节的写,以及多个字节的写

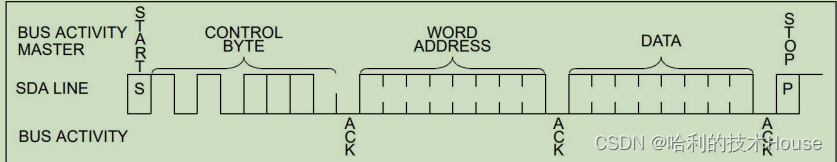

写字节操作 BYTE WRITE

在起始位产生后,先写器件地址,再写芯片内存地址,再写入数据,最后产生停止位,每写一个字节都要产生 ACK 位。

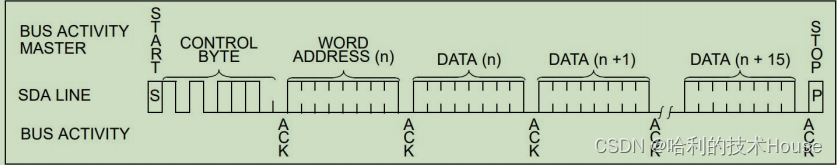

页写 PAGE WRITE

页写和字节写差不多,在字节写的基础上,连续写入数据,最后产生停止位。

eeprom的读时序

支持单个字节的读,以及多个字节的读,三种方式。

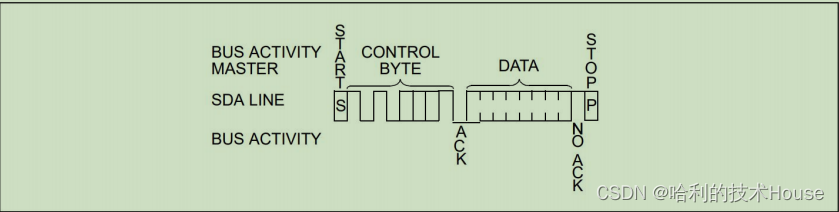

读当前地址 CURRENT ADDRESS READ

只要发送器件地址就能读当前内存地址所指向的地址空间数据,最后的读数据可以不需要发送 ACK,读就需要写一次控制字。(读操作必须要写入控制字)

(内存地址应该是上一次控制传输入的内存地址,如果连续读写进行地址增减)

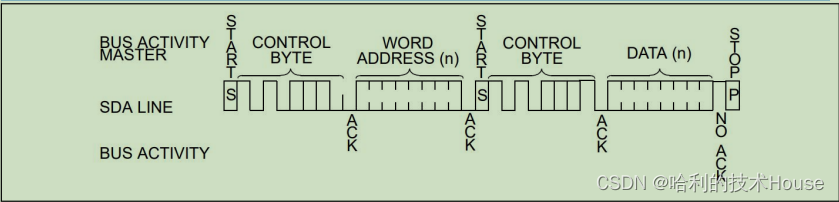

随机读 RANDOM READ

要发送器件地址,然后发送内存地址,之后再发送器件地址并且读取到数据,最后的读数据可以不需要发送 ACK。(读数据必须要写入控制字、内存地址)

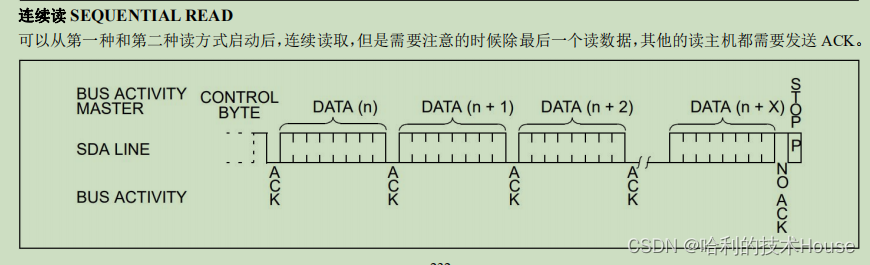

连续读 SEQUENTIAL READ

可以从第一种和第二种读方式启动后,连续读取,但是需要注意的时候除最后一个读数据,其他的读主机都需要发送 ACK。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/461721

推荐阅读

相关标签