- 1webpack中alias配置_webpack.prod.conf修改生产环境的alias

- 2超赞!LeetCode 真题版电子书在 GitHub 上终于开源了

- 3哈工大发布最新综述:大语言模型时代的表格推理技术

- 4arm安装docker与docker-copose_docker-compose arm

- 5锐捷RSR系列路由器_安全_ACL访问控制列表_锐捷配置acl

- 6「重磅」“庙算·智胜”即时策略人机对抗平台开放访问!「AI核心算法」

- 7学术利器!ChatGPT指南,助力学生党高效写论文_写项目申请书用chatgpt3.5还是4.0

- 8【前端工程化】代码没提交到git discard changes 后,ctrl+z无效,使用vscode中的timeline找回修改的代码_vscode timeline

- 9python3.11安装, 解决pip is configured with locations that require TLS/SSL问题

- 10数据结构入门5-1(树和二叉树)_createbitree是什么意思

FPGA Verilog UART_通用异步收发器 fpga verilog hdl

赞

踩

前言

FPGA_Quartus 18.1环境搭建

FPGA_Verilog_PWM

前两天记录了下Quartus环境搭建 点灯, PWM. 本节搬运一下UART的例子.

通用异步收发器UART, 全称Universal Asynchronous Receiver Transmitter, 比USART, SPI之类的少了时钟线, 需要过采样, 但其实发展到现在, 有LPUART之类的完全可以到30Mbps左右的速率, 也不算太慢了. 常用的仍然是9600bps, 115200bps. 常用MCU里面的UART支持:

- 单向, 半双工, 全双工, (多机)通信

- 读写单个/多个字节

- 5~9数据位, 无/奇/偶校验, 0/1/2停止位

- 波特率配置

- LSB/MSB 位/字节序

- 检测或报告错误

- DMA

- FIFO

- 中断(发送/接收/空闲/错误…)

- …

还有自动波特率, 位反转, 收发交换等新的功能, 当然, 一一实现很复杂, 本节仅仅搬运一个简单的串口回环测试.

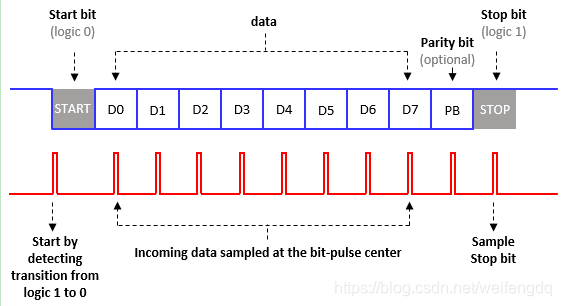

不像以太网之类的, 抛开帧头帧尾, 一下可以来几十数百上千字节, 串口一次只有一个字节, 每个字节算一个Packet, 含起始位/数据位/校验位/停止位等, 通常说的一帧串口数据几个字节, 其中的每个字节都要有这些位, 如常用的115200-8-N-1, 表示115200波特率, 8数据位, 无校验位, 1停止位, 这一个字节至少占用10位了, 换算下来, 1s最多传输11520字节, 只少不多.

串口的数据(Packet)格式(图片来自 链接点我):

此处把正点原子 开拓者FPGA开发板 UART串口通信实验的例子直接搬过来看. 默认-8-N-1, 也就是8数据位, 无校验位, 1停止位.

新建工程

打开Quartus, 步骤如下:

- File -> New Project Wizard…

- Next

- 选择工程目录, 填入工程名.

- Empty Project

- Add Files不设置, 直接点Next.

- 器件选择

EP4CE6F17C8. - EDA Tool Setting暂不动, 点击Next.

- Summary中点Finish.

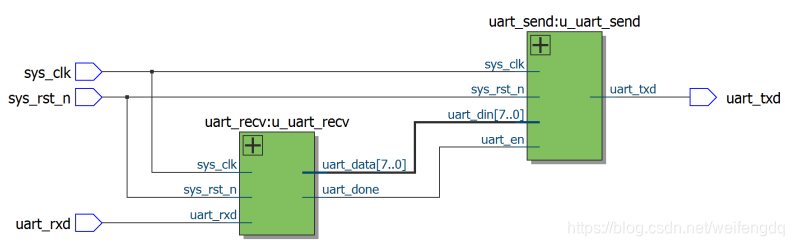

UART顶层

输入50M时钟, 复位信号, 加上发送, 接收端口, 发送接收是独立的, 因为数据格式一样, 代码中很多相通的地方. 由于做的是回环测试, 只需要把接收结束连到发送使能即可, 把原子的图搬过来:

File -> New -> 选择Verilog HDL File, 填入以下代码:

module uart_test( input sys_clk, //外部50M时钟 input sys_rst_n, //外部复位信号,低有效 input uart_rxd, //UART接收端口 output uart_txd //UART发送端口 ); //parameter define parameter CLK_FREQ = 50000000; //定义系统时钟频率 parameter UART_BPS = 115200; //定义串口波特率 //wire define wire uart_en_w; //UART发送使能 wire [7:0] uart_data_w; //UART发送数据 uart_recv #( //串口接收模块 .CLK_FREQ (CLK_FREQ), //设置系统时钟频率 .UART_BPS (UART_BPS)) //设置串口接收波特率 u_uart_recv( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .uart_rxd (uart_rxd), .uart_done (uart_en_w), .uart_data (uart_data_w) ); uart_send #( //串口发送模块 .CLK_FREQ (CLK_FREQ), //设置系统时钟频率 .UART_BPS (UART_BPS)) //设置串口发送波特率 u_uart_send( .sys_clk (sys_clk), .sys_rst_n (sys_rst_n), .uart_en (uart_en_w), .uart_din (uart_data_w), .uart_txd (uart_txd) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

保存为uart_test.v

UART接收

波特率可以当作检测的时机, 检测下降沿捕获起始位, 起始位之后就是8数据位, 无校验位, 那么数据位后就是停止位, 或许是为了迎合起始位的下降沿, 停止位回到的是高电平.

继续File -> New -> 选择Verilog HDL File, 填入以下代码:

module uart_recv( input sys_clk, //系统时钟 input sys_rst_n, //系统复位,低电平有效 input uart_rxd, //UART接收端口 output reg uart_done, //接收一帧数据完成标志信号 output reg [7:0] uart_data //接收的数据 ); //parameter define parameter CLK_FREQ = 50000000; //系统时钟频率 parameter UART_BPS = 9600; //串口波特率 localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率, //需要对系统时钟计数BPS_CNT次 //reg define reg uart_rxd_d0; reg uart_rxd_d1; reg [15:0] clk_cnt; //系统时钟计数器 reg [ 3:0] rx_cnt; //接收数据计数器 reg rx_flag; //接收过程标志信号 reg [ 7:0] rxdata; //接收数据寄存器 //wire define wire start_flag; //***************************************************** //** main code //***************************************************** //捕获接收端口下降沿(起始位),得到一个时钟周期的脉冲信号 assign start_flag = uart_rxd_d1 & (~uart_rxd_d0); //对UART接收端口的数据延迟两个时钟周期 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin uart_rxd_d0 <= 1'b0; uart_rxd_d1 <= 1'b0; end else begin uart_rxd_d0 <= uart_rxd; uart_rxd_d1 <= uart_rxd_d0; end end //当脉冲信号start_flag到达时,进入接收过程 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) rx_flag <= 1'b0; else begin if(start_flag) //检测到起始位 rx_flag <= 1'b1; //进入接收过程,标志位rx_flag拉高 else if((rx_cnt == 4'd9)&&(clk_cnt == BPS_CNT/2)) rx_flag <= 1'b0; //计数到停止位中间时,停止接收过程 else rx_flag <= rx_flag; end end //进入接收过程后,启动系统时钟计数器与接收数据计数器 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin clk_cnt <= 16'd0; rx_cnt <= 4'd0; end else if ( rx_flag ) begin //处于接收过程 if (clk_cnt < BPS_CNT - 1) begin clk_cnt <= clk_cnt + 1'b1; rx_cnt <= rx_cnt; end else begin clk_cnt <= 16'd0; //对系统时钟计数达一个波特率周期后清零 rx_cnt <= rx_cnt + 1'b1; //此时接收数据计数器加1 end end else begin //接收过程结束,计数器清零 clk_cnt <= 16'd0; rx_cnt <= 4'd0; end end //根据接收数据计数器来寄存uart接收端口数据 always @(posedge sys_clk or negedge sys_rst_n) begin if ( !sys_rst_n) rxdata <= 8'd0; else if(rx_flag) //系统处于接收过程 if (clk_cnt == BPS_CNT/2) begin //判断系统时钟计数器计数到数据位中间 case ( rx_cnt ) 4'd1 : rxdata[0] <= uart_rxd_d1; //寄存数据位最低位 4'd2 : rxdata[1] <= uart_rxd_d1; 4'd3 : rxdata[2] <= uart_rxd_d1; 4'd4 : rxdata[3] <= uart_rxd_d1; 4'd5 : rxdata[4] <= uart_rxd_d1; 4'd6 : rxdata[5] <= uart_rxd_d1; 4'd7 : rxdata[6] <= uart_rxd_d1; 4'd8 : rxdata[7] <= uart_rxd_d1; //寄存数据位最高位 default:; endcase end else rxdata <= rxdata; else rxdata <= 8'd0; end //数据接收完毕后给出标志信号并寄存输出接收到的数据 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin uart_data <= 8'd0; uart_done <= 1'b0; end else if(rx_cnt == 4'd9) begin //接收数据计数器计数到停止位时 uart_data <= rxdata; //寄存输出接收到的数据 uart_done <= 1'b1; //并将接收完成标志位拉高 end else begin uart_data <= 8'd0; uart_done <= 1'b0; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

保存为uart_recv.v

UART发送

上面接收完成uart_done是1, uart_done直连发送的使能uart_en, 所以uart_en默认0, 检测到上升沿即可认为接收一字节完毕可以回传了.

继续File -> New -> 选择Verilog HDL File, 填入以下代码:

module uart_send( input sys_clk, //系统时钟 input sys_rst_n, //系统复位,低电平有效 input uart_en, //发送使能信号 input [7:0] uart_din, //待发送数据 output reg uart_txd //UART发送端口 ); //parameter define parameter CLK_FREQ = 50000000; //系统时钟频率 parameter UART_BPS = 9600; //串口波特率 localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率,对系统时钟计数BPS_CNT次 //reg define reg uart_en_d0; reg uart_en_d1; reg [15:0] clk_cnt; //系统时钟计数器 reg [ 3:0] tx_cnt; //发送数据计数器 reg tx_flag; //发送过程标志信号 reg [ 7:0] tx_data; //寄存发送数据 //wire define wire en_flag; //***************************************************** //** main code //***************************************************** //捕获uart_en上升沿,得到一个时钟周期的脉冲信号 assign en_flag = (~uart_en_d1) & uart_en_d0; //对发送使能信号uart_en延迟两个时钟周期 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin uart_en_d0 <= 1'b0; uart_en_d1 <= 1'b0; end else begin uart_en_d0 <= uart_en; uart_en_d1 <= uart_en_d0; end end //当脉冲信号en_flag到达时,寄存待发送的数据,并进入发送过程 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin tx_flag <= 1'b0; tx_data <= 8'd0; end else if (en_flag) begin //检测到发送使能上升沿 tx_flag <= 1'b1; //进入发送过程,标志位tx_flag拉高 tx_data <= uart_din; //寄存待发送的数据 end else if ((tx_cnt == 4'd9)&&(clk_cnt == BPS_CNT/2)) begin //计数到停止位中间时,停止发送过程 tx_flag <= 1'b0; //发送过程结束,标志位tx_flag拉低 tx_data <= 8'd0; end else begin tx_flag <= tx_flag; tx_data <= tx_data; end end //进入发送过程后,启动系统时钟计数器与发送数据计数器 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) begin clk_cnt <= 16'd0; tx_cnt <= 4'd0; end else if (tx_flag) begin //处于发送过程 if (clk_cnt < BPS_CNT - 1) begin clk_cnt <= clk_cnt + 1'b1; tx_cnt <= tx_cnt; end else begin clk_cnt <= 16'd0; //对系统时钟计数达一个波特率周期后清零 tx_cnt <= tx_cnt + 1'b1; //此时发送数据计数器加1 end end else begin //发送过程结束 clk_cnt <= 16'd0; tx_cnt <= 4'd0; end end //根据发送数据计数器来给uart发送端口赋值 always @(posedge sys_clk or negedge sys_rst_n) begin if (!sys_rst_n) uart_txd <= 1'b1; else if (tx_flag) case(tx_cnt) 4'd0: uart_txd <= 1'b0; //起始位 4'd1: uart_txd <= tx_data[0]; //数据位最低位 4'd2: uart_txd <= tx_data[1]; 4'd3: uart_txd <= tx_data[2]; 4'd4: uart_txd <= tx_data[3]; 4'd5: uart_txd <= tx_data[4]; 4'd6: uart_txd <= tx_data[5]; 4'd7: uart_txd <= tx_data[6]; 4'd8: uart_txd <= tx_data[7]; //数据位最高位 4'd9: uart_txd <= 1'b1; //停止位 default: ; endcase else uart_txd <= 1'b1; //空闲时发送端口为高电平 end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

保存为uart_send.v

引脚分配下载验证

接下来点击Pin Planner快捷图标, 分配引脚, 一般是连接串口转USB芯片(CP210x或者CH34x)的引脚.

引脚分配完后, 点击Start Compilation快捷图标编译.

点击Programmer快捷图标, 点击Start下载.

连接开发板USB转串口的USB到PC, 打开串口调试工具, 直接定时发送测试:

可以看到百万字节不丢数.

微信公众号

欢迎扫描二维码关注本人微信公众号, 及时获取或者发送给我最新消息: