- 1Python 基础 — 基础语法_python %name %name

- 290后,转行软件测试3年,从月入7000+到月入过万,整理出的这一万字经验分享。_毕业后第二份工作可以转研发嘛

- 3Unity Lighting Window 属性的序列化与反序列化_unity lightingdata.asset 序列化

- 4深入了解Nginx(一):Nginx核心原理

- 5软件测试—接口测试面试题及jmeter面试题_软件测试面试题接口

- 6STM32+WIFI+MQTT+云Mysql数据上报并转存到云数据库_stm32基于云平台的数据库

- 7【C++】详解深浅拷贝的概念及其区别

- 8使用Git 命令行拉取、提交、推送 代码_git命令行推送

- 9智慧水务大数据平台-智慧水务建设方案_智慧水务平台方案

- 10新朋友+1!拓数派 PieCloudDB Database 与 OpenCloudOS、TencentOS Server 完成产品兼容互认证_opencloudos tencentos server

【FPGA】:Axi quad spi

赞

踩

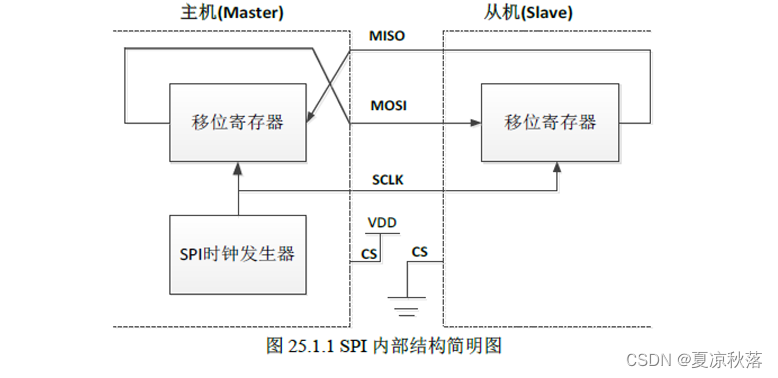

一、概述

SPI是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,短距离的、同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议

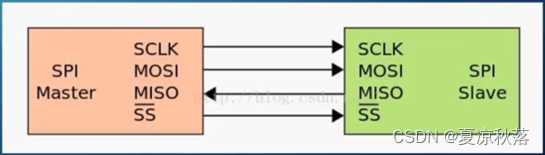

如下图所示,SPI接口一般使用4条线通信:

MISO 主设备数据输入,从设备数据输出。

MOSI 主设备数据输出,从设备数据输入。

SCLK/SCK时钟信号,由主设备产生。

CS从设备片选信号,由主设备控制(CS,有时候又称为NSS),低电平有效

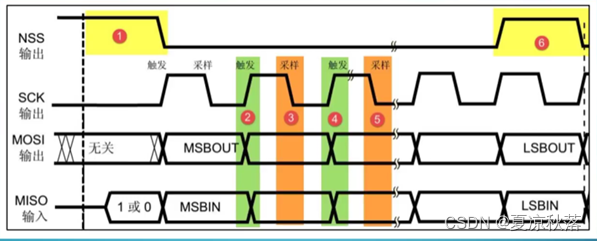

起始信号:CS/NSS/SS由高电平变为低电平

终止信号:CS/NSS/SS由低电平变为高电平

SPI主要由主机进行控制,开始或者结束都由主机控制。Spi协议通常情况下先传输高位,然后再传输低位。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

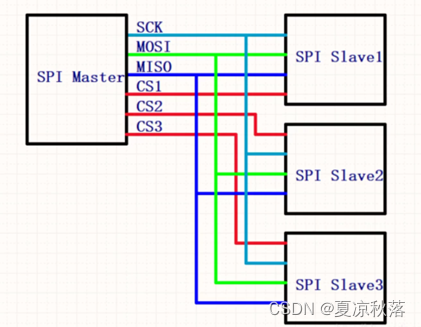

SPI与多个设备通信情况如下图所示:通信时通过cs信号进行拉低,从而选择与那个设备进行通信。

二、时序说明

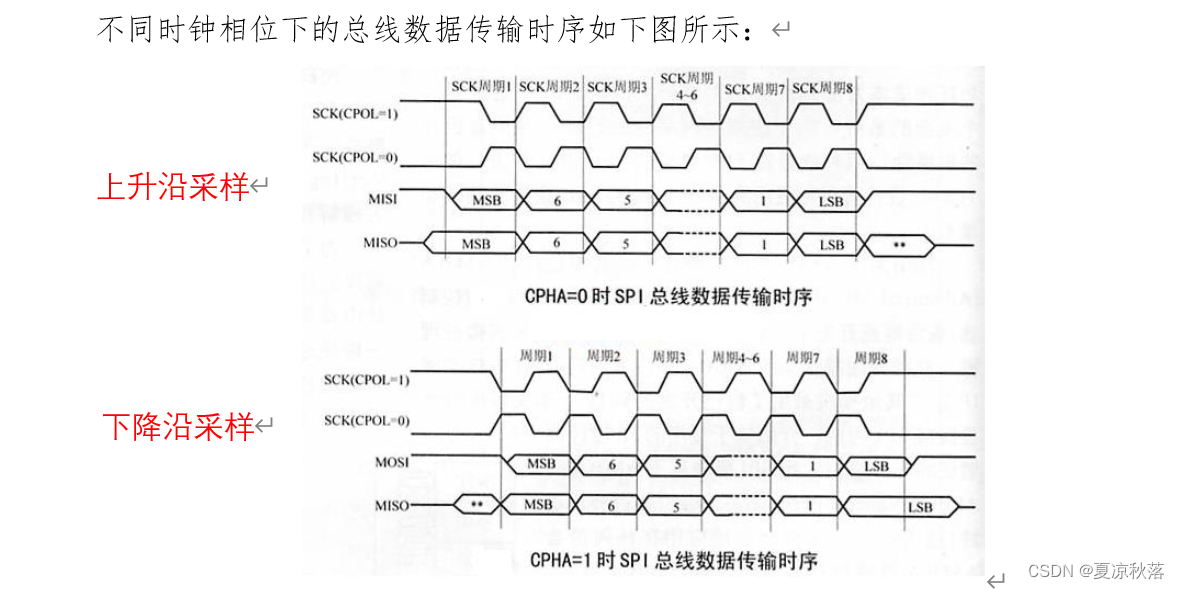

SPI总线四种工作方式:SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设备时钟相位和极性应该一致。

不同时钟相位下的总线数据传输时序如下图所示:

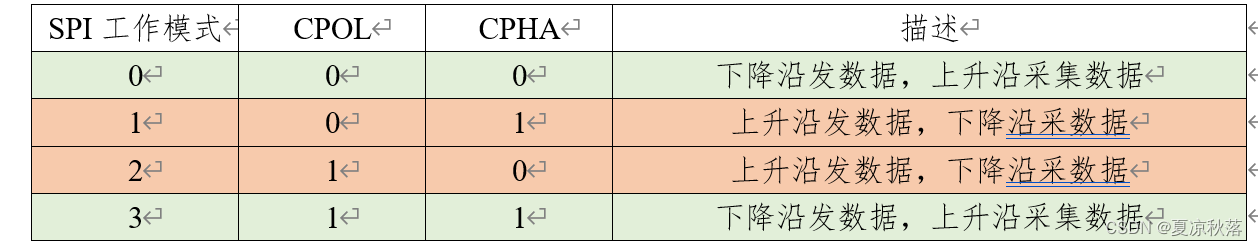

主机和丛机工作模式需要匹配,否则会出错误,具体对应关系如下表所示:

主机和丛机工作模式需要匹配,否则会出错误,具体对应关系如下表所示:

SPI一帧可以传输8位或者16位,主要由SPI_CR1决定。

SPI在fpga中实现时,可以采用线性序列机(一个always计数器,一个always进行数据的发送)/状态机(通常采用一段式或者三段式)实现。

三、SPI的优势和缺点

(1)SPI通讯的优势

全双工串行通信;

高速数据传输速率。

简单的软件配置;

极其灵活的数据传输,不限于8位,它可以是任意大小的字;可以不用报头和报尾,只要cs拉低就开始信号的传输。

非常简单的硬件结构。从站不需要唯一地址(与I2C不同)。从机使用主机时钟,不需要精密时钟振荡器/晶振(与UART不同)。不需要收发器(与CAN不同)。

最先发送的为数据的高位

靠cs信号拉低对应器件来区分是给那个器件传输信号。

全双工同步传输,速度约有50Mbps,即约5.9MB/s

(2)SPI的缺点

没有硬件从机应答信号(主机可能在不知情的情况下无处发送);

通常仅支持一个主设备(通过将片选信号拉低,从而确定要通信的是那个元器件);

需要更多的引脚(与I2C不同);

没有定义硬件级别的错误检查协议;

与RS-232和CAN总线相比,只能支持非常短的距离;

Spi的可靠传输距离只有1~3m。

四、参考资料

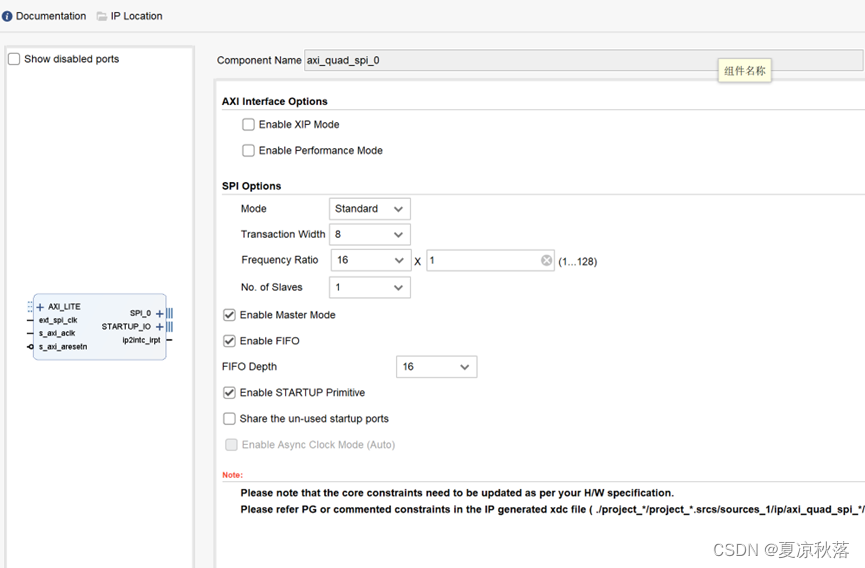

Enable XIP Mode: XIP使能AXI4 和 AXI4-Lite(理解为AXI4的简化版本)接口,地址模式可以选择24bit和32bit;

Enable Performance Mode: 使能AXI4接口;使用AXI4接口可以在核的发送和接收FIFO地址处启用突发功能。当不使能performance模式时,AXI4-Lite将被使用。

Mode: standard(三线SPI,CS、CLK、SIO)/dual(四根线:CS、CLK、SIO1、SIO2)/quad(六根线:CS、CLK、SIO1、SIO2、SIO3、SIO3)

Transacton Width: 8/16/32。在双SPI和四SPI模式中,传输宽度被限制为8位。在XIP模式中,传输宽度在标准模式、双模式和四模式中被限制为8。

频率比率:2~2048, 代表了SPI的sck = ext_spi_clk/ratio ;

NO. of Slave: 代表了slave的个数;1~32;

Enable Master Mode: 主从模式选择,在标准模式下可以选择,其他模式只支持主模式

Enable FIFO: 使能fifo

Enable STARTUPEn Primitive: 勾选时在设计中包含STARTUP原语,未勾选时省略原语。7系列fpga采用STARTUPE2原语,UltraScale设备采用STARTUPE3原语。它在与外部SPI从设备共享SPI时钟时很有用。这个原语在设备的从属模式下总是被禁用的。

Enable Async Clock Mode: 只有当核心处于独立模式,且axis接口和外部SPI时钟在相位/极性和频率方面不同时,才启用此选项。该选项在IP集成商中被禁用。此参数根据连接到核心的时钟自动传播。如果AXI时钟和ext_spi_clk是同步的,该参数设置为0;如果是异步的,该参数设置为1。

五、参考资料

说明;DI输入,DO输出