Xilinx-7 Series FPGA---->Spartan-7---->通用逻辑

---->廉价/低功耗

---->高I/O口性能

---->小封装

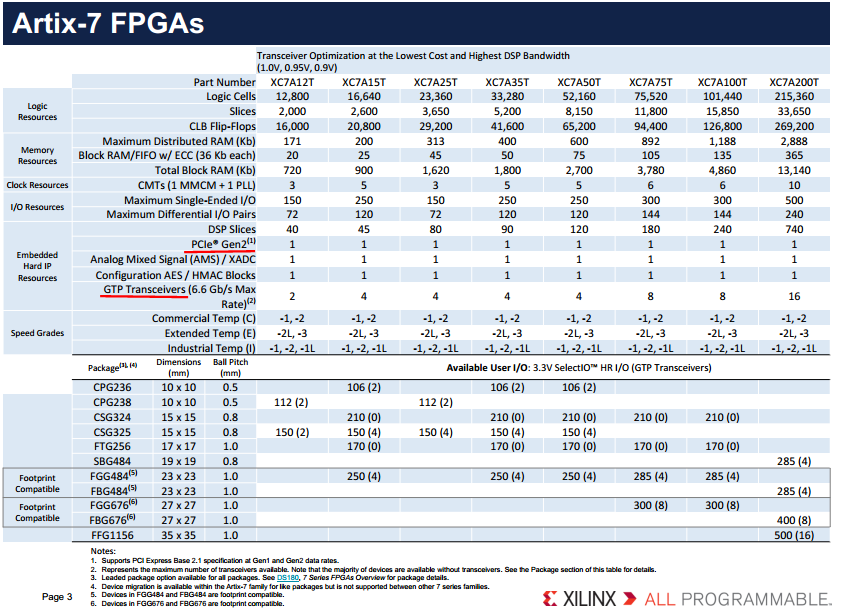

---->Artix-7---->增加了PCIE接口

---->增加了吉比特收发器接口

---->逻辑密度更大

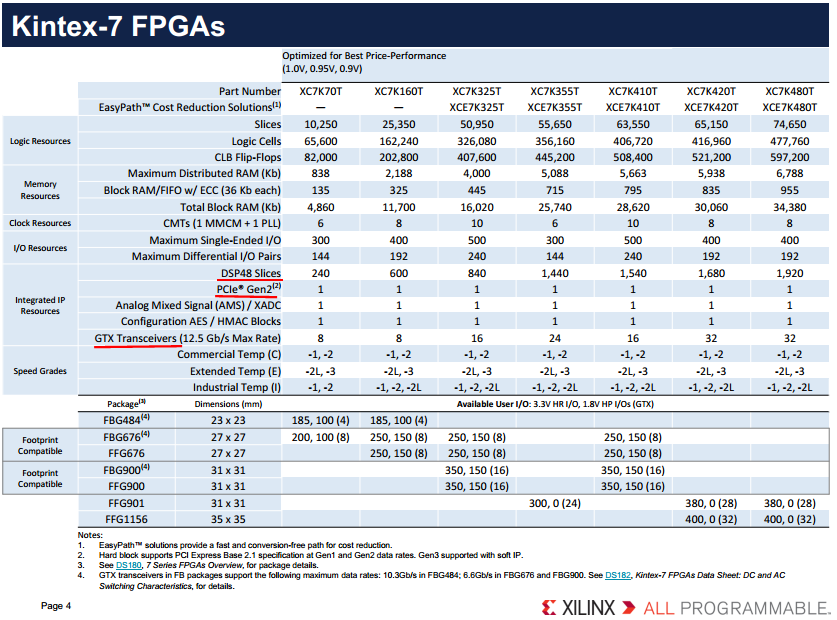

---->Kintex-7---->PCIE接口

---->DSP Slices升级为DSP48 Slices

---->GTP升级为GTX,速率更快

---->逻辑密度更大

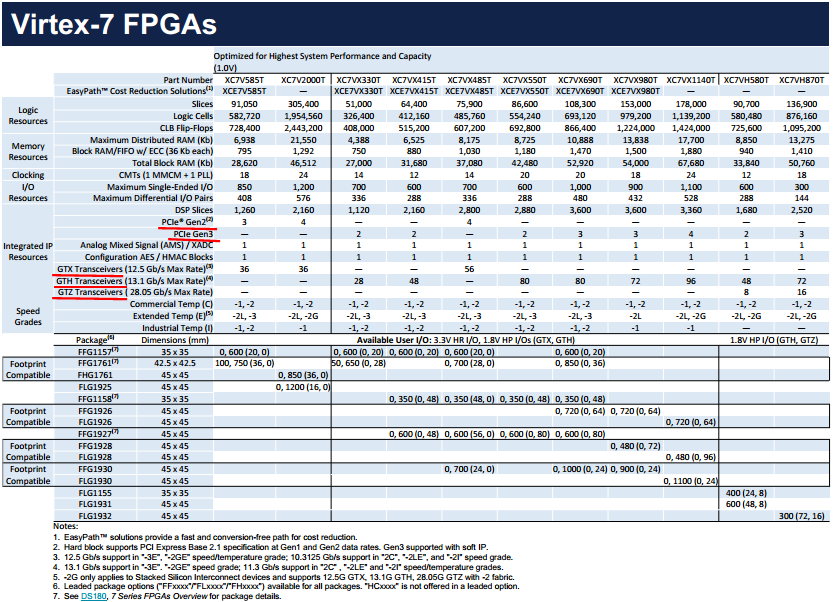

---->Virtex-7---->增强PCIE功能

---->增强GTP功能

---->逻辑密度更大

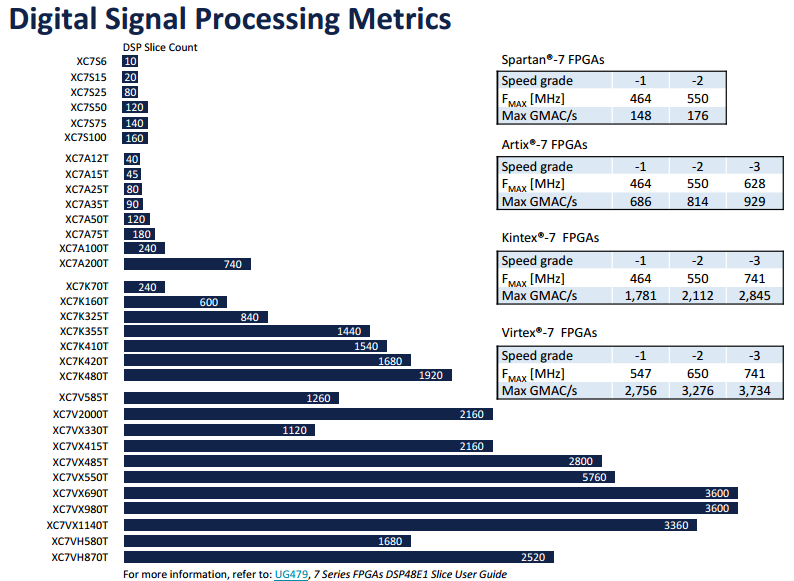

DSP数量对比:

BRAM数量对比:

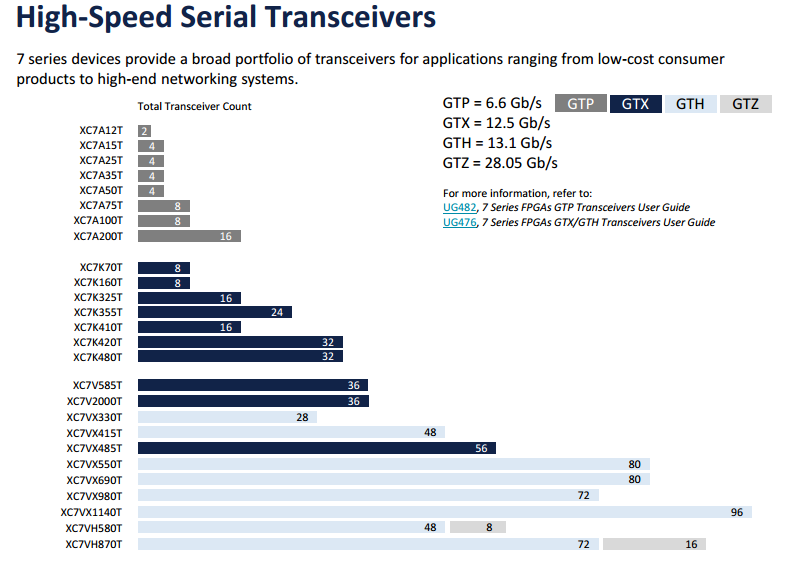

高速串行收发器对比:

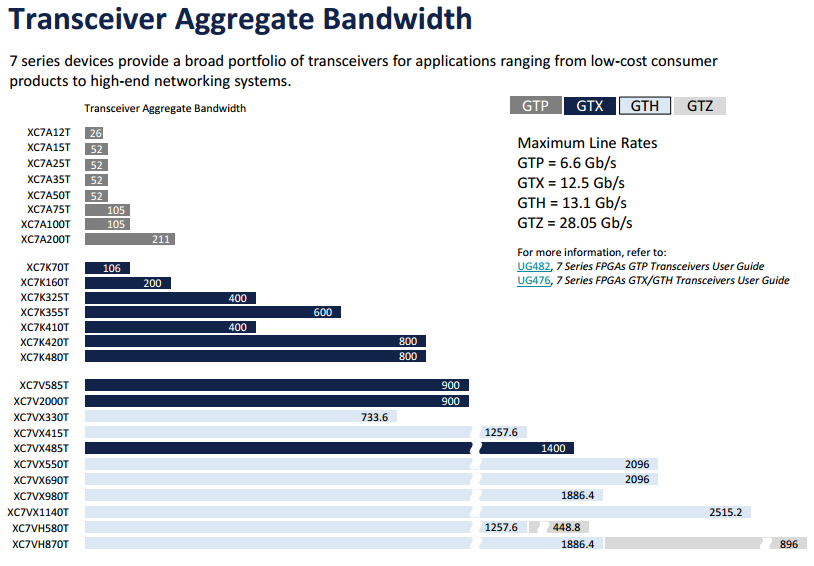

高速串行收发器总带宽对比:

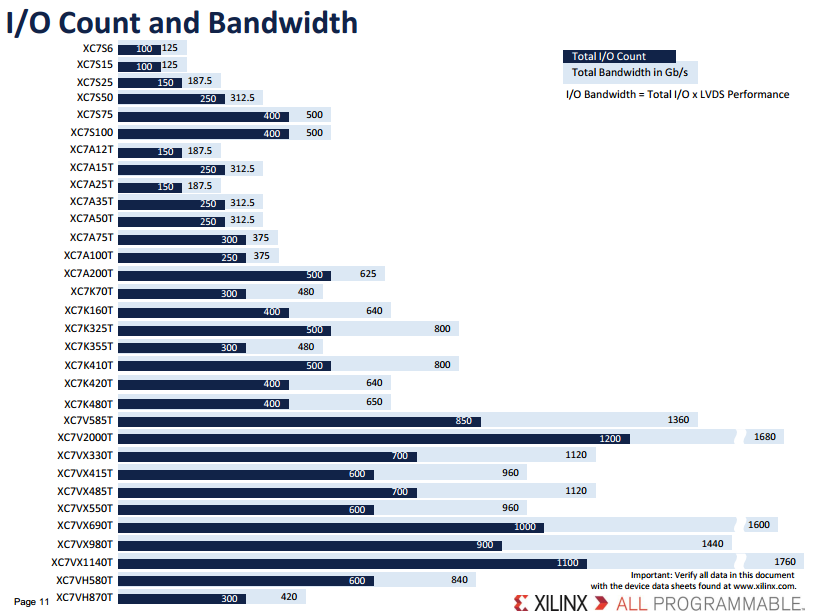

I/O数量与带宽对比:

Xilinx 7-Series特点---->28nm工艺

---->I/O带宽:2.9Tb/s

---->Logic Cell容量:2,000,000

---->DSP运算速度:5.3TMAC/s

---->功耗低

---->真正的6输入LUT,可用于分布式存储

---->36Kb双端口BRAM,内嵌FIFO逻辑以及片上数据缓冲

---->SelectI/O工艺,支持DDR3接口,速率可达每秒1866Mb

---->高速串行连接,速率从6.6Gb/s到28.05Gb/s,支持低功耗模式,优化芯片到芯片接口

---->用户可配置模拟接口,双12位1 MSPS(Million Samples per Second),片上温度/供电传感器

---->DSP slices---->25×18乘法器

---->48bit累加器

---->高性能滤波器

---->优化的均衡系数滤波器

---->CMT---->PLL

---->MMCM(混合模式时钟管理)

---->MicroBlaze CPU---->整数计算能力260 DMIPs~441 DMIPs

---->集成PCIe,x4 Gen2~x8 Gen3,适用于PCIe端点/根端口设计

---->存储器256位AES加密,HMAC/SHA-256验证,内嵌SEU检测与错误校验

---->环保高性能

---->1.0V/0.9V内核电压

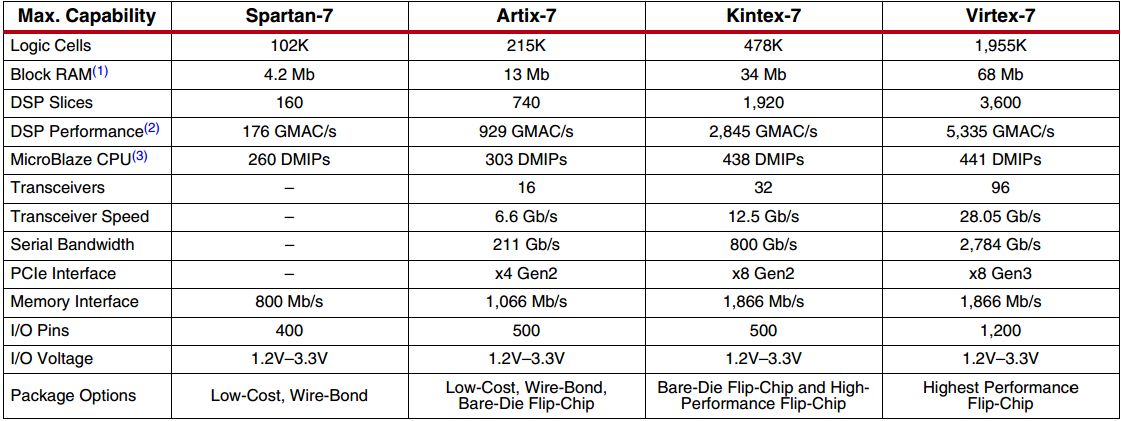

下面这张表更直观的表明了几类的区别:

一些概念:

---->SSI工艺---->使用了多超级逻辑域SLR---->超级高带宽连接性

---->低延迟

---->低功耗

---->两种---->逻辑加强型---->Virtex-7T

---->DSP/BRAM/收发器密集型---->Virtex-7XT/HT

---->高容量/高性能/短周期/低风险

---->超级长布线资源/超级高性能时钟线

---->CLBs---->真正6输入LUT---->可配制成一个6输入单输出LUT/64位ROM

---->2个5输入LUTs/32位ROMs---->各自有一个输出

---->共同的地址和逻辑输入

---->每个LUT输出可选的连接到触发器

---->4 LUTs+8 触发器+多路选择器+算术进位逻辑---->Slice

---->2 Slices---->CLB

---->8个触发器中的4个(每个Slice,每个LUT中的一个)---->锁存器latch

---->LUT可用作存储器---->所有slice的25%~50%使用它们的LUTs作为64位分布式RAM

---->LUT可用作寄存器和移位寄存器---->所有slice的25%~50%使用它们的LUTs作为32位移位寄存器SRL32或2个SRL16

---->时钟管理---->高速缓冲和布线

---->低抖动

---->频率合成和相移

---->低抖动时钟生成器

---->滤波

---->高达24个时钟管理通道CMTs---->MMCM---->分数计数器

---->固定或动态相移

---->PLL

---->频率合成器

---->时钟抖动滤波

---->中央有一个VCO---->频率大小和PFD传给VCO的电压有关

---->3个可编程频率分频器---->D---->输入预分频

---->M---->反馈分频

---->O---->输出分频

---->3个输入抖动滤波选项---->低带宽---->最好抖动衰减

---->高带宽---->最好的相位偏移

---->优化模式---->二者均衡

---->时钟分配---->6种不同的时钟线---->BUFG/BUFR/BUFIO/BUFH/BUFMR/高性能时钟

---->全局时钟---->32个全局时钟

---->可作为所有触发器的时钟

---->带使能/置位/复位

---->BUGH驱动的12根时钟线,可以在任意时钟域驱动

---->每个BUFH可以独立使能控制,所以可以在一个域内关掉时钟

---->可由全局时钟缓冲器驱动---->无故障时钟分配和全局时钟使能

---->由CMT驱动---->消除时钟分布延迟

---->域时钟---->驱动域内所有时钟目标

---->域定义指50 I/O和50 CLB和半芯片宽度的范围

---->7系列可以有2~24个域

---->每个域有4个域时钟通路

---->域时钟缓冲器由4个时钟输入引脚驱动,同时可以进行1~8分频

---->I/O时钟---->快速

---->作为I/O逻辑或串行化/去串行化电路

---->I/O可直接连接MMCM

---->Block RAM---->双端口,72位,36kb BRAM

---->可编程FIFO逻辑

---->错误校验电路

---->5到1880个

---->读写同步操作

---->可编程数据位宽

---->DSP Slice---->25 × 18 二互补乘加器48位高分辨率单乘加器

---->单指令多数据运算单元SIMD/2操作数10个不同逻辑功能的逻辑单元

---->省电预加器

---->均衡滤波器

---->流水线/ALU/专用总线级联

---->up to 741MHz

---->48位模式检测器

---->高速度/高效率

---->动态总线转换器

---->内存地址发生器

---->总线复用器

---->I/O口存储器映射寄存器

---->累加器可用作同步加减计数器

---->输入输出---->SelectIO工艺

---->1,866Mb/s DDR3接口

---->片内高频去耦电容器增强信号完整性

---->支持多种I/O标准

---->HR IO---->宽电压范围(1.2V~3.3V)

---->HP IO---->高性能操作

---->以Bank组织,每Bank 50引脚

---->每Bank由VCCO共同供电

---->有些单端输入缓冲器需要外部参考电压VREF

---->每Bank有2个VREF引脚(配置Bank 0除外)---->只能有一个VREF电压值

---->多种封装

---->电气特性---->上下拉输出结构

---->可以设为高阻态

---->可以设置压摆率和输出强度

---->可以设置上拉和下拉电阻

---->引脚对可以设置为差分输入输出

---->可以设置100欧姆内部端接电阻

---->多种差分接口标准:LVDS,RSDS,BLVDS,差分SSTL,差分HSTL

---->每个IO口支持存储器接口标准

---->T_DCI可以控制输出驱动阻抗---->串联端接/并联短接

---->节省线路板空间

---->输出模式或三态模式端接会自动关闭

---->IBUF和IDELAY有低功耗模式

---->8-bit IOSERDES 可完成串并与并串的转换---->可编程宽度2到8位

---->支持相邻引脚级联

---->专用过采样模式用于数据恢复---->如SGMII接口

---->低功耗吉比特收发器

---->集成PCIE接口

---->配置

---->模数转换