- 1【EMNLP2021&&含源码】「自然语言处理(NLP)」跨度提取QA形式算法改进_enhanced language representation with label knowle

- 2GAT-图注意力网络_gat图注意力网络

- 3PatchTST:时间序列预测的突破 从理论到实践,了解 PatchTST 算法并将其与 N-BEATS 和 N-HiTS 一起应用在 Python 中

- 4NLP语义引擎改变直播行业的一种方式

- 5短剧机器人插件

- 6基于人脸面部检测的口罩识别系统_基于人脸识别的口罩检测系统的设计

- 7一文详细介绍什么是数据标注?

- 8与或树的盲目搜索和启发式搜索_与或树的启发式搜索例题

- 9深度学习的最佳入门路线

- 10【金融科技前沿】【长文】金融监管、监管科技以及银行业监管报送概述_银行监管报送业务知识

FPGA DDR4 学习(一)_ddr4 fpga

赞

踩

目录

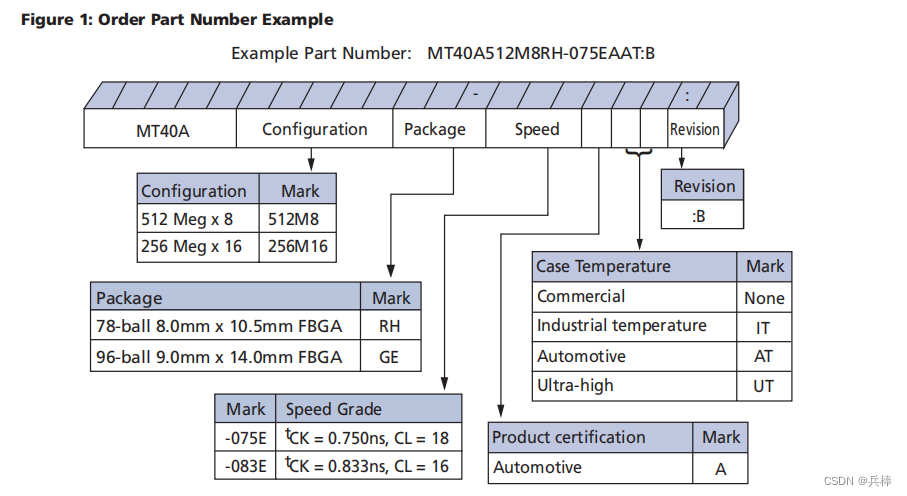

一、DDR型号解读

如MT40A512M8RH-075EAAT:B型号为例:

1.MT40A:系列名称。

2.512M8:内存与位宽,512*8/1024=4Gb。

3.RH:packege包装。

4.-075E:速度,Tck=0.75ns。

5.A:产品标识。

6.AT:外壳温度。

7.:B:模具修订。

以上需要着重了解的是512M8,理解每个型号的内存大小和位宽。

二、了解DDR4的存储

这是512M8的内存图

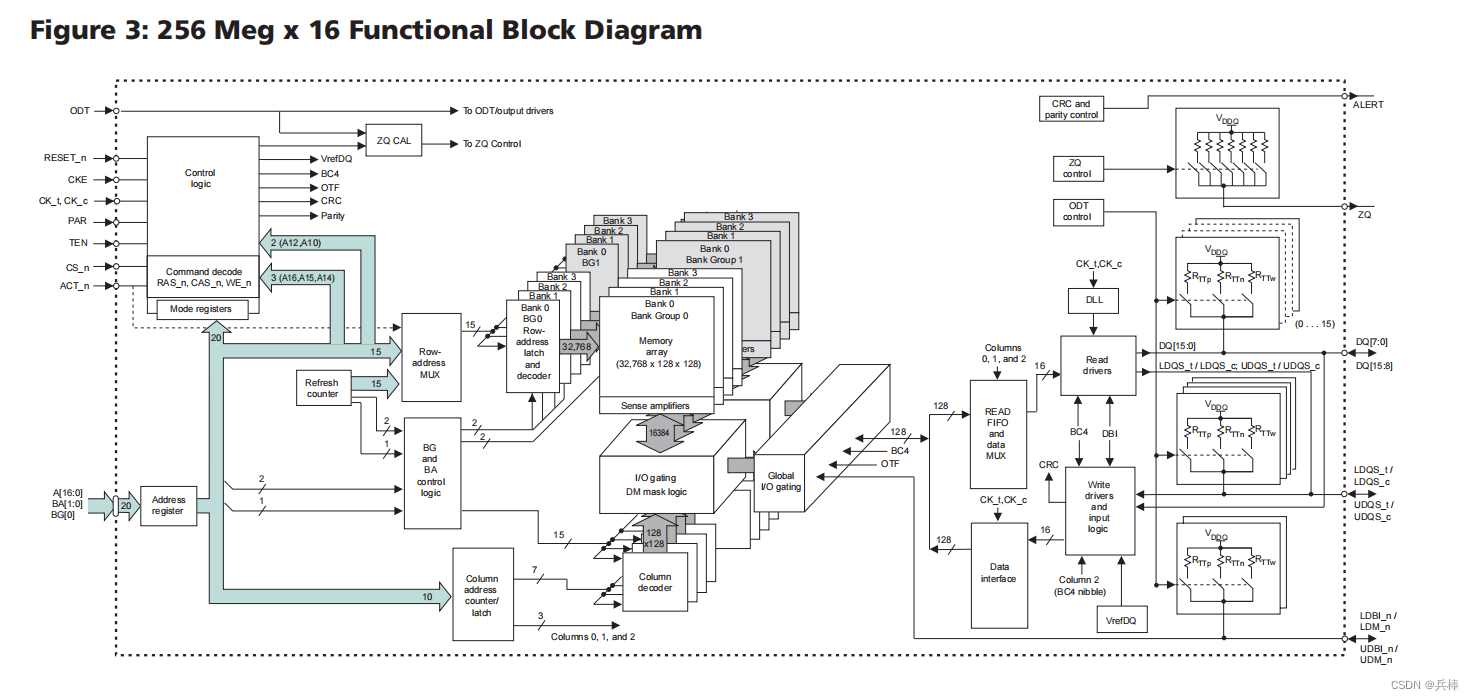

这是256M16的内存图

这两张图最终的内存大小都是4Gb,只是方式不同。

三、引脚功能

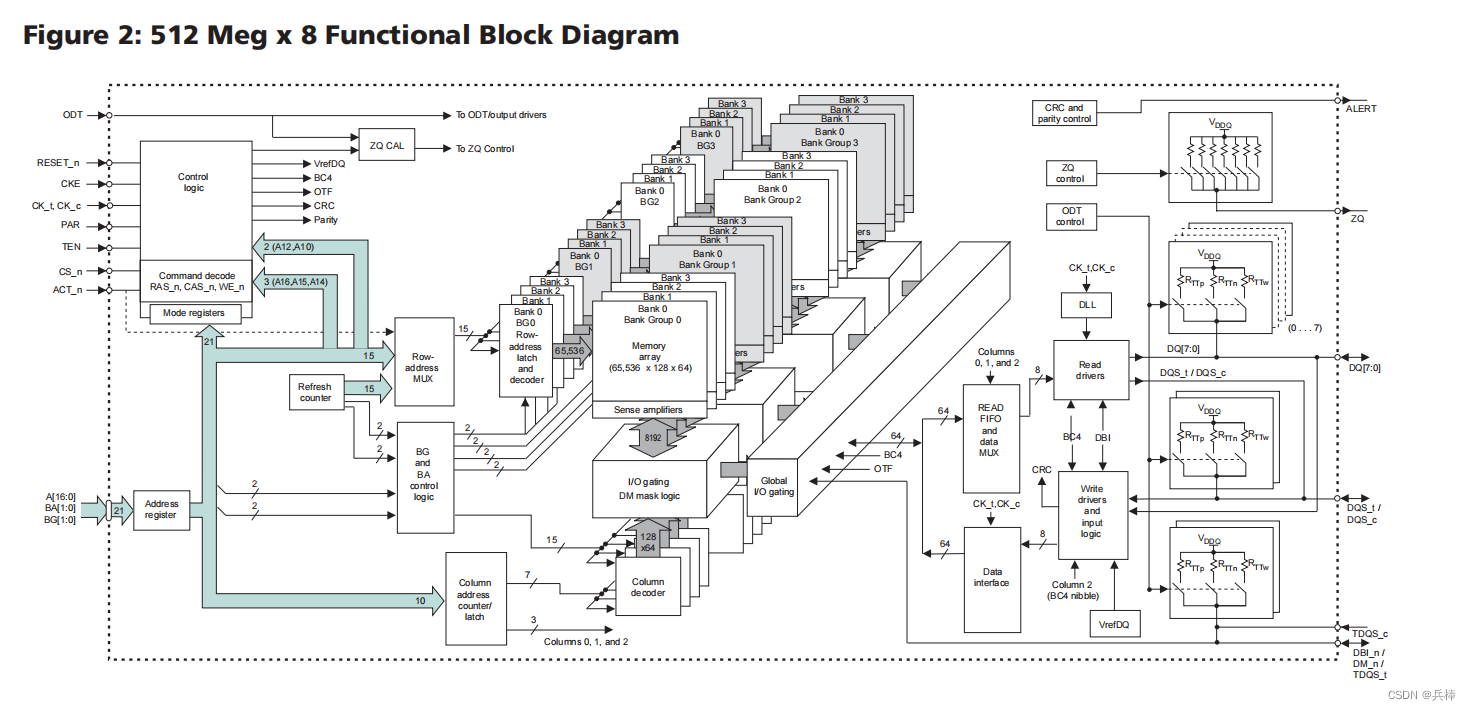

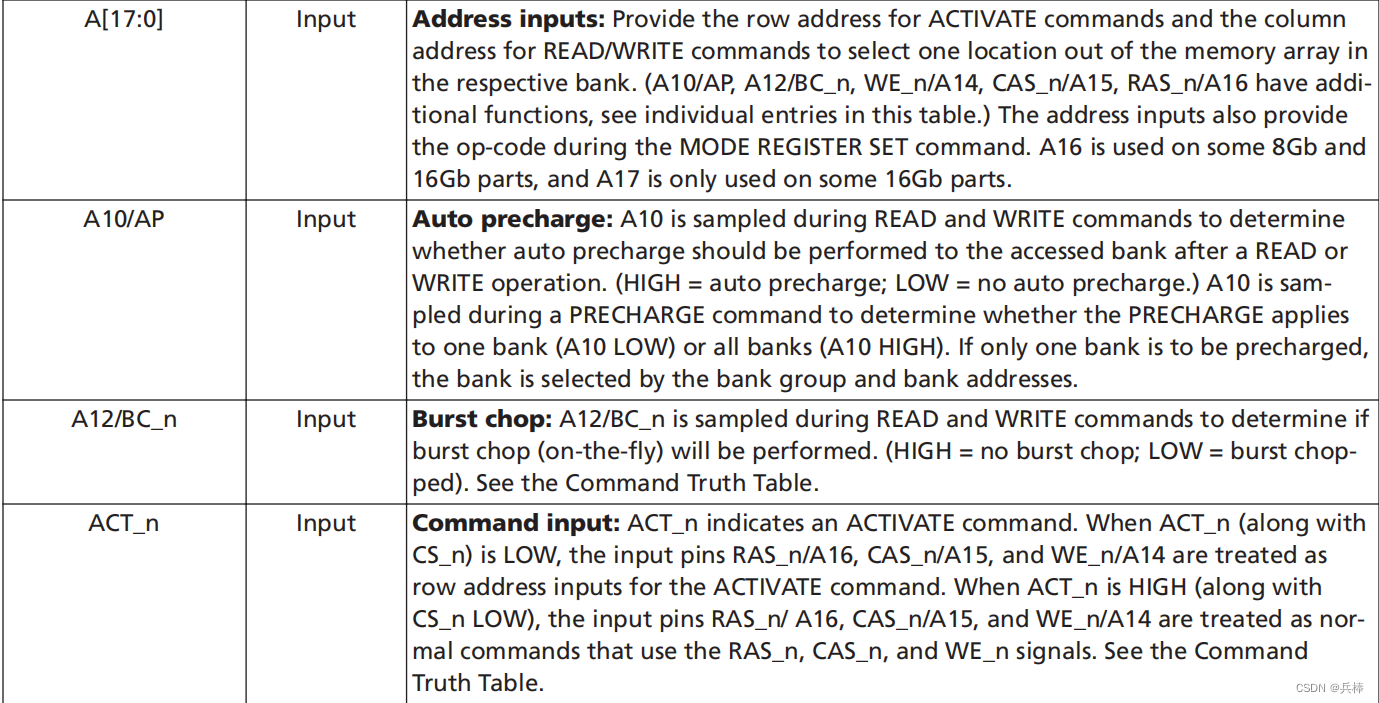

A[17:0]地址,不是所有都是18个地址引脚,有的只有17个,有的只有16个,因DDR4型号而定。其中A14是写选通信号,A15是列选通信号,A16是行选通信号,值得注意的是选通信号是低电平选中,高电平无意义。

AP,BC_n:预充电和爆片,一般用不到不需要了解,但预充电还是会与你的读写有一定的关联。

ACT_n:选通信号,低电平选中,高电平时将A14\A15\A16三个地址引脚作为地址线。

BA[1:0]:bank,每个型号都有自己想对应数量的bank,在写入和读出的时候bank起到很重要的作用。

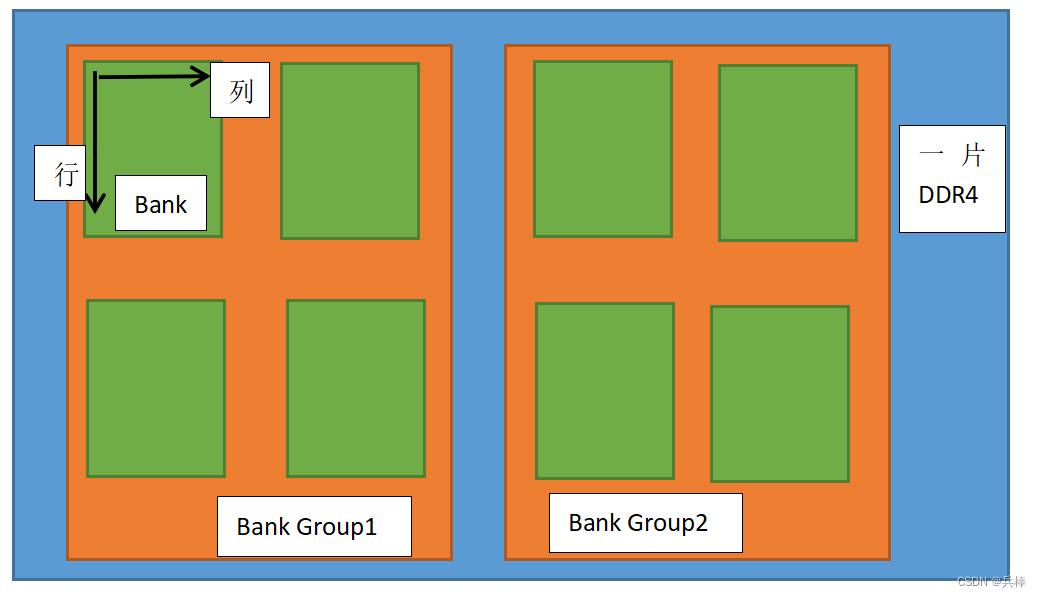

BG[1:0]:存储组,在DDR4中将一个存储模块分为几个存储组,然后再分为各个bank模块。

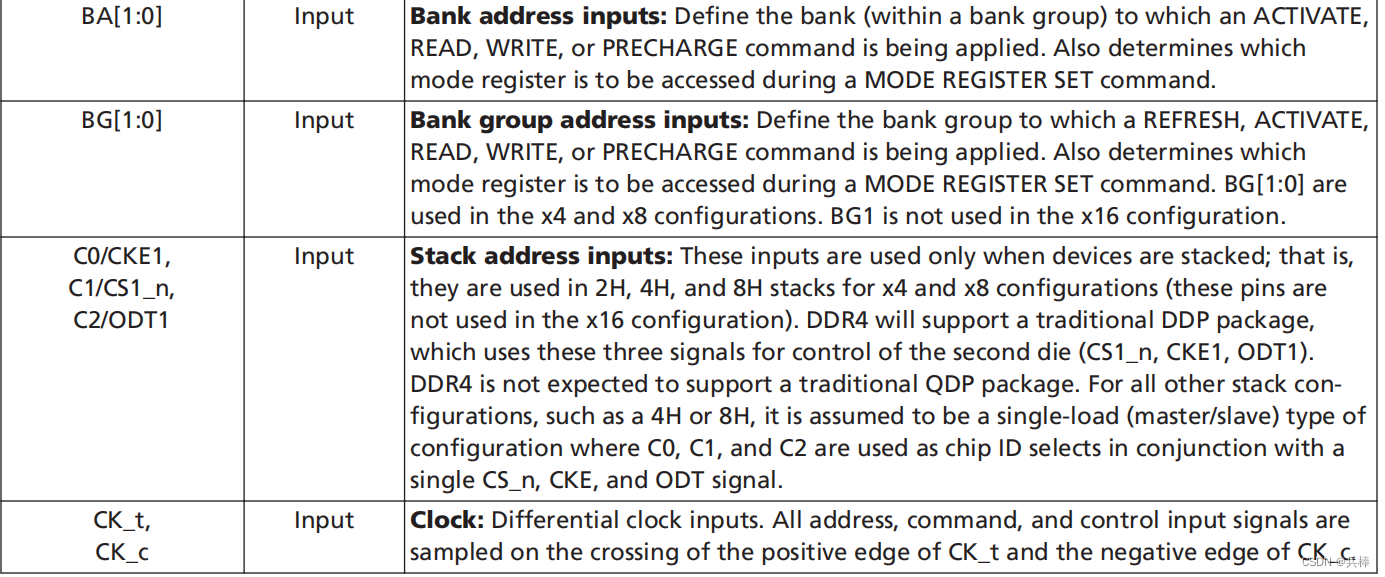

C0:时钟使能,高电平表示此时时钟有效。C1:片选选通信号,可以通知各个片选,以及当为高电平时会让所有的命令无效。C2:控制输出电平大小,保证信号完整性。

CK_t\CK_c:差分时钟,给DDR4的时钟。

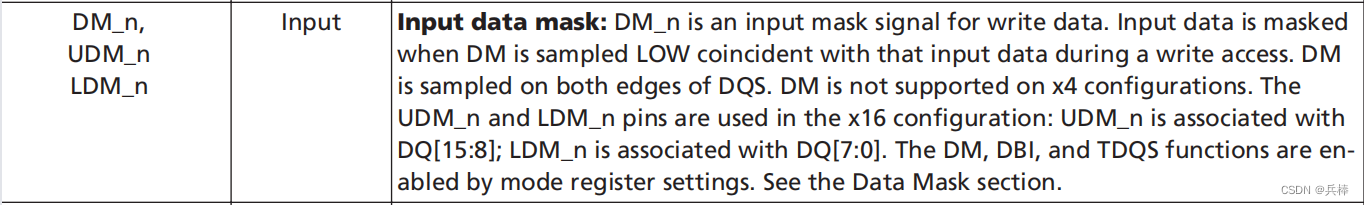

数据掩码部分

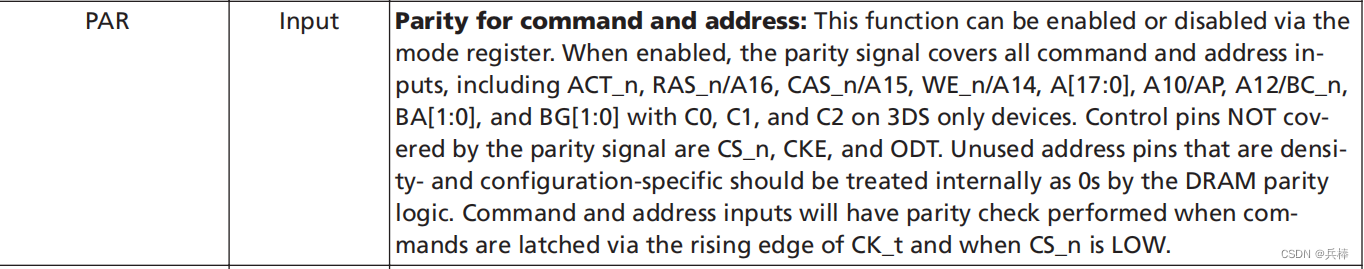

奇偶判断部分

奇偶判断部分

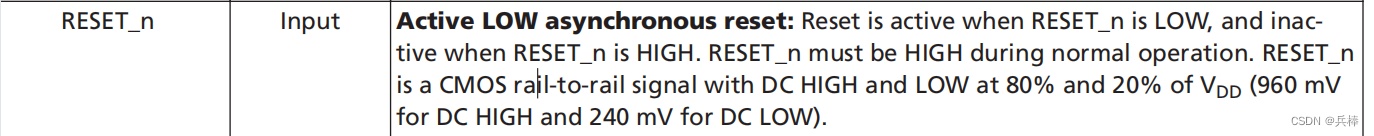

低电平异步复位

四、了解ddr4的储存过程

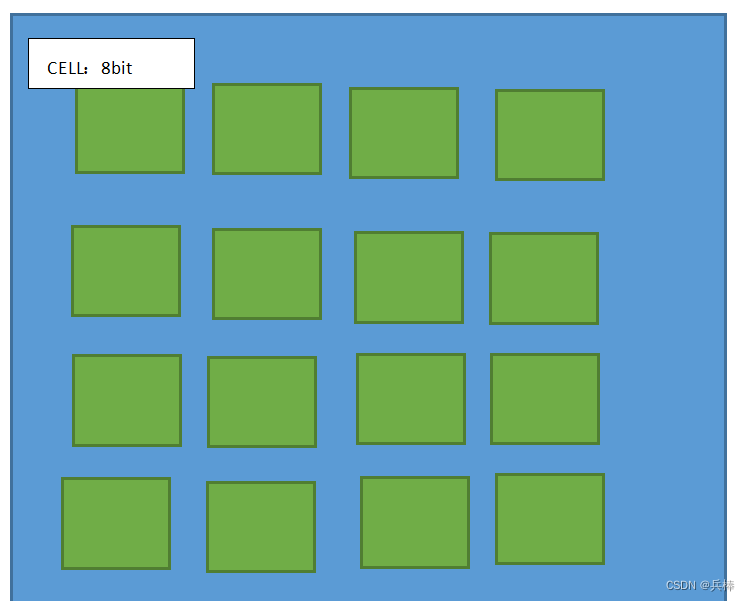

首先将一个ddr4存储片拿来,将其分为多个存储组(Bank Group),再将一个 Bank Group分为多个bank,bank内再分行和列,在每一列中有16个Cell单元并联,有因为DDR4的数据有16跟数据线,所以依次对应每一个Cell单元,每个单元可以存8bit数据也就是1个字节。