- 1无人机航摄时航高与地面分辨率的关系

- 2【AIGC调研系列】测试工程师如何拥抱AIGC的发展_aigc对测试工作的帮助

- 3Bert模型介绍及代码解析(pytorch)_bert代码

- 4Appium+python自动化(二)- 环境搭建—下(超详解)_windows python appium教程

- 5大模型在文本分类与聚类中的应用与优化

- 6如何应用 AI 进行软件测试?_百度 ai 创建 测试用例

- 7CPU上安装ollama和部署开源Llama2-chinese模型_ollama cpu

- 8RabbitMQ工作模式以及java代码实现_mq java最佳实现

- 9小说推文怎么制作视频呢?

- 10Paddle实现人脸对比

【FPGA】Modelsim的使用方法_modelsim使用教程

赞

踩

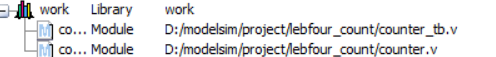

Modelsim的使用方法

1新建库

File->New->Library…

Create:选择创建的库,一般选择第三项。

Library Name:库的名字,一般以字母下划线命名。

Library Physical Name:默认。

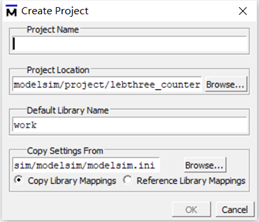

2新建工程

File->New->Project…

Project Name:工程名,不要出现中文字符,空格,一般以字母或下划线命名。

Project Location:文件保存路径,点击Browse,选择路径,最好每个工程建一个文件夹。

其他默认,点击ok完成创建。

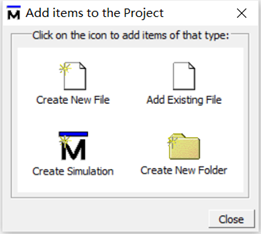

3.弹出下面框图,添加/新建文件:

如果已经有要仿真的文件点击Add Existing File打开文件,如果没有则新建新的文件。

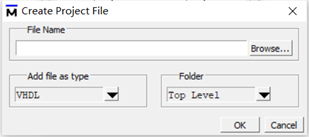

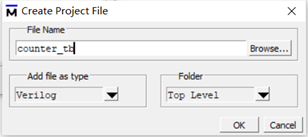

4.新建文件(首先说明这个框图包含的内容)

Create New File:

File Name:文件名字,一般以字母、数字、下划线命名,注意不要出现空格和中文字符。

Add file as type:文件类型,默认位VHDL,我们创建的是verilog,选择verilog。

Folder:默认。

(我们要新建两个文件一个是源文件,一个是testbench源文件)

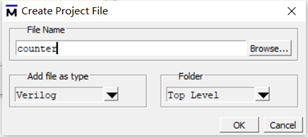

5.新建源文件

Create New File->输入文件名字(一般以要完成的电路英文简写命名)->选择verilog文件->OK

6.新建testbench文件

Create New File->源文件名字_tb(说明是testbench文件与源文件所区分)->选择verilog文件->OK

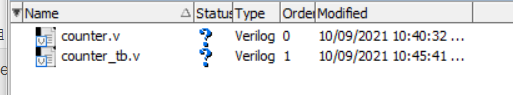

7.创建完成:

在project图窗可以看到创建的两个文件,如果没有project图窗:View->勾选project(x)

8.编写源文件

双击打开创建的源文件counter.v进行编写。

常见问题:双击后是默认用其他软件打开的,比如我下载了AltiumDesigner软件,双击打开文件是用AltiumDesigner软件打开的

解决方法:找到文件存放的位置,找到对应文件->右键->打开方式->选择Modelsim,将默认用该应用打开.v文件的勾选框勾上即可。

(这里以8位记数器为例)

module counter( //Module naming input clk, //Declarations of input and output variables. input reset, output reg [7:0] count ); /*It also includes the definition of parameters and declarations of other variables used in the file.*/ always@(posedge clk) //Function realization code. begin if (count===8'bxxxxxxxx)count=8'b0000_0000; if(!reset) count<=8'b0000_0000; else if(count==8'b1111_1111) count<=8'b0000_0000; else count<=count+1; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

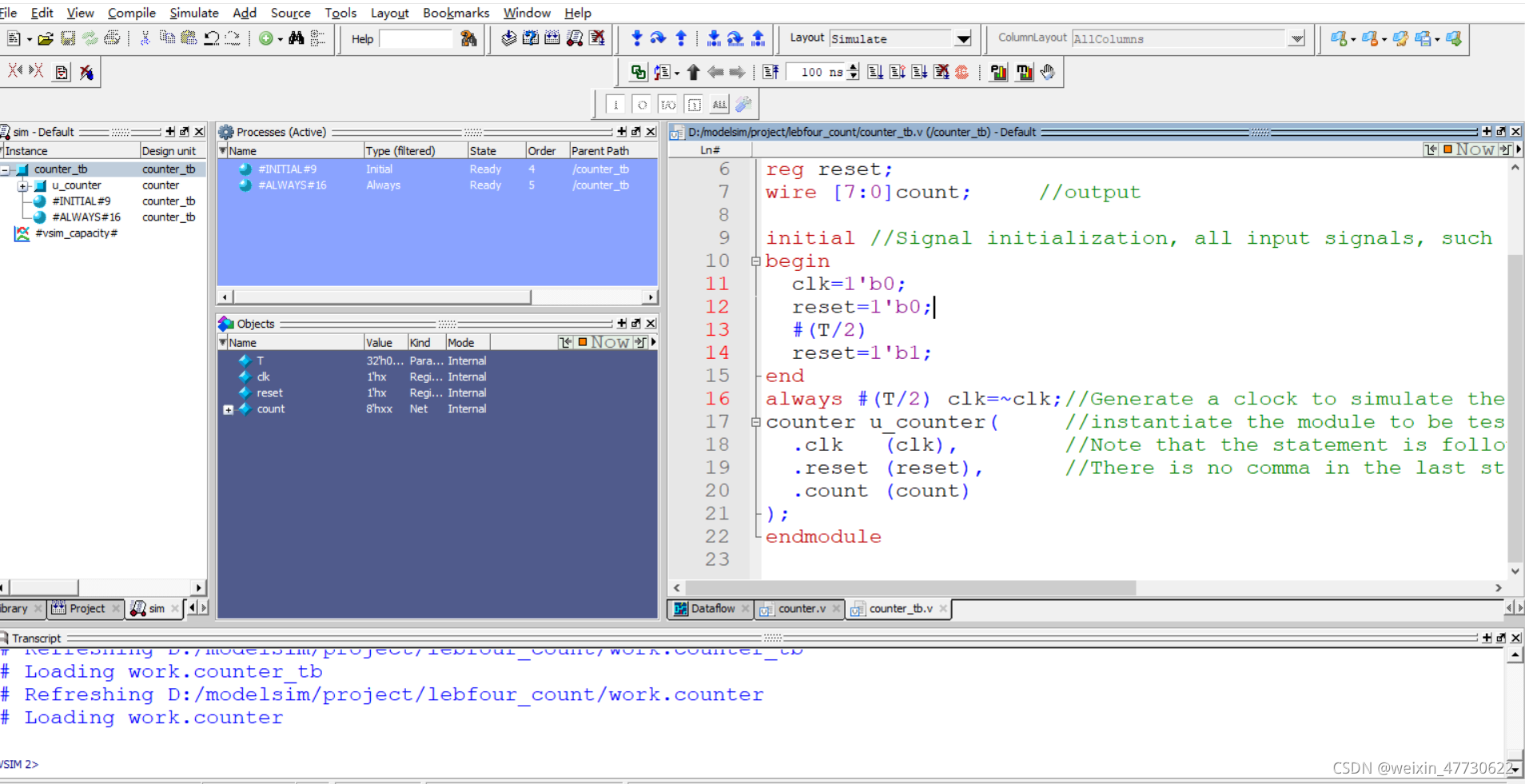

9.编写testbench文件

`timescale 1ns/1ns //Time unit/time precision. module counter_tb; //Testbench module name, usually named after this file. parameter T=20; //parameter definition reg clk; //input reg reset; wire [7:0]count; //output initial //Signal initialization, all input signals, such as clock and reset signal. begin clk=1'b0; reset=1'b0; #(T/2) reset=1'b1; end always #(T/2) clk=~clk;//Generate a clock to simulate the actual cycle timing of the crystal oscillator. counter u_counter( //instantiate the module to be tested. .clk (clk), //Note that the statement is followed by a comma. .reset (reset), //There is no comma in the last step. .count (count) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

10.特别注意:上面两个文件,在编辑或者修改以后,一定要按ctrl+s或者保存按键进行保存。(很重要,不保存编辑修改的地方就不起作用)

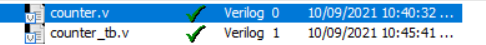

11.编译文件:

Compile->Compile All

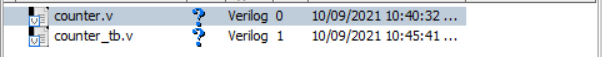

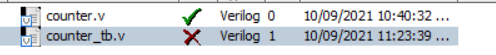

project图窗中可以看文件的编译状态:

问号:修改编辑后未编译。

绿色对勾:编译成功

红色叉号:编译失败

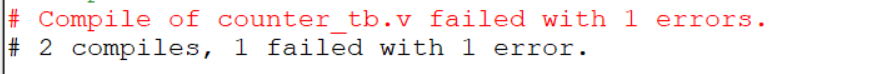

要学会看编译的错误:(要学会查看Transcript框中的报错)

说明.v文件中存在一个错。

双击报错红色字体部分:

弹出报错框:经分析可以看出在_tb.v文件中第一行:接近“timescale”关键字附近出现的错误

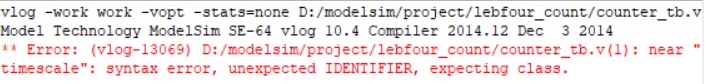

这里说一个很常见的错误:testbench文件中,·timescale前的点是键盘上数字1左边的那个点。修改后

:不再报错。

12.仿真

Simulate->Start Simulation(出现如下窗口)->点击我们最开始(步骤1)建的库work左边的±>出现下面第二张图->点击_tb文件->取消勾选Optimization->点击OK

13.仿真完成

13.打开波形:

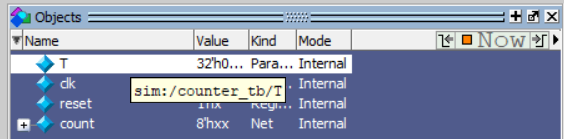

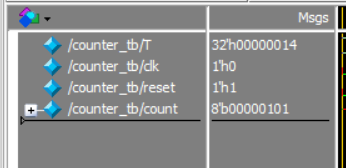

在Object框中,选择要观察的波形,比如示例的8位计数器,需要显示时钟信号(clk),清理信号(clr)和计数输出信号(count)(如下图)->右击->Add to->Wave->Selected Signal

出现波形仿真界面:

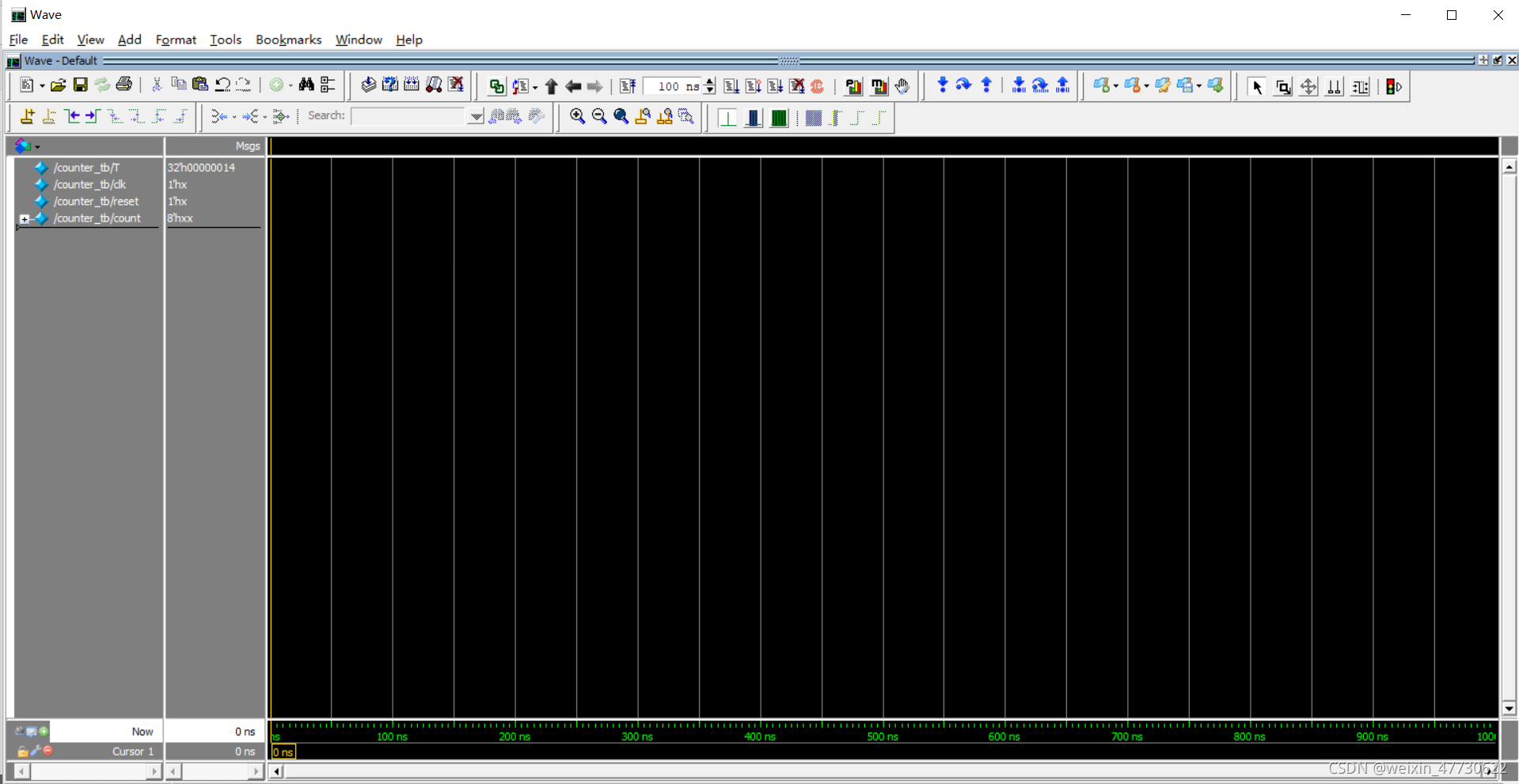

14.仿真波形:

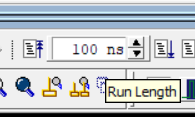

设置仿真时间(代码中时间单位是1ns(见步骤9中代码第一句),这里就设置了100ns)

->点击Run

出现波形:

放大缩小显示时间间隔:

修改显示变量波形的进制数:右击Msgs中要修改进制数的变量->Radix->选择显示进制数

15.结语:

以上只是一些常见的操作,部分操作还有很多简便的方法,希望可以和大家进行交流学习,有问题的地方希望大家能够指点。以后还会持续跟新过程中常见的问题一级代码的具体编辑,希望能和大家一起学习。