热门标签

热门文章

- 1Java spring boot 项目和python flask项目 开启 https 请求_flask keystore

- 2基于Python爬虫河南洛阳景点数据可视化系统设计与实现(Django框架) 研究背景与意义、国内外研究现状

- 3大数据中台架构以及建设全流程一(Paas层设计)

- 4自然语言处理以及对话系统知识点总结_自然语言对话系统

- 5人工智能之启发式搜索算法_人工智能之启发式搜索算法头歌求解8数码问题

- 6成功解决java.lang.OutOfMemoryError: Java heap space错误

- 7本科论文查重会检测AI辅写疑似度吗?全面解析查重机制_查重软件可以查出ai相似度吗

- 8基于ChatGPT4学习大模型day1

- 9HarmonyOS 4.0 开发教程下载

- 10用 AI 驱动创意,Unity 推出 Unity Muse 与 Unity Sentis

当前位置: article > 正文

使用modelsim设计4位全加器,并调出波形图和电路图(详细教程)_modelsim怎么看电路图

作者:我家自动化 | 2024-04-09 06:34:17

赞

踩

modelsim怎么看电路图

OK , Let’s begin

一、仿真

四位全加器的代码如下

add4的代码

module add_4

(

input[3:0] a,b,

output[3:0] sum,

output cout,

input cin

);

assign{cout,sum} = a+b+cin;

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

adder4_test的代码

module adder_4(); wire[3:0] sum; wire cout; reg[3:0] a,b; reg cin; initial begin #0 a = 4'b0001; b = 4'b1010; cin = 1'b0; #5 a = 4'b0010; b = 4'b1010; cin = 1'b1; #5 a = 4'b0010; b = 4'b1110; cin = 1'b0; #5 a = 4'b0011; b = 4'b1100; cin = 1'b1; #5 a = 4'b0111; b = 4'b1001; cin = 1'b0; #5 a = 4'b0001; b = 4'b1100; cin = 1'b1; #5 a = 4'b0011; b = 4'b1100; cin = 1'b0; #5 a = 4'b0111; b = 4'b1111; cin = 1'b1; #5 $finish; end add_4 u1(.a(a),.b(b),.cin(cin),.sum(sum),.cout(cout)); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

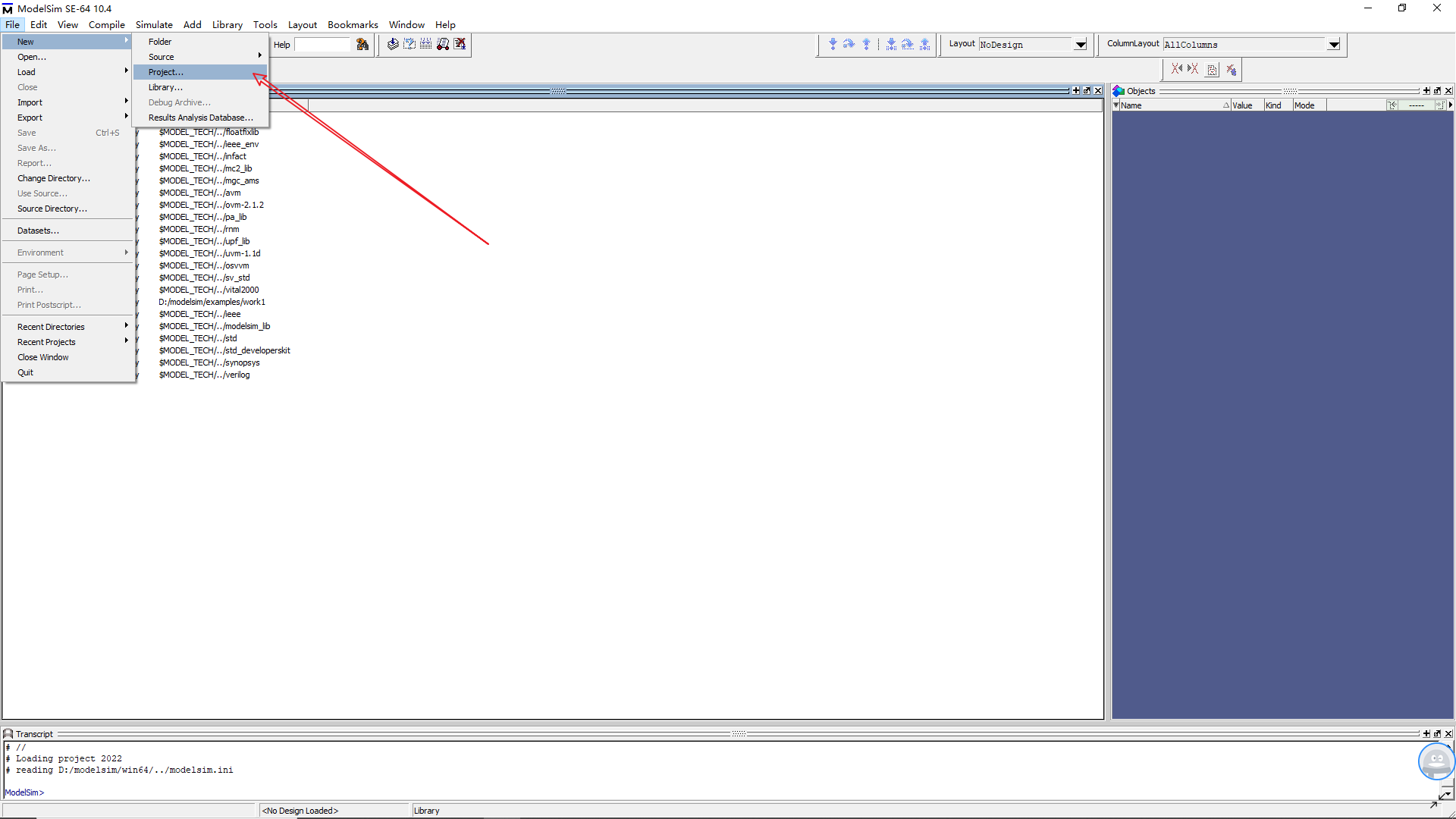

1、打开modelsim10.4

选择file,选择New --> project

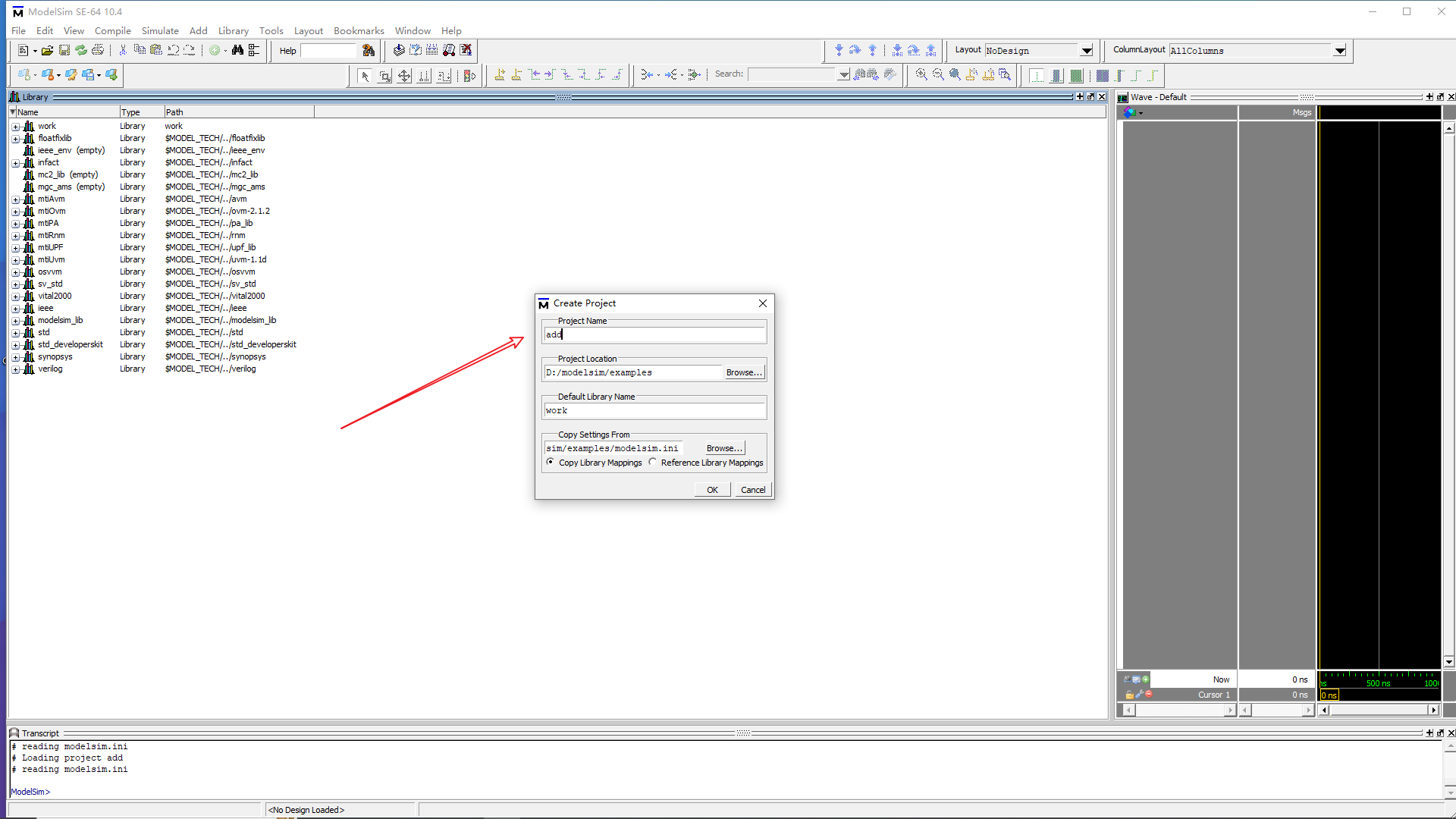

2、文件名可以自定义,这里命名为add

(注意不能用中文)

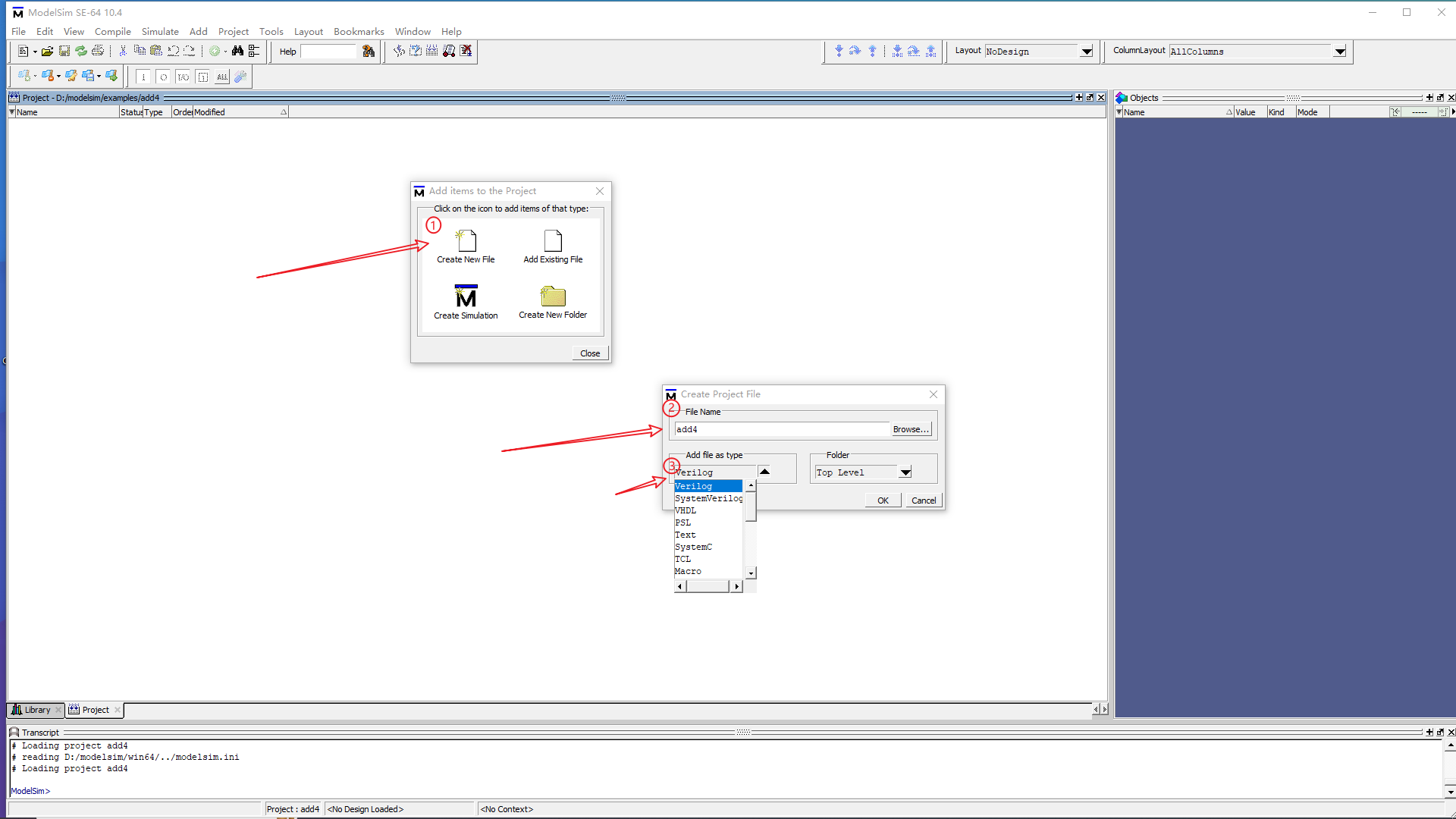

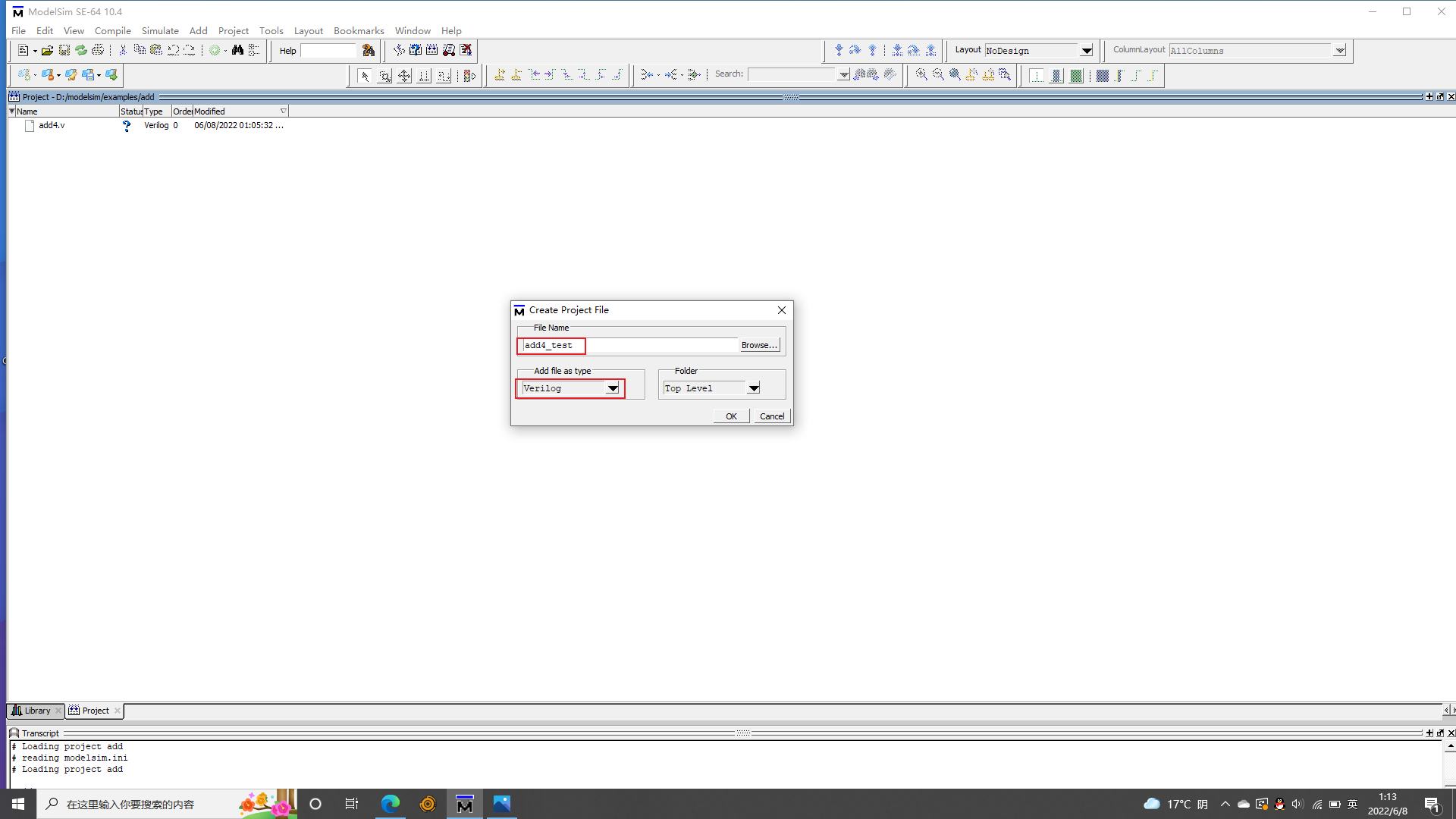

3、选择create new file,创建一个为add4.v的文件

选择文件类型为Verilog

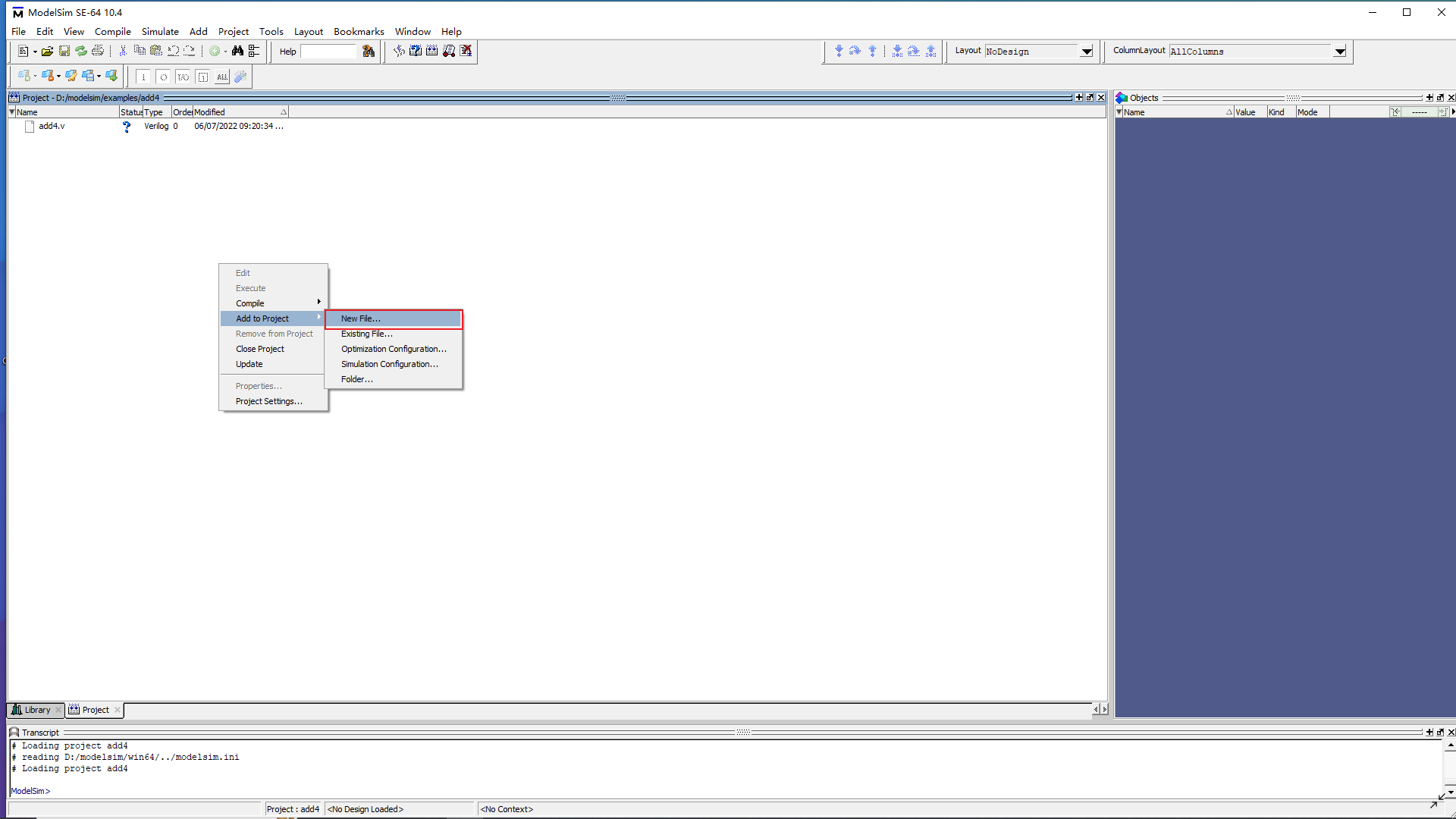

4、右键添加文件add4_test, 重复上述操作即可

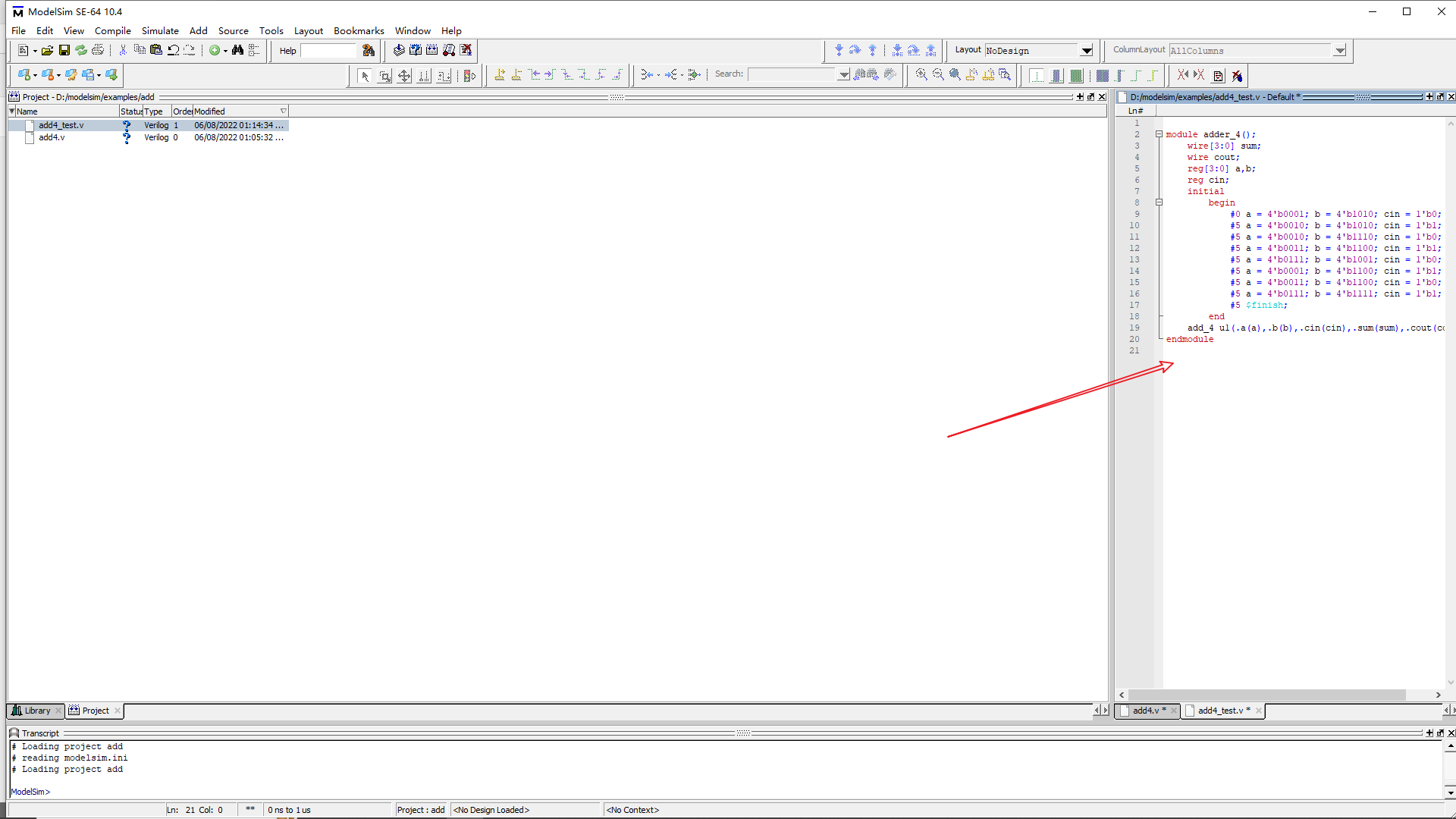

5、双击选中项目,将文章开头的两个代码分别复制到右边的代码框中

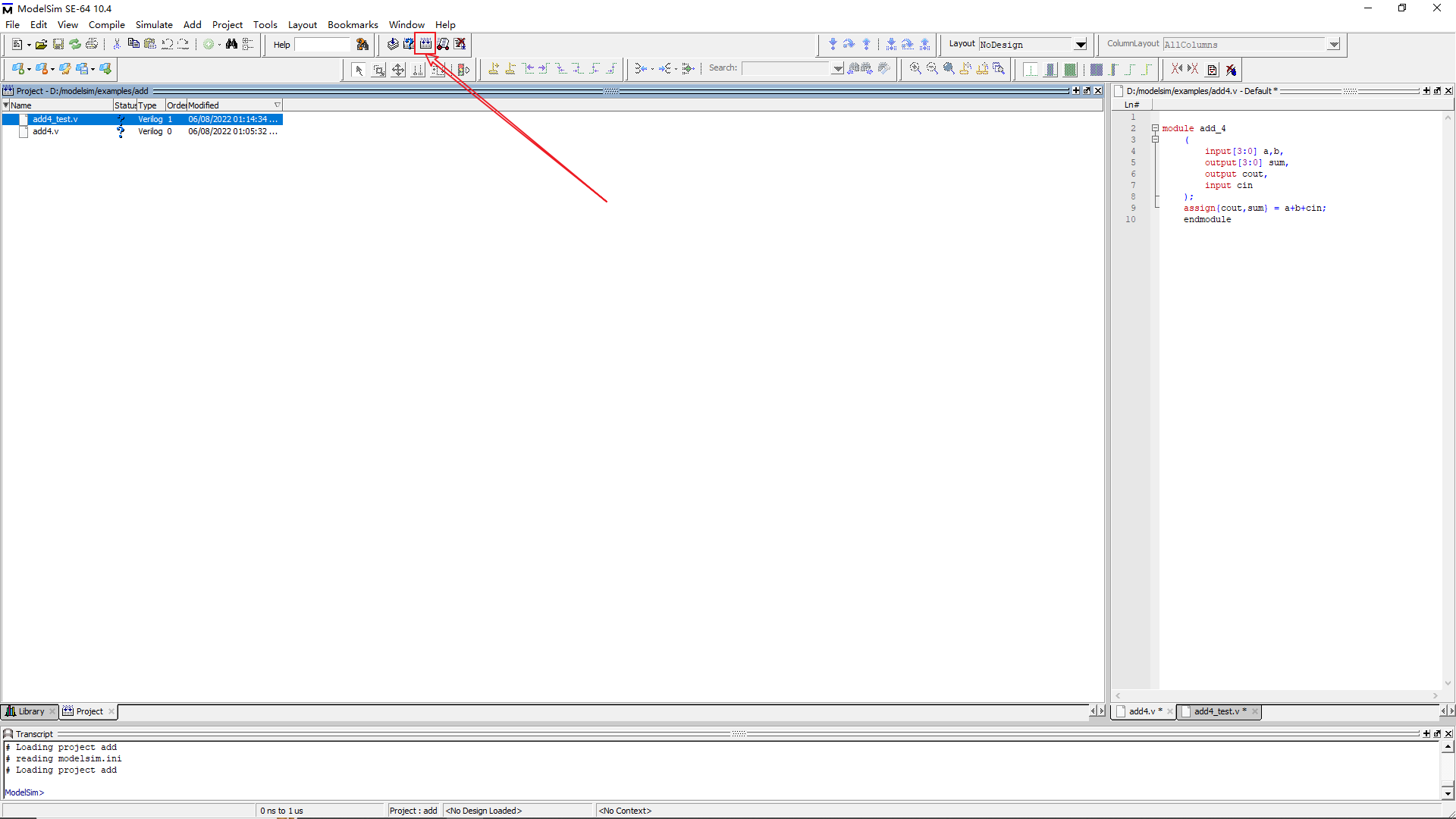

6、点击编译

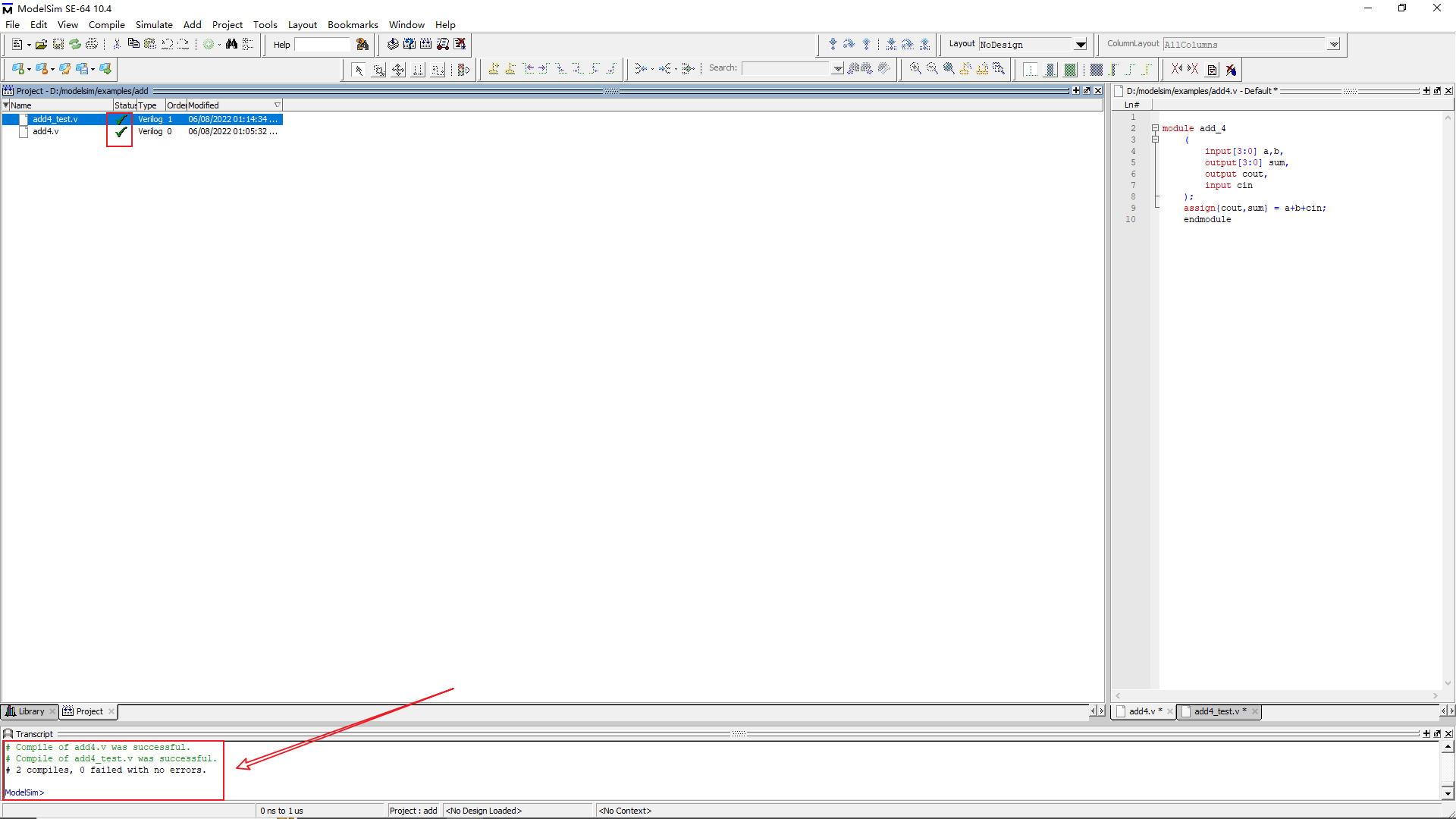

7、编译完成后会显示0错误,0警告

然后就可以进行下一步了

点击Library

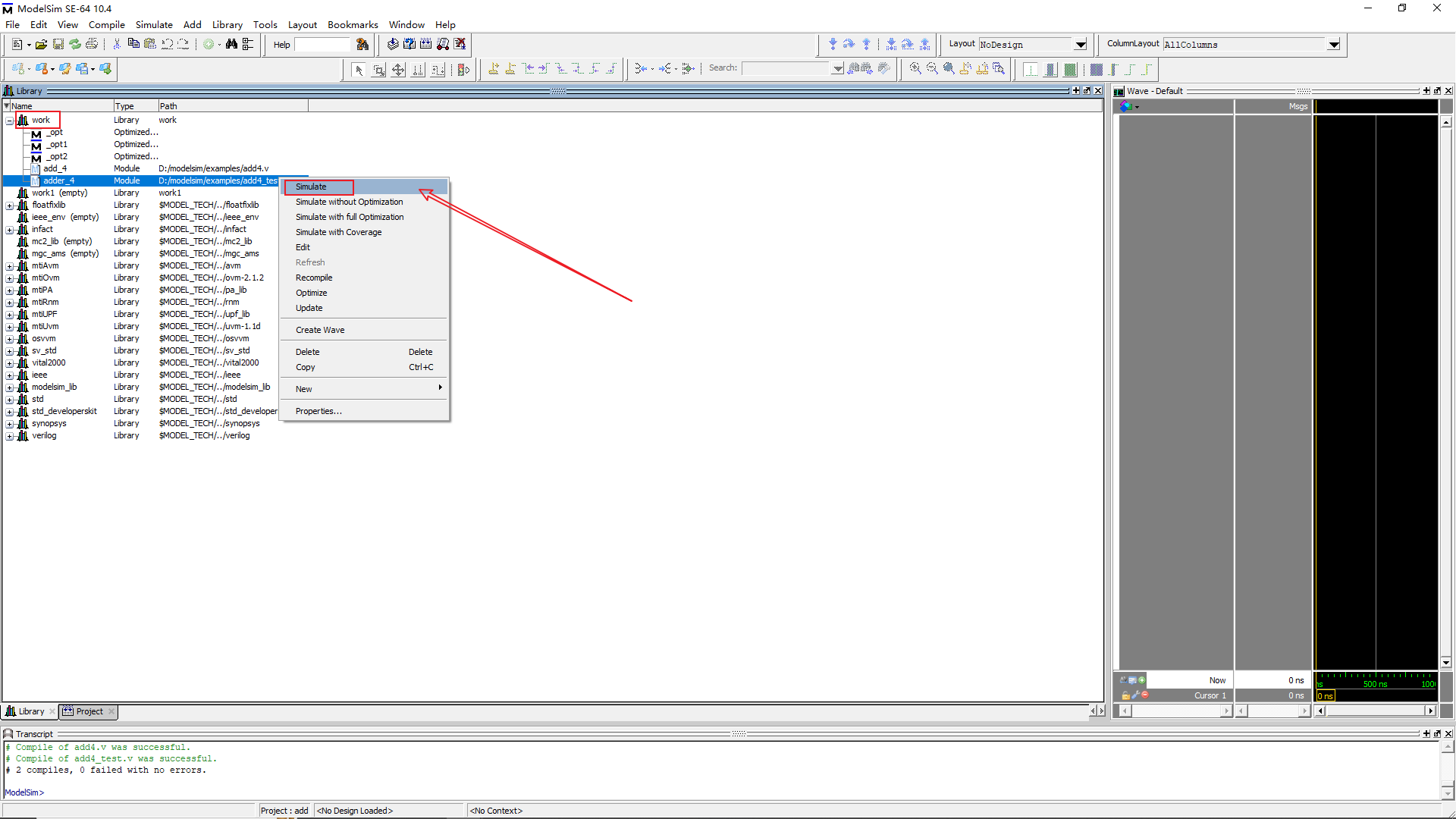

8、进行仿真

展开work的组

右键对测试文件add4_test进行仿真

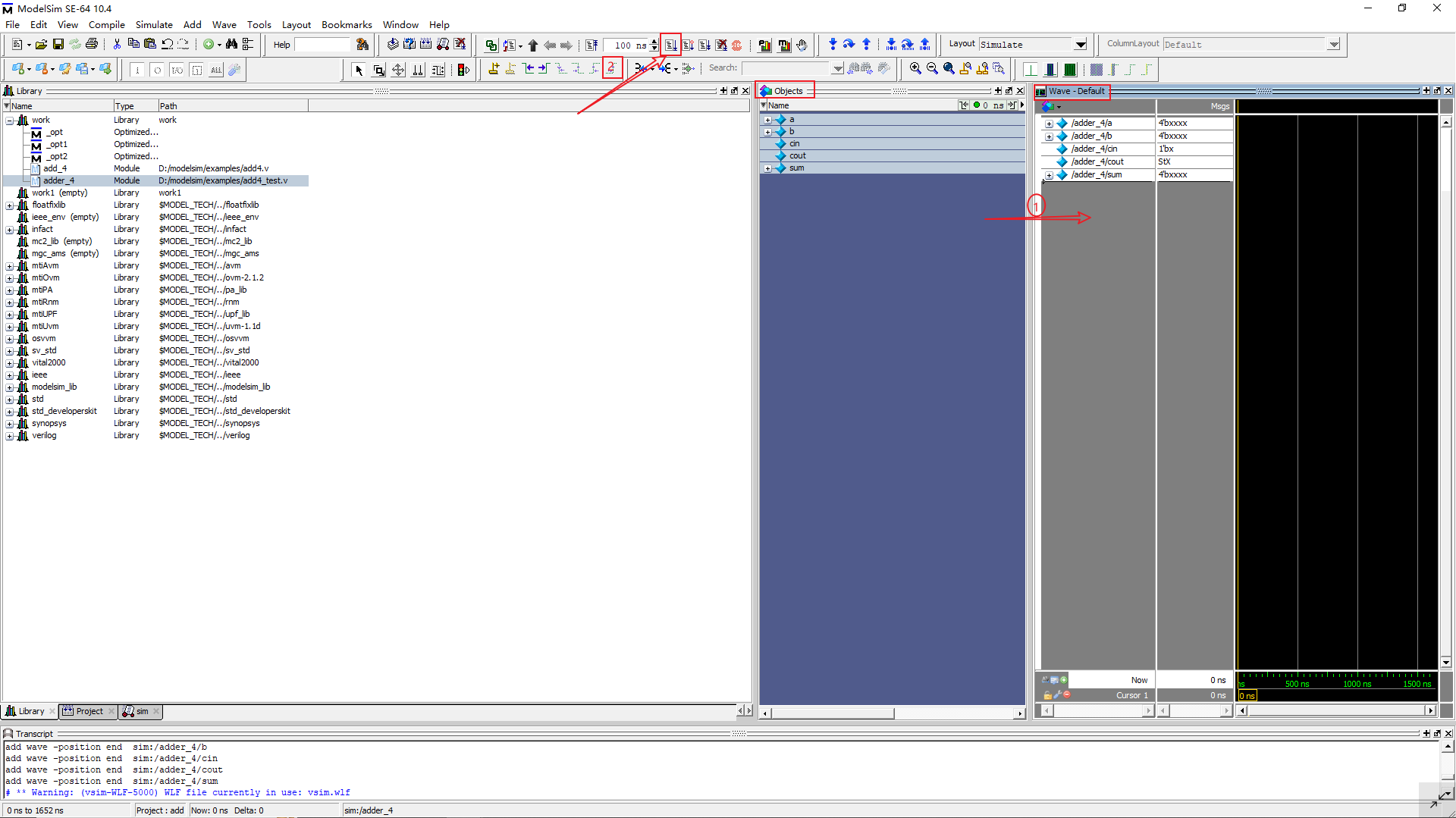

9、将objects下的项目全部选中,拖动到右边wave栏

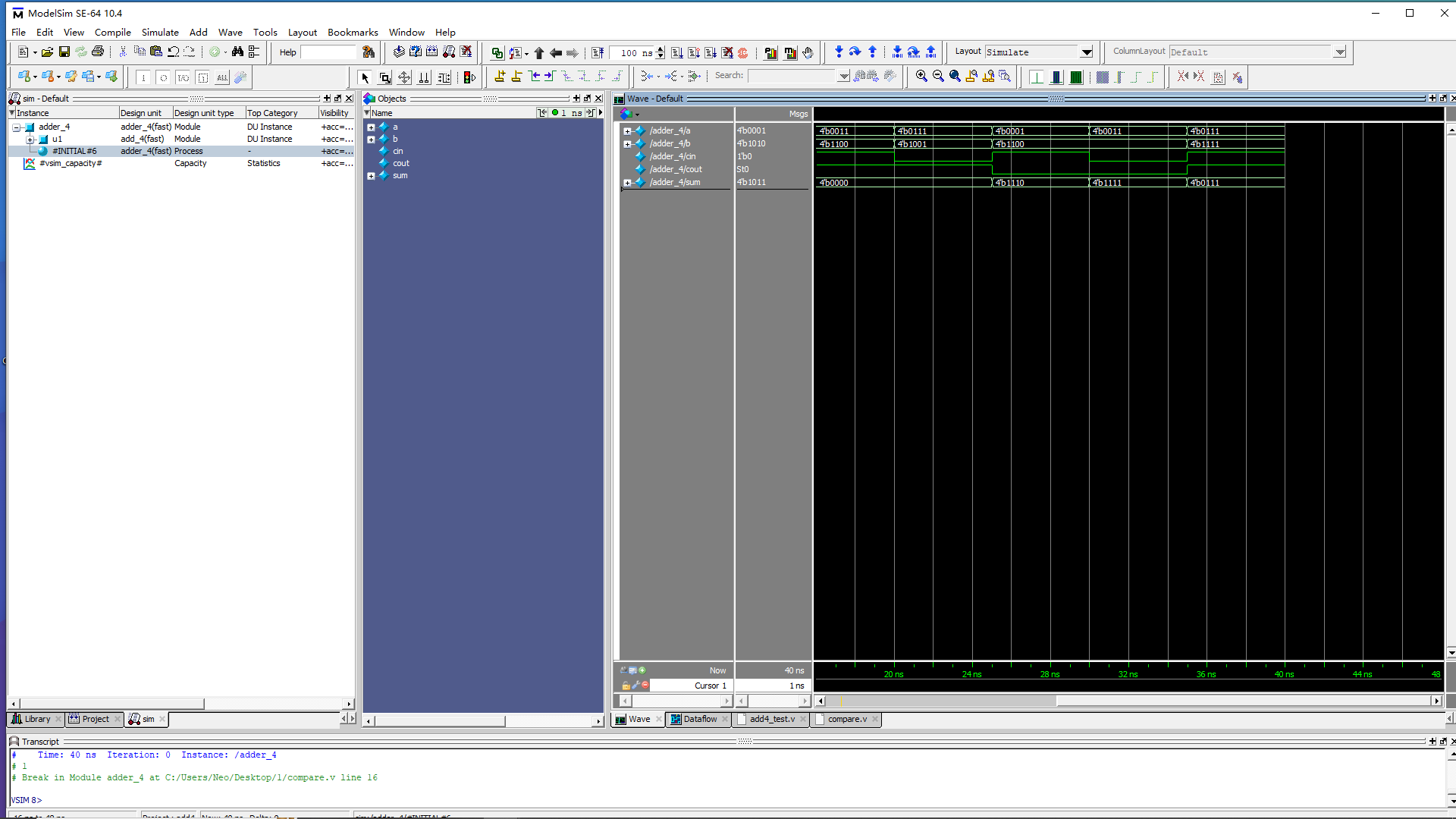

然后点击仿真

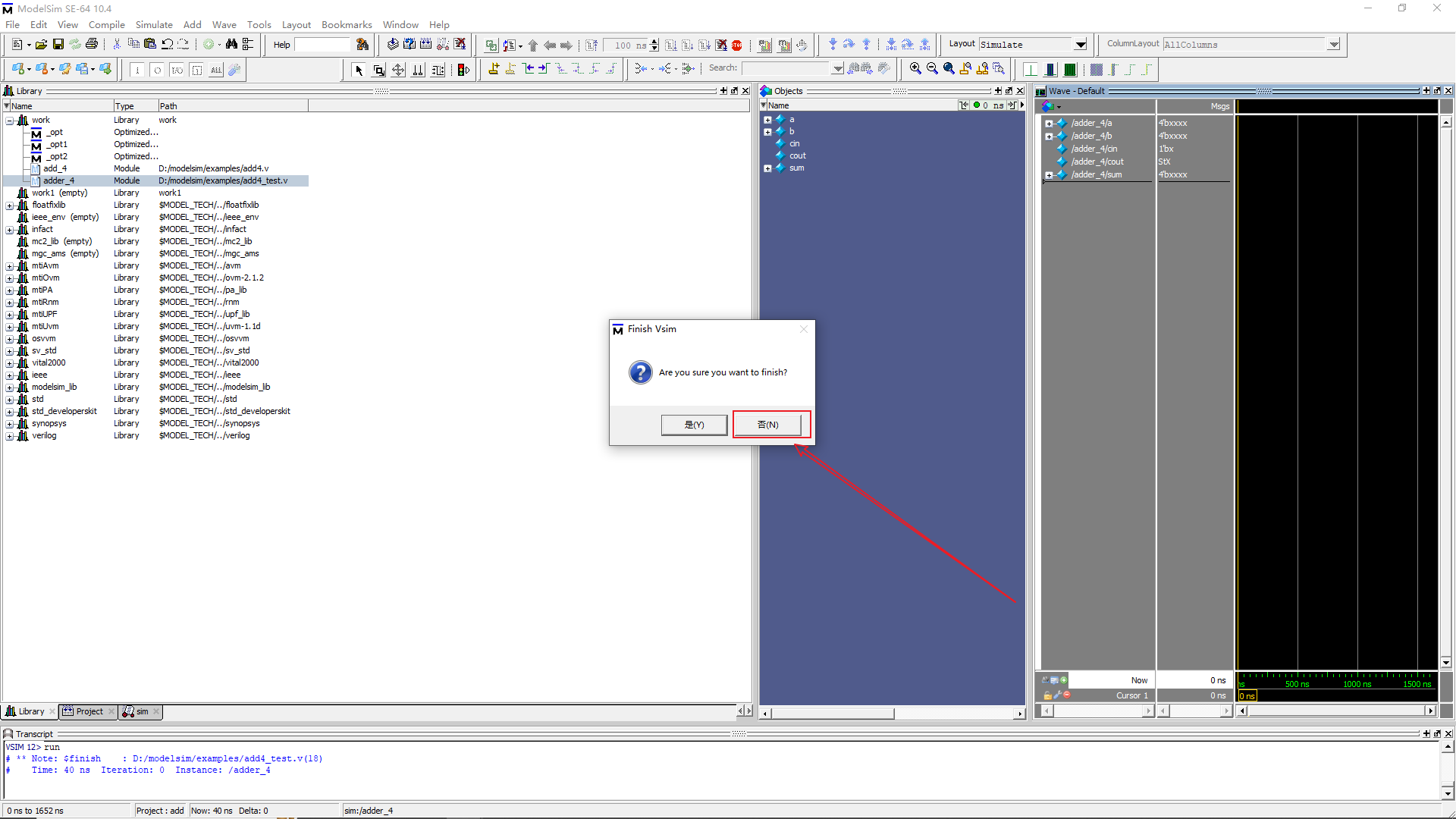

10、点击否

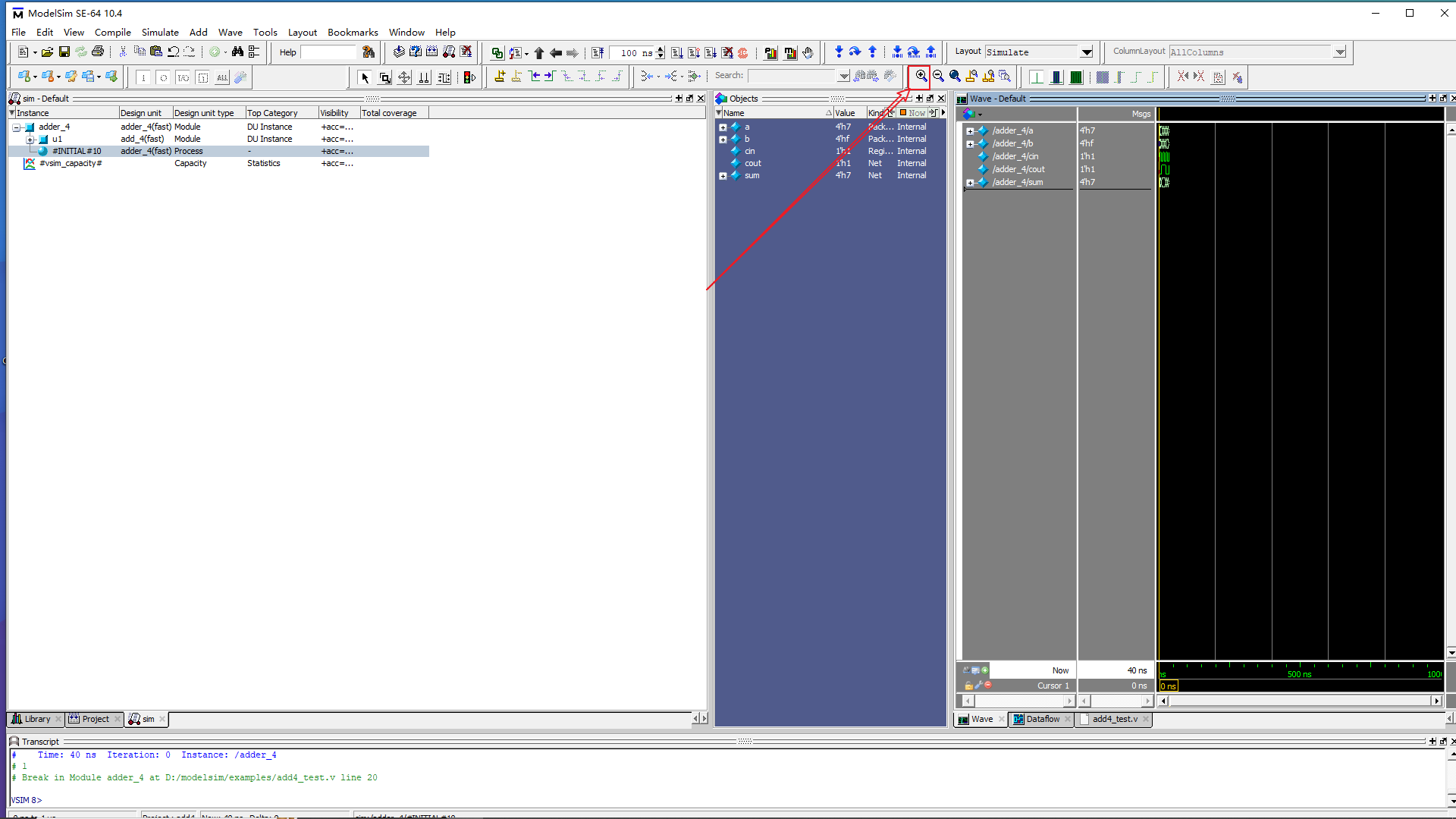

11、波形太小可以点击放大镜

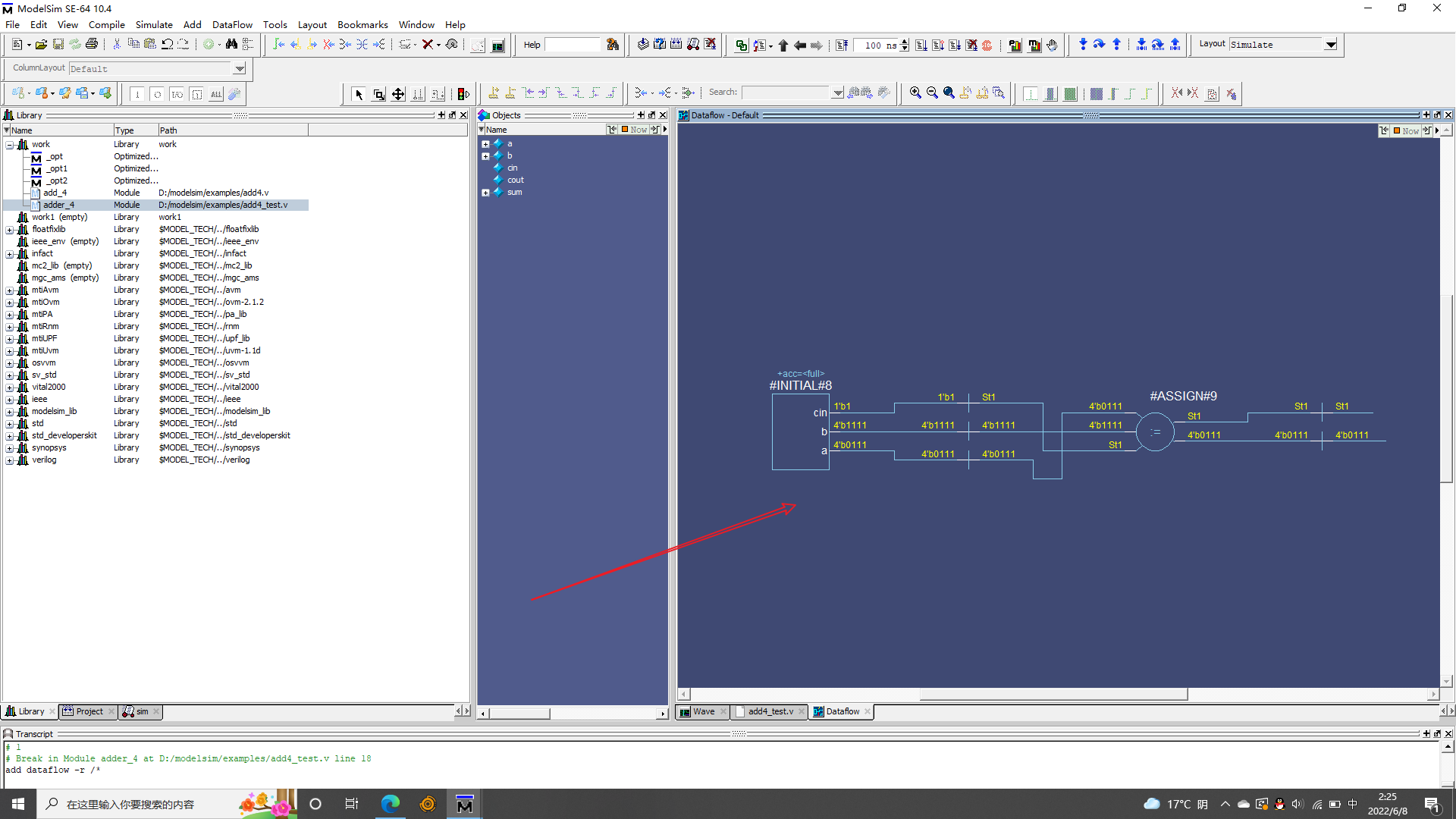

二、嗯,还有电路图

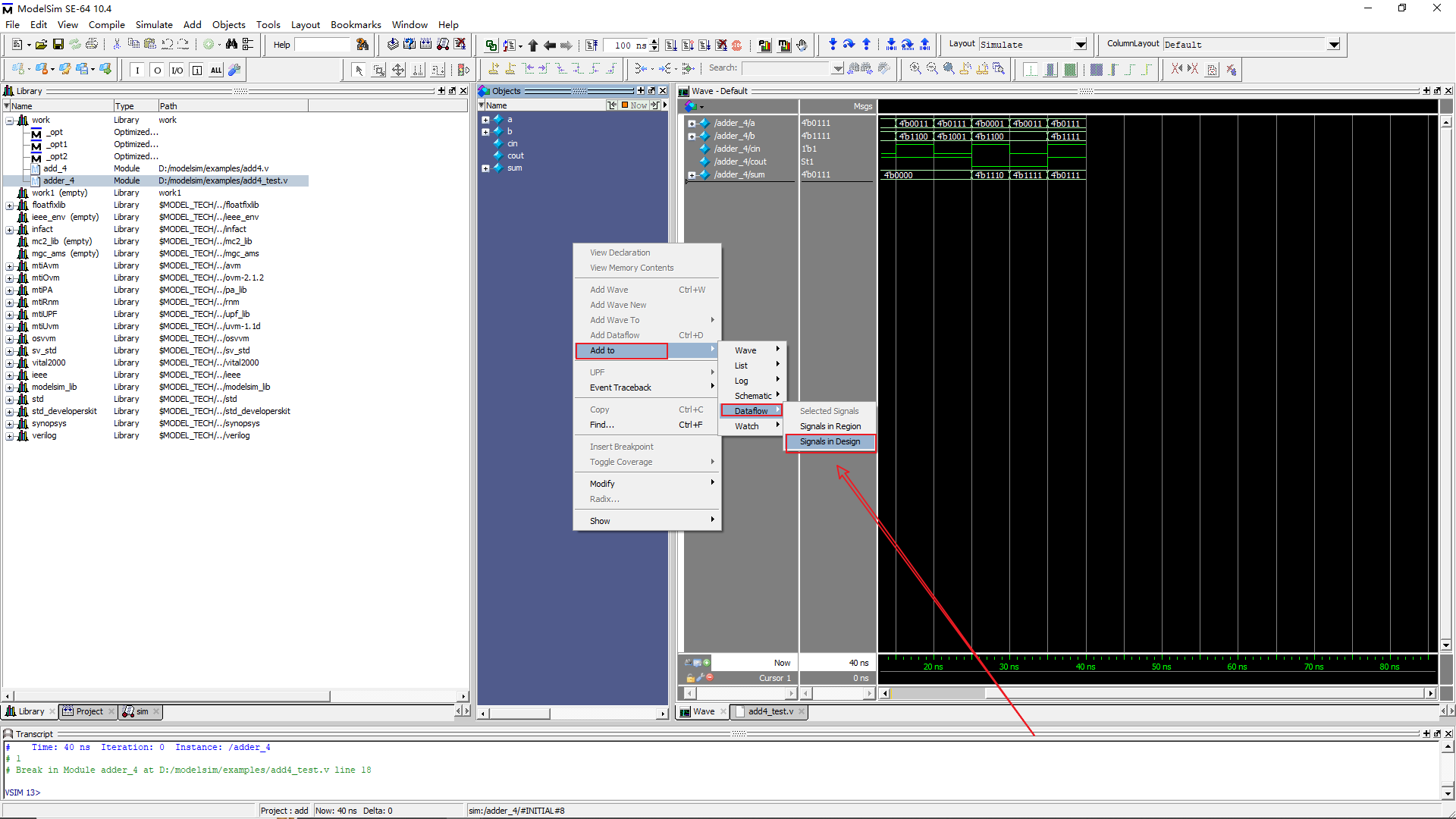

在objects下右键,依次找到Add to --> dataflow --> signals in design,如此便可以调出电路图

三、最后,大功告成

最后的最后,如果文章对你有帮助的话,还请点个赞,观众姥爷的支持将是我更新最大的动力

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/390918

推荐阅读

相关标签