热门标签

热门文章

- 1【Microsoft Azure 的1024种玩法】三十六.通过网络文件系统NFS协议快速将Blob 存储挂在Azure Virtual machines中_azure 宝塔 存储

- 2公司缺人面了8个测试员,他们都有一个相同的缺点....._测试工程师工作中如何找一个人缺点

- 3如何运用AR技术提升制造效率?这里有答案!

- 4【OpenVINO™】在 C# 中使用 OpenVINO™ 部署 Blazeface 模型快速实现人脸检测

- 5ROS主从机时间同步_ros时间同步

- 6一文5000字详解Python中PO模式的设计与实现_python -p -o

- 7Shiro和Security的核心模块以及两者的区别_daoauthenticationprovider整合cachemanage

- 8AI agent的核心有两个,执行和自我迭代

- 9鸿蒙教程来袭,苦熬一个月

- 10flask的session_flasksession加密

当前位置: article > 正文

山东大学计算机组成与设计实验一基本逻辑门逻辑实验_山东大学计组实验

作者:我家自动化 | 2024-05-19 01:23:02

赞

踩

山东大学计组实验

山东大学计算机组成与设计实验

山东大学计算机组成与设计实验报告

计算机组成原理实验报告

山东大学计算机组成原理实验报告

实验题目:基本逻辑门逻辑实验

实验目的:

1. 掌握TTL常用逻辑门输入与输出之间的逻辑关系。

2. 熟悉TTL中、小规模集成电路的外型、管脚和使用方法。

实验软件和硬件环境:

软件环境:

QuartusII软件

硬件环境:

1.实验室台式机

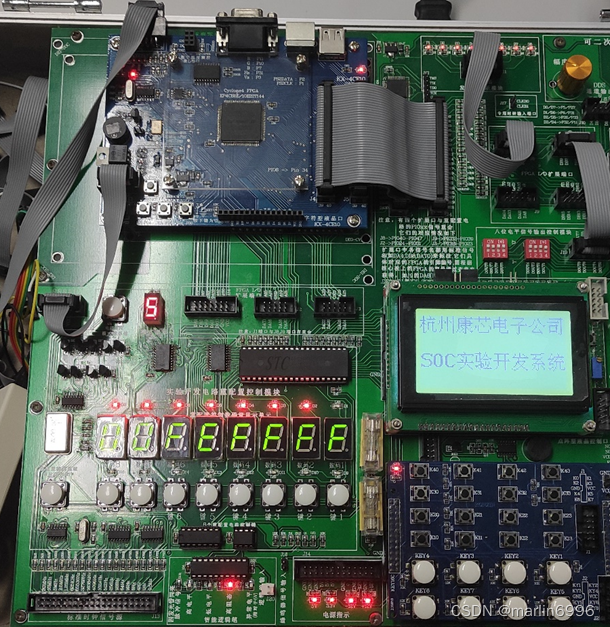

2.计算机组成与设计实验箱

实验原理和方法:

测试74LS86、tri、138、161、74LS194、74LS74集成电路模块,分析其输入和输出之间的逻辑关系。

实验步骤:

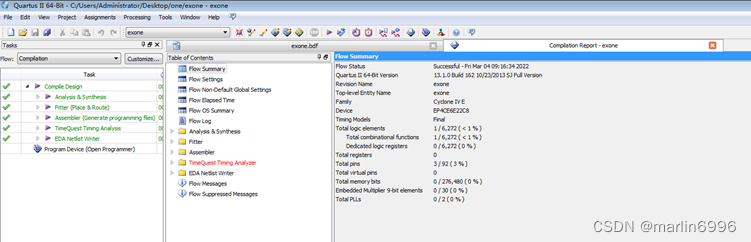

(1)在GuarttII环境下,建立工程文件,调入被测器件,将其输入管脚绑定在相应的开关上,输出管脚绑定在相应的指示灯上,创建源文件。

(2)将该文件编译下载到实验平台上的FPGA内,按照所测器件的功能表逐条验证。

(3)用试验台的电平开关输出作为被测器件的输入。拨动开关,改变器件的输入电平

(4)被测器件的输出引脚与实验台上的电平指示灯连接。指示灯亮表示输出电平为1,指示灯灭表示输出电平为。

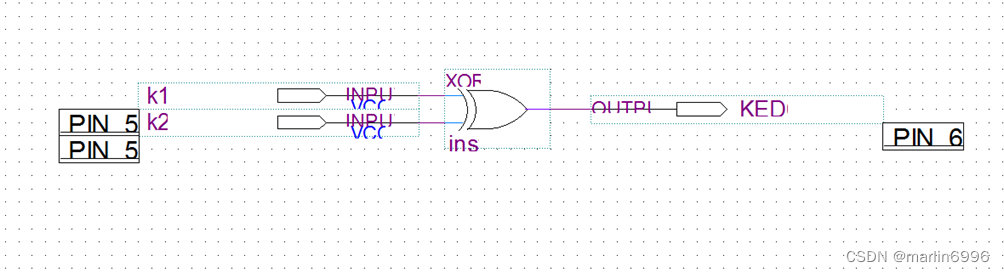

- 二输入四异或门 74LS86原理图:

画完实验原理图后给他设计了pin. K1,K2绑定在FPGA的PIN_52、PIN_55两个管脚上,LED0绑定在FPGA的PIN_60管脚上。

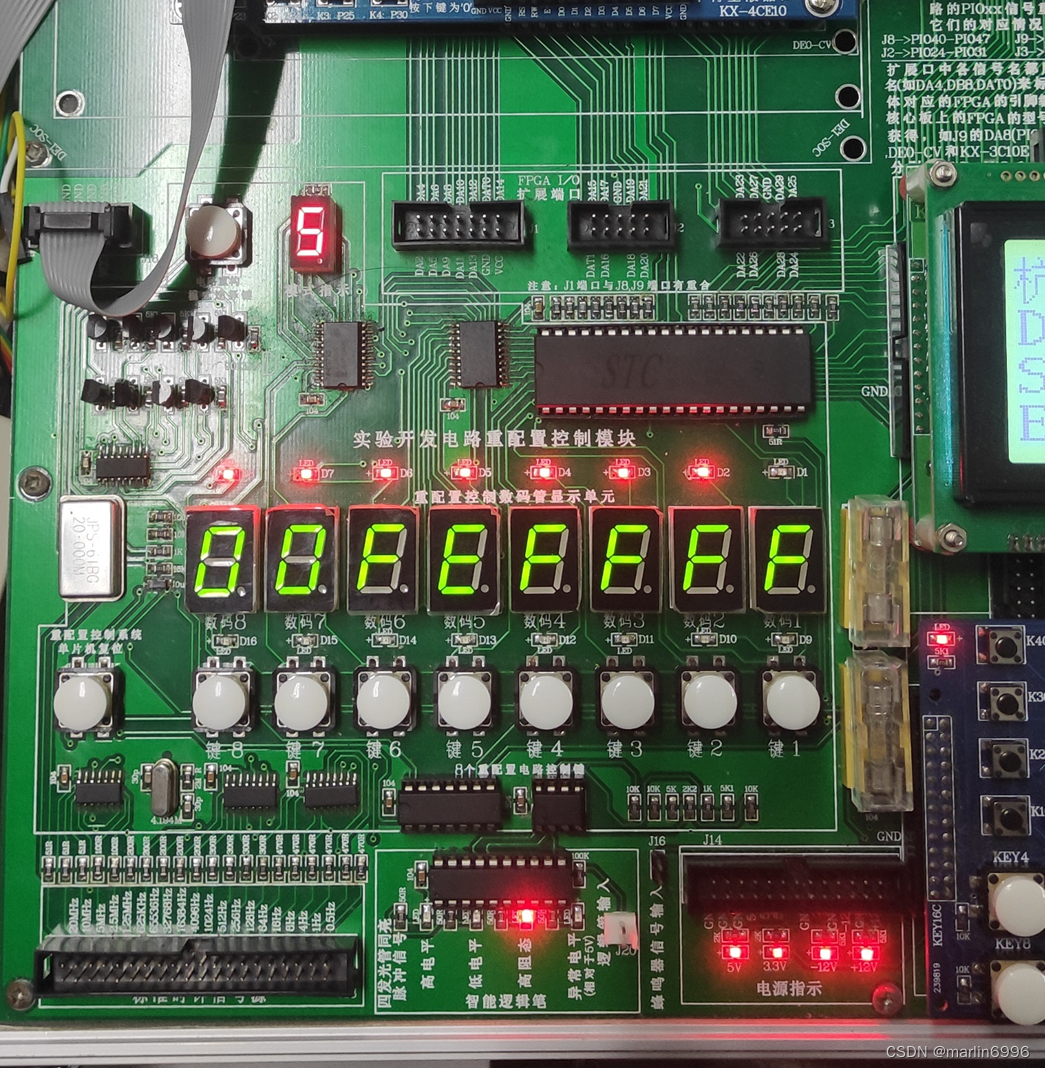

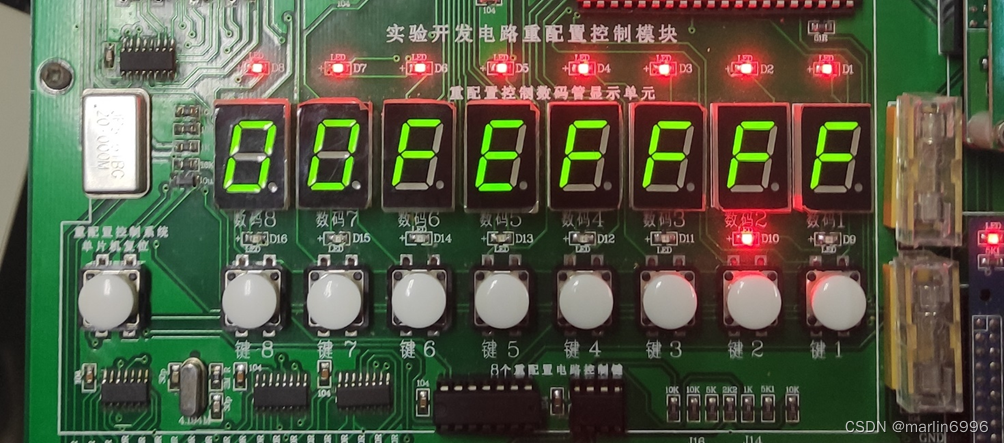

首先,模式指示跳到5。

然后我们用Key1 和 key2来输入高和低电平。

默认K1和k2 低电平时LED0不亮

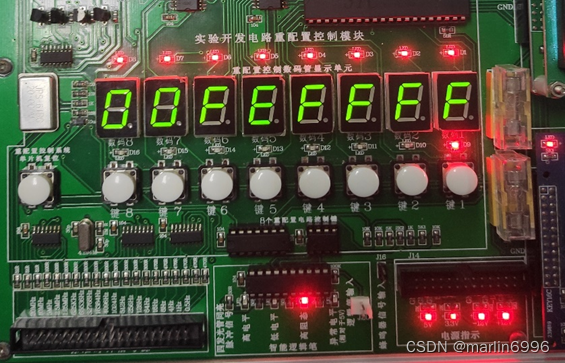

用K2给高电平的时候输出高电平。

用K1给高电平的时候输出高电平。

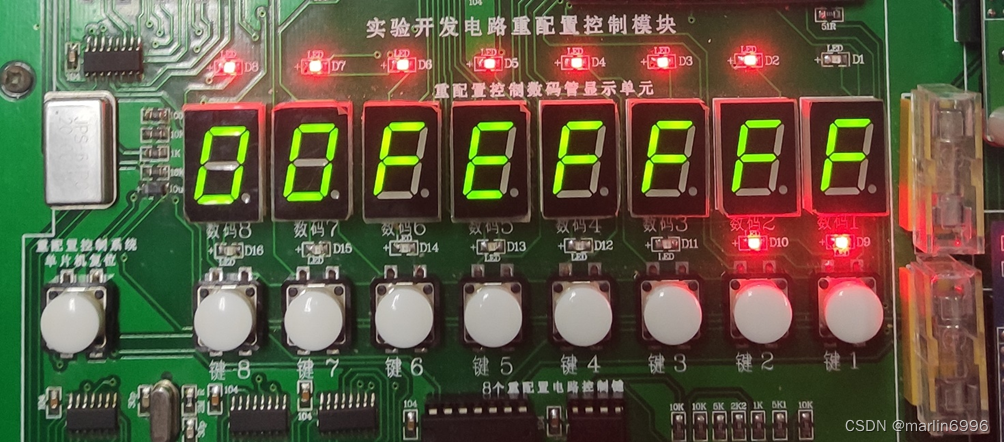

现在k1和k2高电平的时候输出低电平

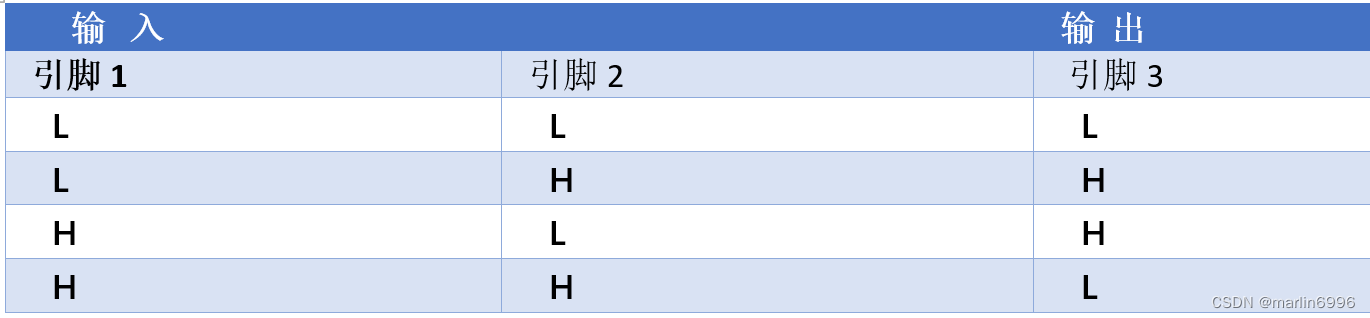

实验结果:

*L低电平输入,H高电平输入

二输入四异或门 74LS86 当信号不同时,高电平输出。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/590754

推荐阅读

相关标签