- 1用scipy的solve_ivp 求解复数常微分方程组_python在复数域内求解微分方程

- 2关于oracle 11g 循环多判断+continue 用法例子_oracle 多个判定多次执行

- 3Java中的推荐系统算法与实现

- 4lvs实现ftp负载均衡集群

- 5基于自然语言处理的深度学习综述(从word2vec,RNN,LSTM,Encoder-Decoder,Attention,BERT)_word2vec,rnn,lstm,gru等方法属于深度学习算法吗

- 6Java多线程的详细介绍_关于java中的多线程的说法

- 7JVM面试题详解系列——Java 对象的创建过程_java对象的创建过程

- 8打造智能Web抓取:ScrapeGraphAI - 一次抓取,无限可能!

- 9SQL分组统计,将两个字段或者属性相加进行分组_sql统计两个字段

- 10LangChain:大模型框架的深度解析与应用探索_langchange 大模型

timingPath/set_data_check和set_max_delay/set_multicycle_path_data check max delay

赞

踩

目录

1.2 set_data_check和set_max_delay区别和使用场景

0.timing path

timing path的概念:

start和end不只是reg的CP和REG的D pin

还可以是mem的D/Qpin和 port

port-->port 这种feedthrough也算timing path

1.set_data_check

set_data_check 通常用于信号间的skew 约束,比如一些高速接口相关信号间的约束。摘一段:

Data checks are normally applied where there is a specific requirement of skew (either minimum of maximum) or race condition (where the order of arrival of two signals can affect output and the intention is to get one of the probable outputs by constraining one signal to come before the other) between two or more signals. These may be required where:

At the digital-analog interface within a chip where analog signals at the analog block boundary are required in a specific order.

At the chip boundary, some asynchronous interface signals may have skew requirements.

set_data_check 和set_max_delay是有很大区别的,一个是保证多bit信号到达capture pin时间相差不多,另一个是保证所有bit的走线延迟在一定范围内。

换一种说法 一个是对skew约束;另外一个主要是约束delay。

可参考:

SDC | set_data_check-腾讯云开发者社区-腾讯云

静态时序分析——Data to data check_沧海一升的博客-CSDN博客

在异步电路后端实现流程(cdc signOff 后端做什么)_cy413026的博客-CSDN博客中说明了使用set_max_delay收cdc path,这里讨论一下set_data_check。

1.1set_data_check约束cdc path

对于grayCode的多bit同步,我们要求这个多bit信号到达dstClk的寄存器时间尽量相等,那么怎么用set_data_check来约束呢?比如dst_gray_code[3:0],我们做如下的约束:

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_1_/D -setup -0.3

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_2_/D -setup -0.3

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_3_/D -setup -0.3

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_1_/D -hold -0.4

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_2_/D -hold -0.4

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_3_/D -hold -0.4

或者做如下设置:

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_1_/D -setup -0.3

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_2_/D -setup -0.3

- set_data_check -from dst_gray_code_reg_0_/D -to dst_gray_code_reg_3_/D -setup -0.3

- set_data_check -from dst_gray_code_reg_1_/D -to dst_gray_code_reg_0_/D -setup -0.4

- set_data_check -from dst_gray_code_reg_2_/D -to dst_gray_code_reg_0_/D -setup -0.4

- set_data_check -from dst_gray_code_reg_3_/D -to dst_gray_code_reg_0_/D -setup -0.4

以上两种设置是等价的,区别在于第一种用了a2b的setup和hold约束,第二种用了a2b的setup和b2a的setup设置------为什么会出现这种情况请参考本人的另一篇文章

set_data_check专题[使用,report_timing,setup/hold检查]_cy413026的博客-CSDN博客

那么约束起效果后,结果就是dst_gray_code[3:1] 3bit信号到达寄存器D端的时间在dst_gray_code[0]到达D端时刻t的 [t-0.4: t+0.3](而不是[t-0.3: t+0.4])范围内,这样对于grayCode来说是否可以呢?

注意上面的setup,hold要设置为负数。至少有一个要设为负值 假如都是正值范围变为[t+0.4:t-0.3]左边界比右边界大就不可实现。如果把-0.4改为+0.2 范围就是[t+0.2:t+0.3],此时要求dst_gray_code[3:1]一定比dst_gray_code[0]晚了。

我们可以用公式来描述一下:

设t0时刻src_gray_code[0]发生变化,经过td之后到达dst_gray_code[0] pin D。t0+tf(tf为fastCLk的周期)时刻src_gray_code[1]发生变化,dst_clk在t0+x时刻第一次采样src_gray_code的变化

m为set_data_check的setup时间

n为set_data_check的hold时间

如果要满足此时两个bit都不满足dst_clk的setup,则需同时满足以下的条件

化简可得:

正常情况下

进一步需要满足下面两个条件

最终要求如下:

一般在一种工艺下

是不会发生的,

同理hold分析也可以完成

所以set_data_check也是可以保证grayCode的最多只有1bit在dst clk 采样时不稳定。

1.2 set_data_check和set_max_delay区别和使用场景

那为什么一般cdc check用maxDelay约束而不用set_data_check?

个人认为 maxDelay除了能保证grayCode同步的上述特性,还能对走线延迟绝对值进行约束。而set_data_check只能保证到达指定pin上的时间相差不大,但这个绝对时延无法保证。

set_data_check常见用于 I2C的scl和sda之间约束。也用于多bit使用打拍同步器的约束(在SNPS家的hdmi PHY sdc见过)。

实际上对于I2C/SPI/I2S/dpi这些接口,后端signOff的时候都会同时处理从数字寄存器到pad port上的maxDelay和信号线之间的skew。常有两种做法:

- 正向约束

可以正向用set_max_delay+set_date_check来约束,分别设定某类接口的maxDelay和信号之间【clk,多bit数据,控制信号等】的skew。

- 反向迭代

这种方法是后端先按照经验做timing,做完之后写脚本检查某类接口的所有信号是否满足maxDelay和信号间skew的要求,如果不满足,那就继续迭代。

2.set_mulicycle_path

可参考原创sdc中set_multicycle_path的解释_进击的芯片的博客-CSDN博客

或本人转载之后的地址:

sdc中set_multicycle_path的解释_cy413026的博客-CSDN博客

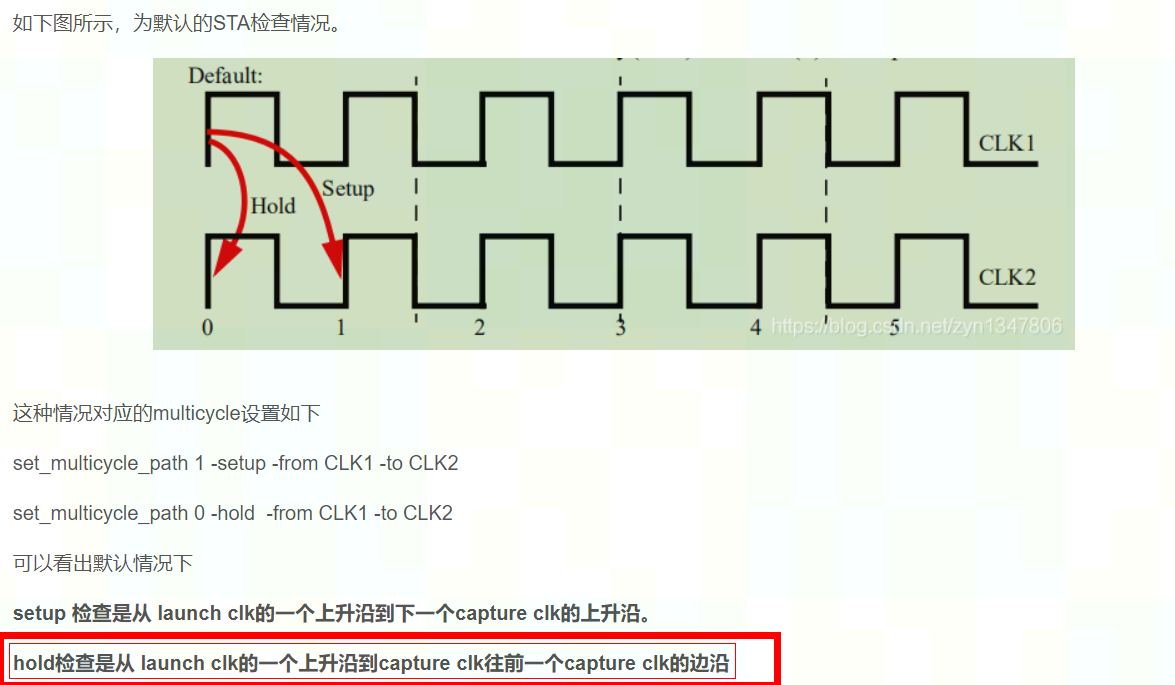

该篇文章详细介绍了setup/hold是的检查从launch/capture clk的哪个沿

快慢时钟间的setup/hold检查从launch/capture clk的哪个沿

multicycle path时setup/hold检查用的从launch/capture clk的哪个沿