- 1征战FPGA之使用IP核dds_compiler获取任意频率时钟和正余弦波形_dds compiler

- 2【MySQL】全面剖析索引失效、回表查询与索引下推

- 3DDS的理解及IP核的使用_dds ip核

- 4杂记——18.git merge使用介绍_提交完代码需要merge吗

- 5Kafka常用JMX监控指标整理【实战笔记】

- 6[随机数详解]生成一个随机数,生成指定范围的随机数及随机数组去重

- 7工作助手C#研究笔记(5)

- 8img2text图片识别商品接口API接口图片识别到文字接入演示

- 9流浪动物救助管理系统(开题报告+源码)_流浪宠物救助系统开题报告

- 10MySQL数据误删,恢复被删除的数据_my2sql下载

ATE测试—新手入门学习(一)【1-5】

赞

踩

目录

1、什么是ATE测试

ATE测试是指自动测试设备(Automatic Test Equipment)进行的测试,它在半导体产业中用于检测集成电路(IC)的功能完整性。ATE是集成电路生产制造的最后一道流程,目的是确保集成电路产品的品质。ATE测试包括对芯片的各种参数进行测试,如直流参数、交流参数、功能测试等,以评估芯片的性能、功能和可靠性4。

ATE测试的基本原理是通过测试向量对芯片施加激励,测量芯片的响应输出,并与预期结果进行比较,从而判断芯片是否符合规格要求。这个过程可以涉及到多种测试项目,包括但不限于:

- 直流参数测试:确定器件参数的稳态测试方法,如接触测试、漏电流测试、转换电平测试、输出电平测试、电源消耗测试等3。

- 交流参数测试:验证与时间相关的参数,如工作频率、输入信号输出信号随时间的变化关系等,常见的测量参数有上升和下降时间、传输延迟、建立和保持时间以及存储时间等3。

- 功能测试:模拟IC的实际工作状态,输入一系列有序或随机组合的测试图形,检测输出信号是否与预期图形数据相符,以此判别电路功能是否正常3。

ATE测试是确保IC产品良好率、提供有效的数据供工程分析使用的重要步骤,对于提高测试覆盖率和测试效率非常重要2。在ATE测试中,测试向量的生成是一个关键环节,它们可以由EDA工具的仿真向量经过优化和转换得到,以适应ATE的测试格式和要求。

ATE测试机是测试工程师在IC测试中必须使用的工具,它在计算机控制下,能自动进行各种信号测量、数据处理、传输,并以适当方式显示或输出测试结果。ATE测试对于芯片设计制造全流程参与的测试流程至关重要,尤其是在芯片后段电学特性测试中。

ATE测试的精确度和稳定性是工程师面临的两大难题,尤其在量产ATE测试时更为严重。为了解决这些问题,工程师需要对测试的基本参数进行深入分析,并采取相应的解决办法。

总的来说,ATE测试是半导体行业中对集成电路进行品质控制的一种重要手段,它通过自动化的方式提高了测试的效率和准确性。

eg:待测件:wafer(晶圆),封装后的芯片

测试设备:测试机,probe card(探针卡),load board

人:prober(探针台),handler(分选机)

ATE测试:使用机器设备 自动 完成对 批量IC 的测试。

2、为什么要做ATE测试

ATE测试一方面机器设备可以大幅提升测试速度,效率高。另一方面,机器能比人识别更加精密的芯片。由于ATE测试在确保产品质量、提高生产效率、降低成本以及提供设计反馈等方面发挥着重要作用,它成为了半导体行业中保证产品可靠性和竞争力的关键环节。

3、CP测试

(1)简要介绍

CP测试,英文全称Circuit Probing、Chip Probing,也称为晶圆测试或中测,测试对象是整片wafer的每一个Die,目的是确保整片wafer中的每一个Die都能满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证。同时也可以用来检测fab厂制造的工艺水平。

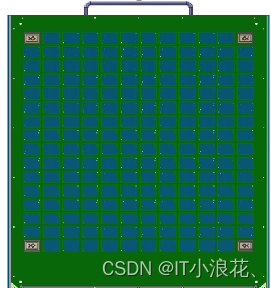

通过CP测试,可以筛选出不良的DIE,减少封装和测试的成本,同时优化生产流程,提高良品率在CP测试过程中,由于芯片的管脚全部裸露在外,需要使用探针台和探针卡等设备,通过探针将裸露的芯片管脚与测试机相连,进行测试。测试结果会用于监控工艺水平,区分芯片等级,以及控制成本。

-

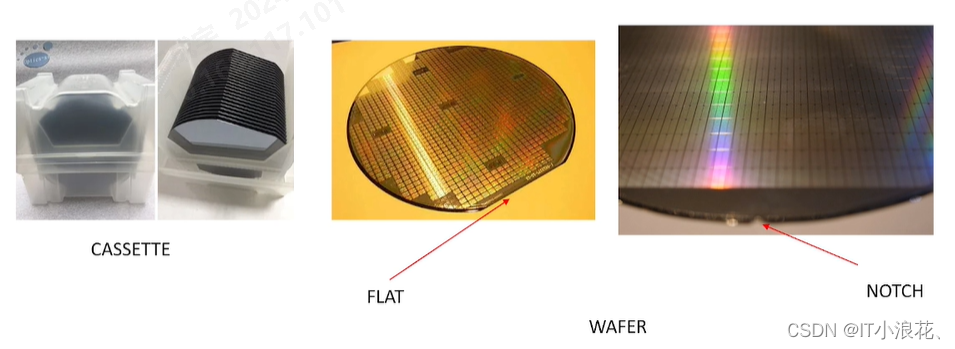

CASSETTE:这个词通常指的是一种盒子或者容器,用于存放和保护晶圆片。在半导体制造和测试过程中,晶圆片可能会被放置在特制的塑料或金属盒子中,以便于运输和存储。

-

FLAT:在晶圆制造中,"Flat"是指晶圆边缘的一个平坦部分,它用于晶圆在生产和测试过程中的定位。晶圆的Flat是识别和处理晶圆时的重要参考特征。

-

NOTCH:Notch是晶圆边缘的一个缺口,它同样用于晶圆的定位和识别。Notch和Flat通常是晶圆上用来确定晶圆方向的物理标记。

-

WAFER:Wafer是半导体制造中的基本材料,指的是硅片或其他材料制成的圆形薄片,用于制造集成电路(IC)。在晶圆上可以制造成千上万的微型电子元件,之后通过切割将它们分离成单独的芯片。

-

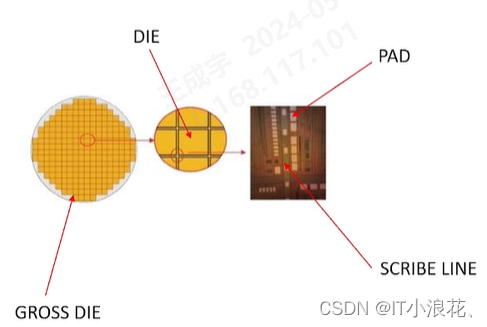

DIE:指的是晶圆上的单个芯片单元,在封装之前的状态。

-

LOT:批次的意思,通常用来标识同一批生产或测试的芯片。一个LOT可能包含多个芯片。

-

PAD:在半导体中,PAD指的是芯片上的一个小的金属区域,用于与外部电路连接。

-

LOTID:批次标识符,用来唯一标识一个特定的生产批次。

-

WAFERID:晶圆标识符,用来唯一标识一片特定的晶圆。

-

HOLDLOT:被扣留的批次,可能因为质量问题或其他原因,这个批次的芯片被保留或暂停进一步处理。

-

BIN:分BIN指的是对晶圆上的芯片进行分类的过程。通常,BIN1代表良品,其他BIN可能根据不同的失效项目或性能等级来定义。

-

SCRIBE LINE:在晶圆上,scribe line是用于指导切割机进行切割的线条,以将晶圆上的各个DIE分隔开。

-

GROSSDIE:通常指的是晶圆上所有未经过筛选的DIE的总数。

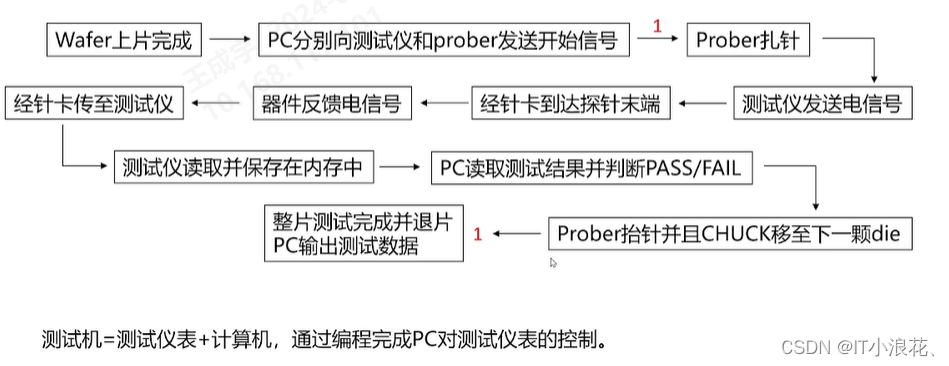

(2)CP测试流程

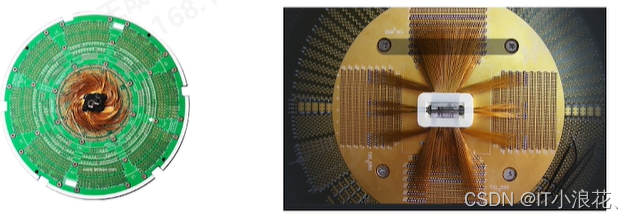

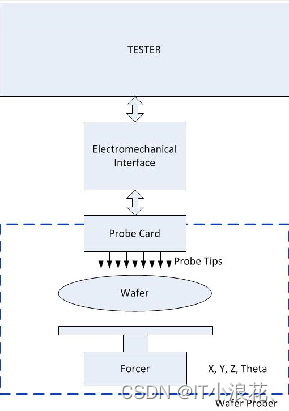

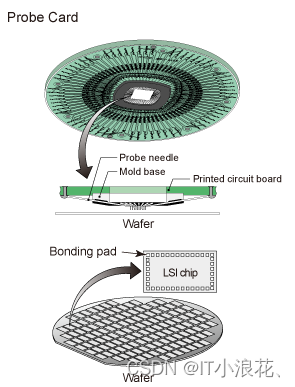

图片中的内容主要是了解Probecard(探针卡)的作用和组成,它在半导体制造过程中的晶圆测试(CP测试)阶段起着至关重要的作用。以下是对图片内容的详细解释:

-

Probecard(探针卡):是一种专门设计用来在晶圆测试阶段与晶圆上的芯片接触的工具。它的主要目的是确保测试信号能够准确无误地传递到芯片上,并且能够从芯片上准确读取响应信号。

-

控制卡(PCB):探针卡的一部分,通常是一块印刷电路板(PCB),它承载电路和电子元件,用于与测试仪器连接,传递测试信号。

-

探针:探针卡上的另一个关键部分,它们是细小的金属针,用于直接与晶圆上的PAD(接触垫)或BUMP(凸点)接触。PAD和BUMP是芯片上用于外部连接的金属区域。

-

晶片信号引出:通过探针与PAD或BUMP的接触,晶片上的电信号可以被引出,以便进行测试。

-

周边测试仪器与软件控制:探针卡与测试仪器和软件系统配合使用,自动化地测量和读取芯片的电信号。测试仪器负责生成测试信号,软件控制测试流程和数据分析。

-

自动化测量:整个测试过程是自动化的,可以高效地对晶圆上的大量芯片进行快速测试。

-

读取芯片电信号:测试的最终目的是读取芯片的电信号,以验证其功能和性能是否符合设计规范。

针卡主要有两个任务,第一,将测试仪的信号接入并将其传递到针尖端;第二,通过探针接触PAD,完成电信号的施加和读取。

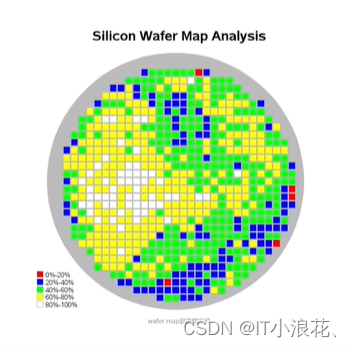

CP测试完成后,会生成两种重要的输出:测试数据(datalog)和晶圆图(Wafer Map,简称MAP)。以下是对这些术语的详细解释:

-

测试数据(datalog):这是一份详细的测试报告,通常以单个裸DIE(die)为单位进行统计。它包含以下信息:

- 位置信息:每个die在晶圆上的具体位置,通常以X和Y坐标表示。

- 测试项:对每个die进行的测试项目,可能包括电压、电流、时序、功能测试等。

- 测试结果:每个测试项的结果,通常用PASS(通过)或FAIL(失败)表示。FAIL品也称为REJECT。

- 分BIN信息:将测试结果的die按照性能或质量等级进行分类的信息。

-

晶圆图(Wafer Map,MAP):是一张图形化的表示,可以直观地展示整片晶圆的良率情况。它通常包含以下信息:

- 分BIN显示:在MAP上,测试合格的die通常按照不同的BIN进行分类显示。这些BIN可以基于性能、质量或其他测试标准。

- Hard Bin:指的是严格按照测试标准进行分类的BIN,通常与die是否能够正常工作直接相关。

- Soft Bin:相对于Hard Bin,Soft Bin可能包含一些性能稍逊或有轻微缺陷但仍然可用的die。Soft Bin的使用取决于具体的应用需求和成本考量。

- 封装依据:MAP提供了封装环节所需的重要信息,用于选择合格的die进行封装。这有助于优化封装过程,确保最终产品的质量和性能。

值得注意的是:"Soft Binning主要在CP测试阶段进行,侧重于根据电气参数测试结果对芯片的功能性进行分类;而Hard Binning则可能在CP测试阶段根据更严格的电气标准进行初步分类,并在封装后的最终测试阶段进一步根据物理特性和长期稳定性进行细分。"

不同的测试机制造商会根据自己的系统设计特定的数据格式。不过,为了确保数据的互操作性和标准化,半导体行业广泛采用了一些通用的文件格式,其中就包括:

-

STDF (Standard Test Data Format):这是一种被广泛接受的半导体测试数据格式,用于存储测试结果和相关信息。STDF文件包含了测试的summary信息,以及所有测试项的详细测试结果。它支持数据的统计分析,并且可以用于追踪和改进工艺流程。

-

CSV (Comma-Separated Values):这是一种简单的、以逗号分隔的文本文件格式,通常用于存储表格数据。CSV文件易于生成和读取,常用于数据分析和数据交换。

-

TXT:这是一种纯文本文件格式,它可以包含测试数据,但不包含任何格式化信息。TXT文件易于使用,兼容性好,但信息量和表达能力有限。

STDF作为一种结构化的文件格式,它不仅可以存储测试结果,还可以包含测试条件、测试限制、测试参数等多种信息。STDF文件由多个部分组成,包括:

- HEADER:文件的头部信息,描述了测试数据的基本信息。

- DATA:实际的测试数据,包括测试结果和相关的统计信息。

- FOOTER:文件的尾部信息,通常包含一些总结性的数据。

Python提供了多种库和工具来处理和分析数据。对于STDF文件的解析,Python社区提供了一些第三方库,例如stdflib,可以用来读取、处理和分析STDF文件。

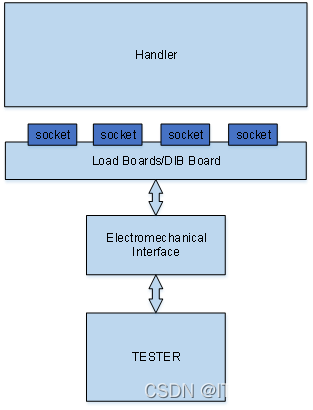

4、FT测试

FT测试,全称为Final Test(终测),是半导体制造过程中对封装后的芯片进行的测试。FT测试是确保芯片在最终封装形态下的功能和性能符合设计规范的重要步骤。

FT测试通常包括以下特点:

-

测试对象:封装好的芯片。与CP测试不同,FT测试是在芯片封装完成后进行的。

-

测试目的:作为芯片出厂前的最后一道拦截,确保每个芯片的功能和性能指标都能达到设计规范的要求。

-

测试内容:FT测试通常包括功能测试(检查芯片的基本功能是否正常)、电参数性能测试(如电压、电流、频率等是否符合规格)以及可能的其他性能测试。

-

测试设备:FT测试通常使用自动测试设备(ATE)和分选机(Handler)等设备。ATE负责生成测试信号并评估芯片的响应,而Handler则负责芯片的自动搬运和分选。

-

测试结果:测试结果将决定芯片的最终质量等级,包括良品和不良品的分类。根据测试结果,芯片可以被分选到不同的市场或应用。

-

重要性:FT测试对于保证产品质量和客户满意度至关重要。任何在封装后发现的功能缺陷或性能问题都可能导致高昂的返工成本或产品报废。

-

与CP测试的区别:CP测试是在晶圆阶段进行的,主要关注DIE的基本电性能参数,而FT测试则是在封装后进行的,更侧重于芯片的最终功能和性能。

FT测试是半导体制造流程中的一个关键环节,它有助于确保只有高质量的产品才能最终交付给客户。通过FT测试,制造商可以及时发现并剔除不合格产品,从而保护品牌声誉并减少经济损失。

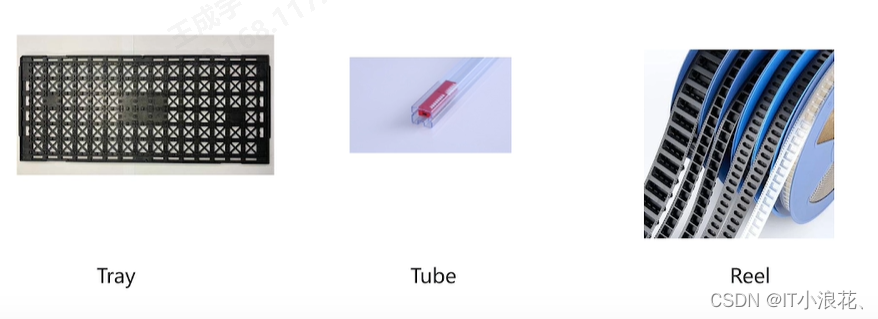

图片中列出的是一系列集成电路的封装类型,包括DIP-S、HP-、SOP-28、SSOP、SOT23、SOT89、SOT223、S0132L、LOO、OFP、BA、PLCC、CLCC等,以及半导体测试中使用的Handler(分选机)和Socket(测试座)。

-

Tray:托盘,通常指的是一种平面的、用于放置或运输芯片的容器。在半导体封装和测试后,芯片可能会被临时放置在托盘上,以便于后续的搬运和封装。

-

Tube:管状容器,用于装载芯片,特别是那些采用卷带包装(Tape and Reel)的芯片。芯片被放置在塑料或纸质的管内,方便自动贴装机进行拾取和贴装。

-

Reel:卷轴,通常与Tube一起使用,指的是装有芯片的卷带包装。在卷带包装中,芯片被放置在塑料卷带上,并通过自动贴装机进行自动化安装。

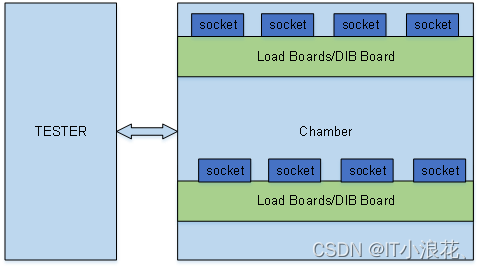

5、BI测试

Burn-in测试,又称老化测试,是一种用于检测半导体器件可靠性的测试方法。在这种测试中,芯片或系统在较高的电压和温度条件下运行一段时间,以加速暴露潜在的制造缺陷或早期失效。Burn-in测试的目的是筛选出那些在正常使用条件下可能早期失效的芯片,从而提高最终产品在实际应用中的可靠性和寿命。

以下是Burn-in测试的一些关键特点:

-

加速老化:通过在高于正常工作条件的电压和温度下运行芯片,Burn-in测试加速了芯片老化过程,使得任何可能导致故障的微小缺陷更快显现。

-

早期失效:测试旨在识别那些由于制造缺陷而可能在早期失效的芯片,这些芯片在正常使用条件下可能无法通过常规测试发现。

-

筛选过程:Burn-in测试是一种筛选手段,用于提高产品的整体质量和可靠性。

-

测试时间:Burn-in测试可能持续几个小时到几天不等,具体时间取决于芯片的类型和所需的可靠性水平。

-

测试环境:通常在特殊的高温测试室或烧录箱中进行,这些环境可以提供所需的高温条件。

-

自动监测:Burn-in测试过程中,芯片的性能和功能通常会被自动监测,以便于实时检测任何异常或失效。

Burn-in 测试 Burn-in test,对封装好的chip进行长时间的高低温‘烤机’测试,加速芯片失效 Burn-in将早期失效的chip挑出来,可以检验提升制造的良率。