- 1Excel计算两个日期之间天数及DATEDIF使用问题解决_datedif函数为什么输出1900

- 2第三章 动态规划-基于模型的RL-强化学习理论学习与代码实现(强化学习导论第二版)_基于rl模型带来的动态效益

- 32024年AI辅助研发:技术突破、行业应用与未来展望_ai各技术领域的最新技术

- 4第十届蓝桥杯大赛软件类决赛(Java 大学A组)_蓝桥杯2019国赛无方集合

- 5Maven的报错记录与解决方式_新导入的maven项目很多报错怎么解决

- 6Linux运维实例 shell脚本中数组的编写和应用 附双层for循环_linux需要用到两个for循环的编程

- 7特斯拉“纯视觉路线”能去掉ISP吗?_特斯拉摄像头raw图算法

- 8gradle 指定springcloud 版本_使用Gradle构建SpringBoot项目

- 9linux dhcp ipv6,Linux IPv6 Router: RADVD + DHCPv6

- 10高并发系统架构设计之数据库篇09:分库分表后数据库ID的全局唯一性_分库分表id全局唯一

数字逻辑第五章(同步时序逻辑电路)_数字电路激励函数

赞

踩

一、时序逻辑电路概述

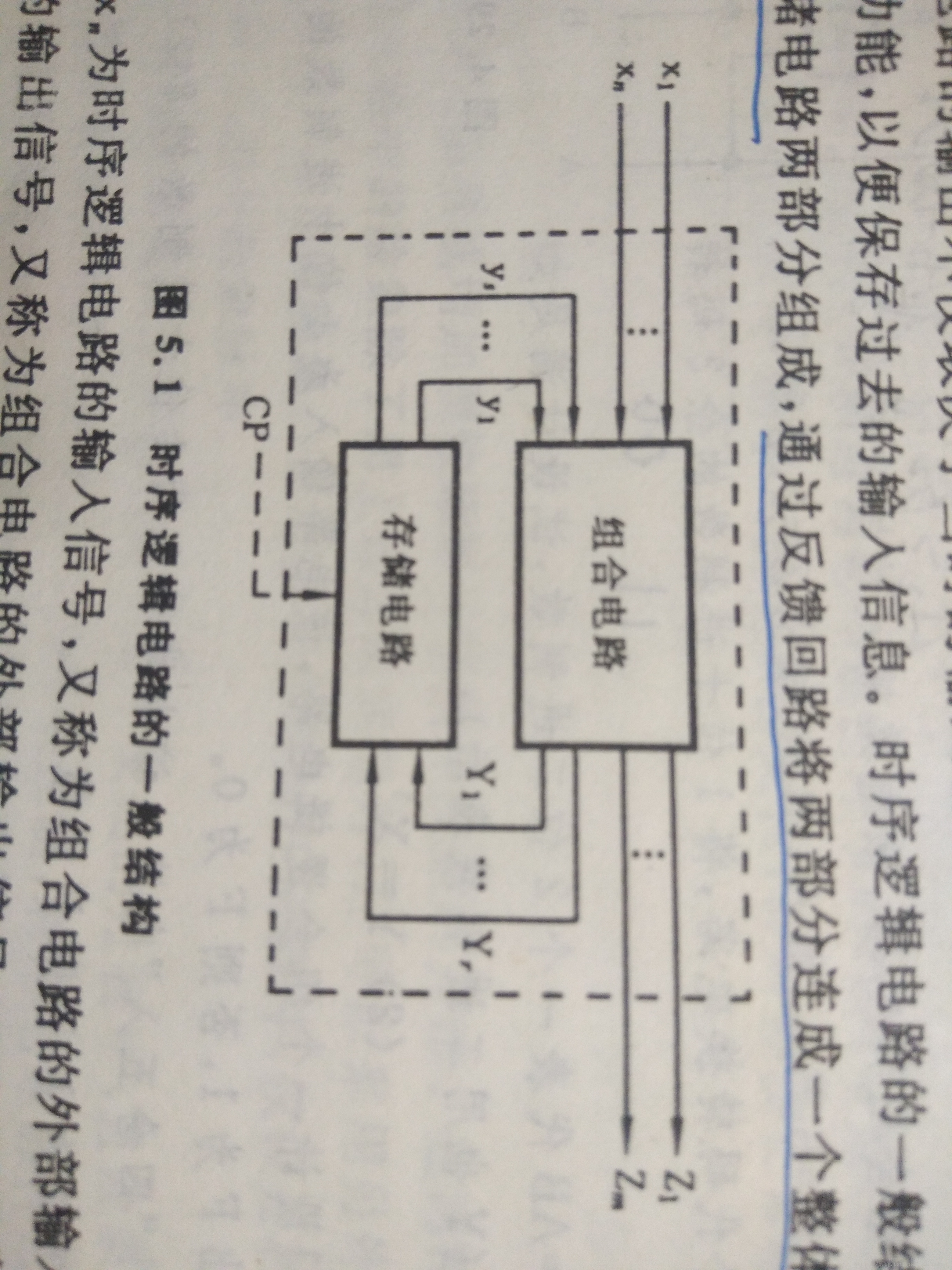

1.时序逻辑电路的结构:由组合电路和存储电路组成,通过反馈回路连成整体

有组合电路和逻辑电路组成,具有对过去输入的记忆功能;

包含反馈回路,通过反馈回路使电路功能与“时序”相关;

电路的输出由电路当时的输入和状态(对过去输入的记忆的结果)共同决定;

2.分类:

电路的工作方式:同步时序逻辑电路;异步时序逻辑电路

电路的输出/输入关系:

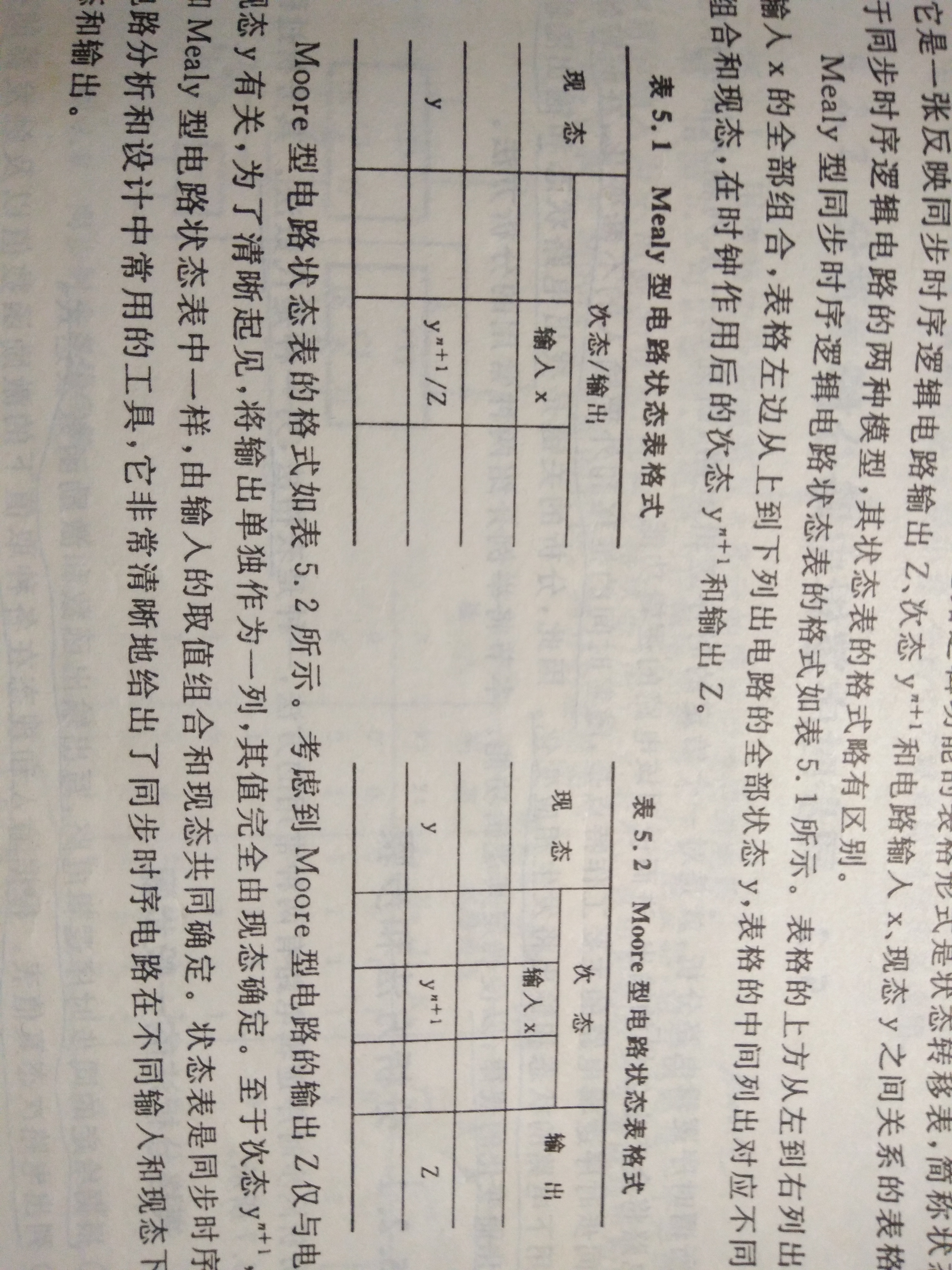

Mealy型时序逻辑电路:电路的输出是电路输入和电路状态的函数;

Moore型时序逻辑电路:电路的输出仅是电路状态的函数;

输入信号:脉冲型/电平型

3.同步时序逻辑电路描述方法:

逻辑函数表达式:输出函数表达式

激励函数表达式(存储电路的输出与电路输入及状态之间的关系)

次态函数表达式(电路的次态与激励函数及电路现态之间的关系)

状态表

状态图 Mealy型在有向线段上标注“/Z”;moore型在圆圈里标注“/Z”

时间图

二、同步时序逻辑电路分析

1.表格法:根据给定的同步时序逻辑电路,写出输出函数和激励函数表达式;

列出电路次态真值表,根据输入和现态在各种取值下的激励函数值及触发器的功能表,确定相应次态;

根据次态真值表和输出函数表达式,做出给定电路的状态表和状态图;

拟定一典型输入序列,画出时间图,并用文字描述电路的逻辑功能。

2.代数法:根据给定的同步时序逻辑电路,写出输出函数和激励函数表达式;

把激励函数表达式代入触发器的次态方程,导出电路的次态方程组;

根据次态方程组合输出函数表达式,做出给定电路的状态表和状态图;

拟定一典型输入序列,画出时间图,并用文字描述电路的逻辑功能。

三、同步逻辑电路的设计:

1.一般步骤:

形成原始状态图和原始状态表;

状态化简,求出最简状态表;

状态编码,的二进制状态表;

确定触发器数量和类型;

求出激励函数和输出函数表达式;

画出逻辑电路图。

2.完全确定同步时序逻辑电路:对所设立的每一个状态,在不同的输入取值下都有确定的次态和输出

不完全确定同步时序逻辑电路:对所设立的某些状态,在不同的输入取值下有随意的次态和输出

3.完全确定同步时序逻辑电路的设计:

形成原始状态图和原始状态表:确定电路模型,设立初始状态,根据需要记忆的信息增加新的状态,确定各时刻输出

状态化简:等效状态和等效类

状态编码;

确定激励函数和输出函数并画出逻辑电路图。