- 1Matplotlib中文乱码解决方案(1):`matplotlib.font_manager` 自定义字体_matplotlib.font_manager.fontmanager.ttflist

- 2【两周学会FPGA】从0到1学习紫光同创FPGA开发|盘古PGL22G开发板学习之数码管动态显示(五)_紫光fpga

- 3Chrome inspect工具使用_chrome 的inspect

- 4高频知识汇总 | 【操作系统】面试题汇总(万字长博通俗易懂)

- 5财务BS与PL关系

- 6程序员如何提高自己的逻辑思维能力?做未来在等待的人才!_程序员逻辑培养方法

- 7电脑远程桌面连接怎么操作?_远程桌面连接怎么设置

- 8TSINGSEE青犀推出河道/河湖/水域治理视频AI智能解决方案

- 9STM32 FLASH的擦写寿命_stm32flash擦写次数

- 10【C++】【TensorRT】检测时间不稳定原因汇总(持续更新)_不同设备的tensorrt不同

【数字IC/FPGA】书籍推荐(1)----《轻松成为设计高手--Verilog HDL实用精解》_轻松成为设计高手verilog

赞

踩

在下这几年关于数字电路、Verilog、FPGA和IC方面的书前前后后都读了不少,发现了不少好书,也在一些废话书上浪费过时间。接下来会写一系列文章,把一部分读过的书做个测评,根据个人标准按十分制满分来打分分享给大家。

书名:轻松成为设计高手–Verilog HDL实用精解

内容:Verilog语法、设计方法学

评价:8.5分。属于是比较推荐的Verilog语法入门书籍,同时也包括一些设计方法,比如状态机和数字电路建模的部分就写得很好。

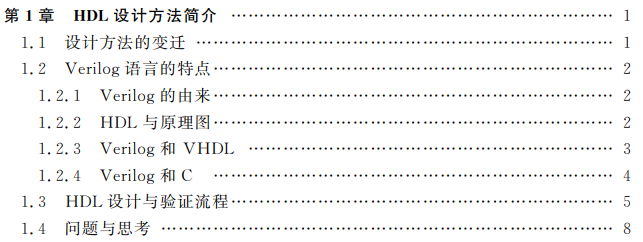

第1章:HDL设计方法简介

大部分书的第一章都没什么干货,基本就是在堆概念。老手用不上,新手看了也结合不到实际,不到三秒就忘了,属于比较鸡肋的一章。

第2章:Verilog语言基础

介绍了基本且实用的Verilog语法,定义的引出与解释都比较口语化,简单易懂,而且基本每个语法点都搭配了相应的示例,这一章学完基本上对日常设计开发常用的Verilog语法就都能掌握了。

第3章:描述方式和设计层次

介绍了用Verilog描述电路的三种层次结构:数据流描述、行为描述和结构化描述。可以让你对Verilog描述电路的思想和方法有个更好的了解,学会用“硬件思维”来设计电路,而不是用“软件思维”。

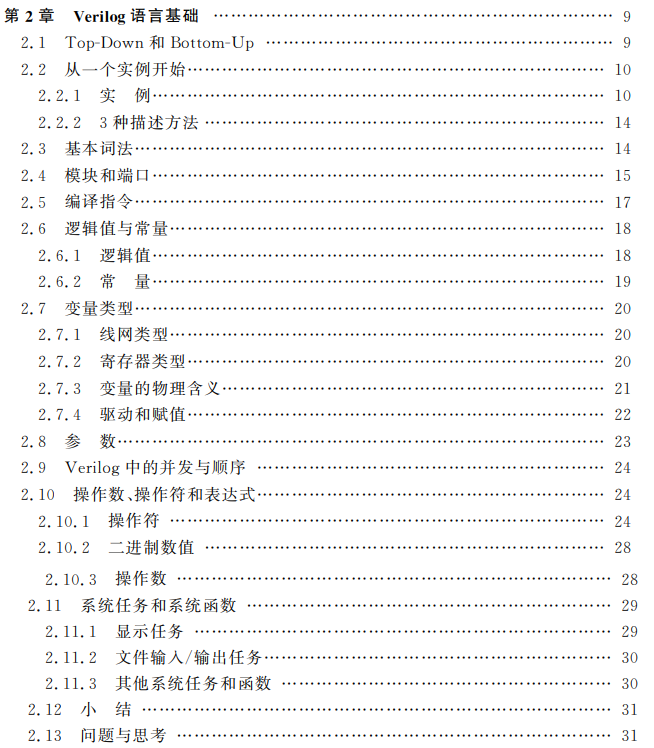

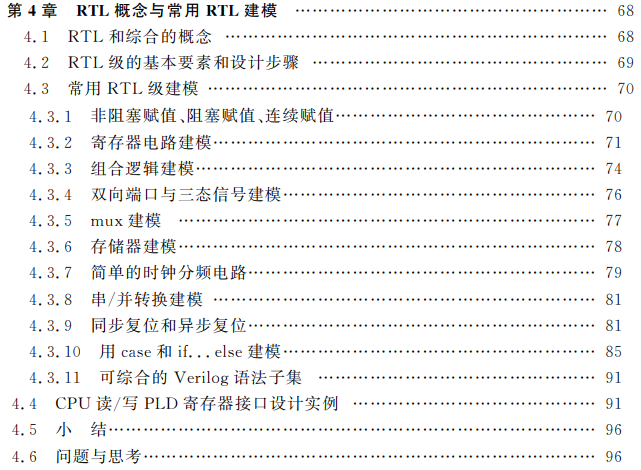

第4章:RTL概念与常用 RTL建模

这一章写得很不错,把Verilog语法和实际数字电路对应上了,可以帮助你建立从数字电路认知到Verilog认知的一个转变。比如组合电路和时序电路的Verilog实现和MUX、RAM等常用设计元素的Verilog实现都讲得挺细了。

这一章也讲了一些诸如复位设计、串并转换等后续学习一定会碰到的设计方法。

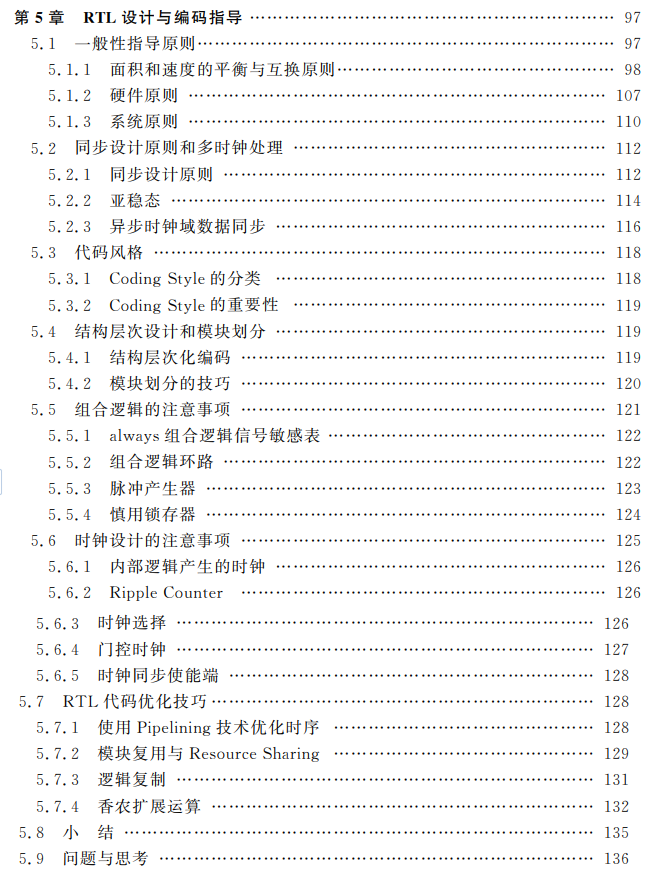

第5章:RTL设计与编码指导

这一章主要是讲的设计方法,比如面积与速度互换原则、代码风格等。

这部分的内容对于Verilog初学者可能暂时没用,可以先对这些方法有个基本的了解和概念即可,当你学了一段时间的FPGA设计后,就会发现这些内容都会对你很有帮助。所以先收藏起来,过段时间再来看看吧。

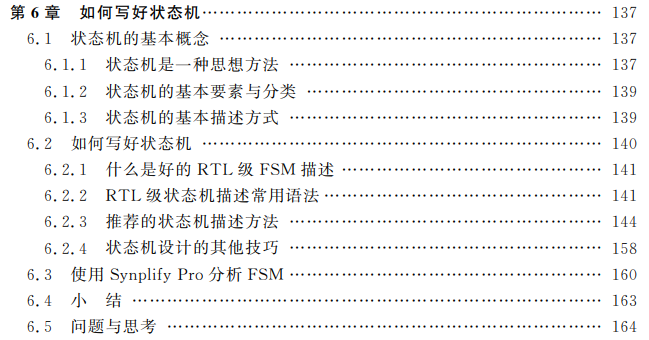

第6章:如何写好状态机

可能是全书写得最好的一章。状态机对FPGA设计有多重要怎么说都不为过,正所谓“万事皆可状态机”。这一章值得细读、反复读。

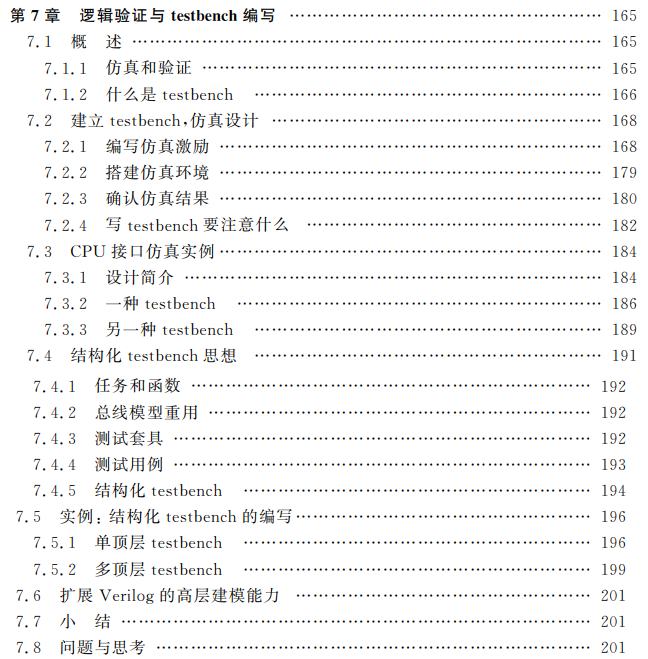

第7章:逻辑验证与testbench编写

这一章告诉你怎么写testbench。testbench用来测试你的设计正不正常,是非常重要的验证和测试手段。

很多初学者喜欢直接下板看运行情况,不喜欢写TB,这种设计习惯其实非常差。稍微复杂一点的设计,可能有一些隐藏很深的BUG在运行过程中是偶发性的、难复现的,这样出了问题你根本就没法查,但是只要你的TB设计得当,保证到一定的覆盖率,有很多BUG是可以在测试阶段就解决掉的。

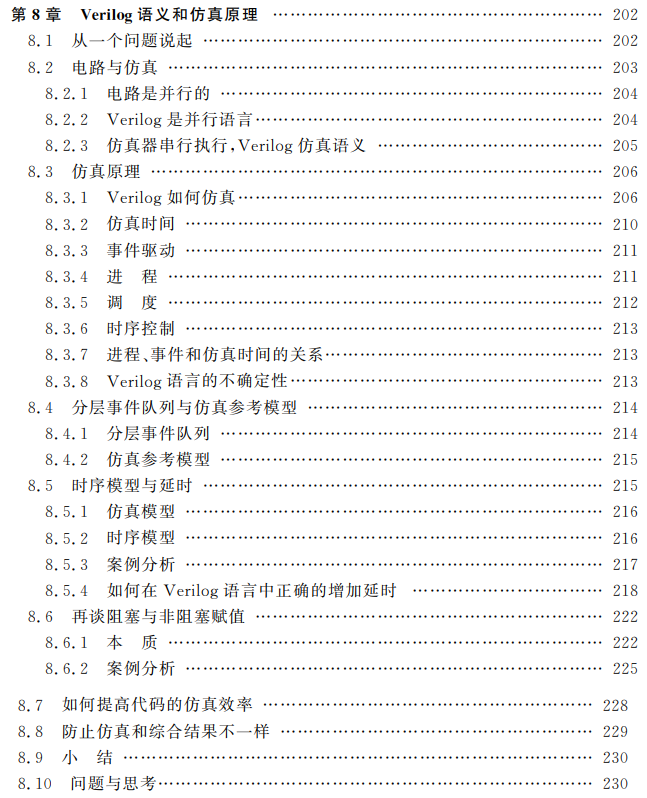

第8章:Verilog语义和仿真原理

这一章讲工具如何对设计电路仿真。因为工具是顺序执行的,而设计的电路是并行执行的,所以需要设计一套机制使其匹配。这部分的内容个人认为随便看看就行。

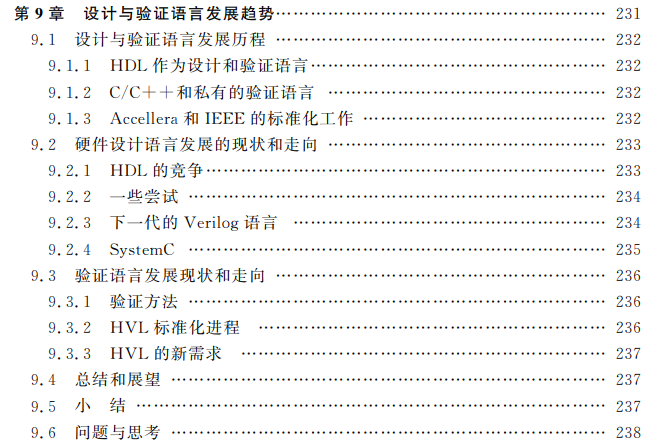

第9章:设计与验证语言发展趋势

和第一章差不多,花2分钟了解下就行。

总结

总的来说,这本书比较适合没有Verilog基础/Verilog基础比较差的同学,大部分的内容阅读起来是没有门槛的,少部分内容(比如设计方法)需要学习一段时间后后才能更好地理解。

- 声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/盐析白兔/article/detail/425143

Copyright © 2003-2013 www.wpsshop.cn 版权所有,并保留所有权利。