热门标签

热门文章

- 1Jenkins内网git无法访问服务器触发构建解决办法_jenkins构建项目时git 凭证加载不出

- 2神经网络与深度学习第6章:循环神经网络 阅读提问_除了堆叠循环神经网络外,还有什么结构可以增加循环神经网络深度?

- 3时空序列预测|| DSTAGNN:用于交通流量预测的动态时空感知图神经网络GNN

- 4申请 meta llama 模型权重(超详细)

- 5el-input限制只能输入数字,且保留2位小数_el-input只能输入数字和最多两位小数

- 6PyOpenGL代码实战(四):着色器_python opengl 编写shader

- 7鹅优化算法(GOOSE)-2024年新SCI算法-公式原理详解与性能测评 Matlab代码免费获取

- 8情感分析(文本分类)数据集汇总_情感分析数据格式有哪些

- 9Jenkins android 自动打包安卓 centos8.5 运维系列五

- 10代码随想录:二分查找和双指针

当前位置: article > 正文

紫光同创PGL22G输出时钟不稳定_紫光的fpga的pll输出有问题

作者:盐析白兔 | 2024-05-05 13:45:12

赞

踩

紫光的fpga的pll输出有问题

**

紫光同创PGL22G输出CLK不稳定

**

使用黑金PGL22G开发板+Pango Design Suite 2021.2输出CLK波形不稳定

基于黑金SD卡读取BMP图片显示例程把分辨率改成2340*1080后对应的PLL IP内频率改为165M

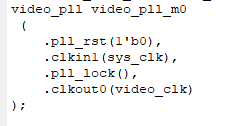

顶层文件配置如下

重新编译下载后,使用逻辑分析仪抓取CLK波形如下

可以发现CLK波形不均匀,逻辑分析仪的采样率等设置无问题,正常出来应该如下

之后把顶层模块中PLL IP调用改为下图后

输出的波形更不稳定了中间的误差到了600NS以上了

最后询问FAE后需要把IO的驱动能力拉高,在软件Tools->User Constraint Editor->Device页面左侧的IO界面中找到CLK输出的脚位的DRIVE属性拉高

之后波形输出就正常了,如果不行可以尝试我前面修改的顶层文件中调用PLL的写法再调高驱动能力,我是直接在例程基础上面把驱动能力调高了,没有修改PLL调用

另外请注意黑金开发板是5V的电源,不是12V的不要接错,避免烧板子

有什么说的不对的地方请各位大佬多多指教!

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/盐析白兔/article/detail/539133

推荐阅读

相关标签