热门标签

热门文章

- 1[OpenCV / The Laplacian pyramid] 浅析拉普拉斯金字塔 / 利用拉普拉斯完成采样的恢复 学习笔记

- 2【2024】当ChatGPT拥有了身体,并且与人类并且全面对话并学习,你还感觉AI与你很远吗?

- 3房地产大数据分析方法_基于大数据的商品房销售数据采集的设计和实现

- 4elasticsearch之DSL查询文档_elasticsearch 查询 dsl 文档

- 5ChatGPT的诞生和发展_chatgpt的产生与发展

- 6hadoop hbase hive spark对应版本_hadoop3.3 spark3.5

- 7(LdAiChat、Ai Loading、不墨AI助手、360AI搜索、TIG AI)分析好用的ChatGPT

- 8C++知识总结

- 9nlp(贪心学院)——实体消歧、实体统一、指代消解、句法分析

- 10PaddleHub中的模型_hub.module

当前位置: article > 正文

基于 DSP+FPGA+1553B总线的水下信息融合系统的设计_fpga接dsp的xintf

作者:我家小花儿 | 2024-05-03 07:32:25

赞

踩

fpga接dsp的xintf

在一个大型水下系统中,针对不同分系统的特

性,通常采用不同的通信协议。串行通信具有抗干扰

能力强,传输距离远等特点,适用于需要远距离通信

的分系统;

MIL-STD-1553B

总线在传输方面具有极强

的可靠性和实时性,适用于对信号准确性和实时性要

求高的惯导及发控分系统

[

1

]

。

DSP

可以快速处理数据且具有较高的集成性和稳

定性,目前已成为控制领域主流的处理芯片

[

2

]

。但

DSP

的片内通信资源有限且固定,会导致系统的可扩

展性不强,且若

DSP 频繁响应中断,也会对其工作的

效率产生影响。

FPGA

与

DSP

相比具有以下优点:支持并行操

作,可以同时处理多个工作单元,可以实现数据的实时

传输

[

3

]

;

FPGA

可以通过自身编程实现传统设计中逻辑

接口,从而使得外围电路设计的难度大大减小,减少

硬件设计难度,且系统的可扩展性得到极大的提高。

本文以

DSP

芯片作为主处理器,负责应用层的设

计以及整个系统运行时信息的调度,采用

FPGA

作为

系统的协处理器,完成对多路

RS-422

串口信号的采集

以及对数据的缓存,同时使用

FPGA

实现

BU61580

的功能并根据项目需要对功能进行扩展,完成

1553B

总线接口模块的设计。

1

系统总体设计

主要实现

16

路串口数据的发送及接收,以及

2

路

1553B

数据的发送及接收 , 后期根据需要可扩 展

CAN

通信及

429

通信等。在进行设计时,要充分考虑

如何实现不同控制芯片之间准确、高速、实时的通信

问题。

DSP

选择

TI

公司的处理器芯片

TMS320F28335

,

该芯片低成本,高性能,运算能力强、精度高。但该

芯片的串口资源只有

3

个,不满足设计要求,且若采

用

DSP+BU-61 580

的结构实现在

BC

模式下的

1553B

通

信,根据设计要求,系统需要发送大量周期为

5ms

和

10ms

的周期信号,若周期信号的发送由

DSP

控制,

则

DSP

需要频繁响应计时中断,会影响芯片的数据处

理速度,且可能造成数据丢失等现象。

为了解决这些问题,选用低功耗型

XC7K325T

[

4

]

芯

片完成对

DSP

功能的扩展。

DSP

与

FPGA

之间通过

XINTF

总线进行数据交互,从而实现

DSP

对外围芯片

的控制 , 使 得

D S P

的功能得到最优的发挥

[

5

]

,

XINTF

总线包括数据线、地址线及片选线等。

RS422

总线接口设计,以

FPGA

芯片为核心进行搭

建。接口驱动芯片均选用

ADM2682E

,该芯片内有隔离,

无需外部隔离处理。通过

FPGA

实现总线控制器(

BC

)

的功能。使用

HI-1 573

将

1553B

总线信号转化为

FPGA

可以处理的

3.3V

差分信号。

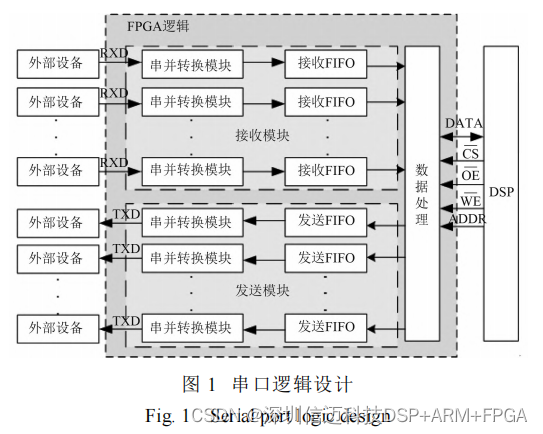

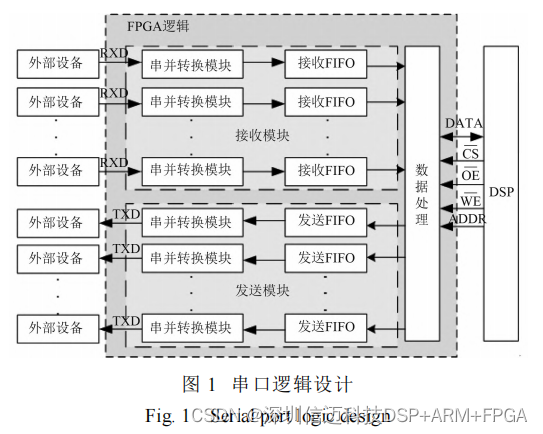

2 FPGA

逻辑设计

2.1

多路串口逻辑设计

RS422

通信电路采用模块化设计。

FPGA

的功能逻

辑如

图

1

所示,从功能上划分为接收模块、发送模块

以及数据处理模块。考虑到不同的外部设备对串口通

信的要求各不相同,为了提高模块的普遍性,每一路

串口通道都具有独立性,可以通过

DSP

对每一路串口

的属性进行分别的设置,也即每一路串口的波特率,

数据位,奇偶校验位,停止位等均可以通过编程进行设置。

1

)收发

FIFO

缓存数据

FIFO

一般用于处理高速异步的数据交互和数据缓

存。收发

FIFO

采用

8×256

的容量,数据位宽度为

8

位,存储

深度为

256byte

。

FIFO_empty

作为

FIFO

是否有数据的

标志信号。

2

)串并转换

FPGA

通过状态机完成将串行数据转换为并行数据的功

能。系统上电复位后状态机进入

Idle

状态,当收到数

据时,状态机进入

Start

状态;检测到串行数据的起始

位后状态机进入

Receive

状态否则退回

Idle

状态;

Re

ceive

状态主要进行数据位的接收,不同通道可以接收

不同位数的数据位,当循环接收数据位个数满足通道

要求后,进入下一个状态

[

6

]

;若串口协议中有校验位,

则进入

Parity

状态,判断奇偶校验,否则状态机进入

Stop bit

状态。

Stop

状态可以进行停止位的接收,当接

收的停止位符合要求后,状态机将已转换为并行的数

据存入接收

FIFO

中,并重回

Idle

状态。

系统上电进行复位后状态机进入

Idle

状态,当发

送

FIFO

的

fifo_empty=’0’

时,状态机进入

Start

状态,

否则仍然处于

Idle

状态;完成起始位的发送后,状态

机进入

Sample

状态,读取

FIFO

中的数据并进行采

样,将数据转换为高低电平后,状态机进入

Transmit

状态,发送串行数据,并发送停止位;发送完成后进

入

Stop

状态完成整个发送流程。

3

)数据处理及与

DSP

的通信

FPGA

为每一路通道分配不同的片选地址,

DSP

在

对通道进行初始化及收发数据时,要根据片选地址找

到对应的寄存器并通过总线收发不同地址中的数据,

从而进行相应的数据处理。根据系统流程,当需要获

取某一路串口的数据时,

DSP

读取该通道对应的

fifo

empty

状态,若不为空,则

DSP

从该通道存放数据的

寄存器地址中,获取已经过串并转换的数据。反之,

若需要发送指令至某一通道时,

DSP

通过总线将打包

好的带帧头帧尾的数据发送至相应的

FPGA

寄存器,

FPGA

将数据存入对应通道的发送

FIFO

,通过串并转

换后将

FIFO

中的数据转为串行码发送至外部设备

[

7

]

。

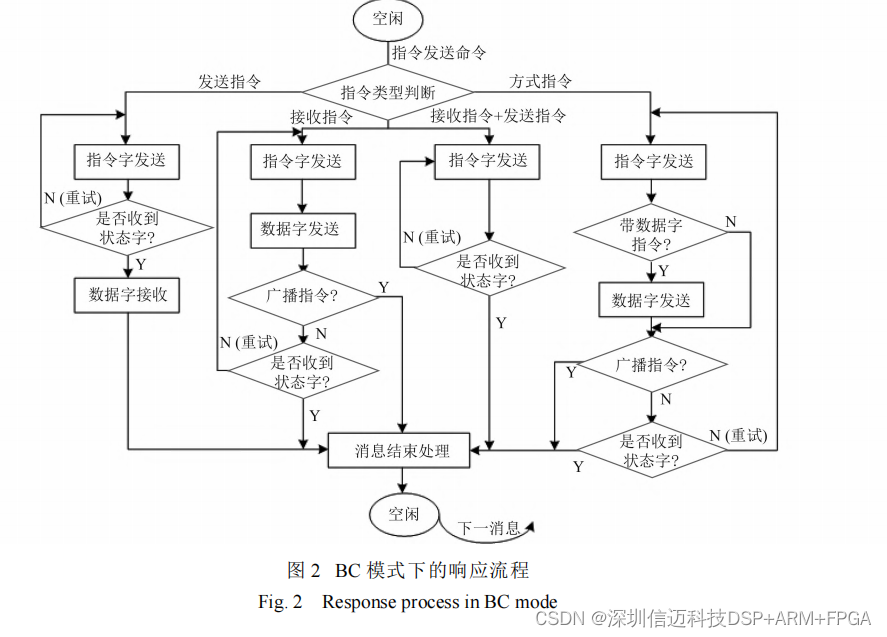

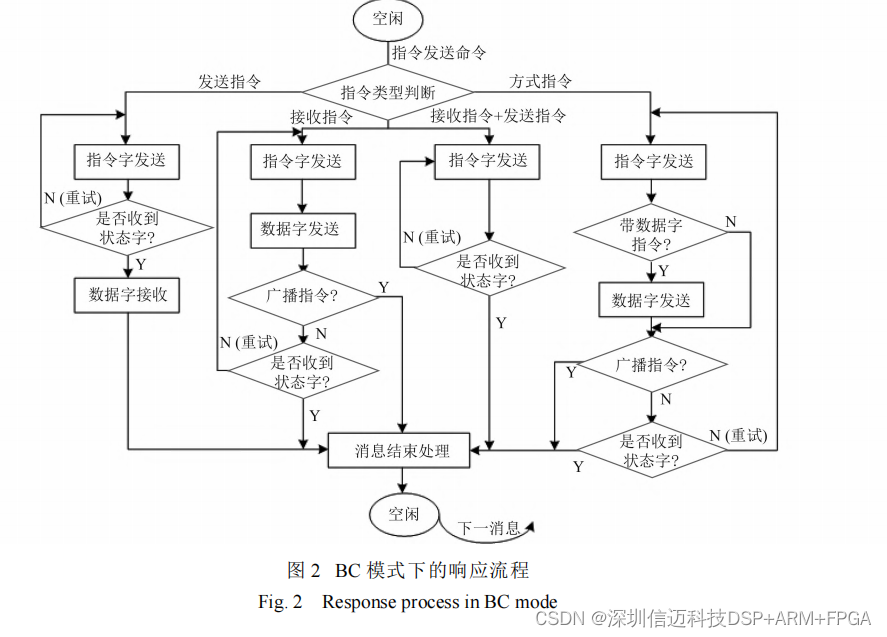

2.2 1553B

逻辑设计

信息融合系统作为系统的中心,在

1553B

通信中

担任总线控制器(

BC

)的角色,负责收发数据,同时

还需要对整个流程进行调度。根据流程,信息融合系

统需要通过发送周期和非周期信号对分系统下发指令

并获取分系统的反馈信号。为了提高

DSP

的工作精度

及效率,对于周期信号,

DSP

只控制信号发送的启

停,也即当

DSP

对

FPGA

下发了某条周期信号的启动

指令后,

FPGA

自动对该条指令计时,当时间到达周

期时,

FPGA

控制发送指令,直到

DSP

下发该条指令

的停止指令。所以信息融合系统需要完成的工作包

括:准确发送命令字和数据字;准确接收数据字和状

态字;根据需要在不同时期发送不同周期长度的周期

性信号及非周期信号 。 因此在对信息融合系统 的

BC

功能进行设计时,主要分为以下功能模块:发送模

块、接收模块、流程控制模块。

2.2.1

发送、接收模块

发送及接收模块包括发送部分、接收部分、超时

检测部分等

[

8

]

。

发送部分:主要功能是将数据经过曼彻斯特编码

后发送,根据解析出的数据字个数开始计数,当数据

字个数达到规定值时,发送完毕

[

9

]

。发送的数据包括

同步头类型、指令字及数据字

[

10

]

。

接收部分:

BC

主要接收状态字和数据字,通过解

码状态字判断接收的数据字是否正确。

FPGA

将收到

的数据字放在特定的

RAM

地址中,根据流程,

DSP

在

特定时间读取

RAM

地址中的数据字,从而获得分系

统反馈的数据和状态。

发送超时检测:为保证总线传输的可靠性,协议

规定发送时长超过

800 us

的信息按超时处理。通过计

时器进行超时检测,当接收到指令字的同步头时开始

计时,接收到状态字时计时结束,一旦计数值超过

800 us

,则表示发送超时。

BC

模式下接口的响应流程如

图

2

所示。

2.2.2

流程控制模块

信息融合系统在

1553B

通信中不仅需要完成

BC

的

基本收发功能,还需要对系统运行的整个流程进行调

度。具体来说,

FPGA

通过状态机实现流程控制的主程序。

3

功能验证

3.1

多通道串口板级验证

通过

CCS

软件和串口调试助手可完成串口在线测

试。对通道

ID

为

0

的通道进行收发测试,该通道采用

115 200 bit/s

波特率,串口助手向

0

通道发送

5f

,

f5

,

01

,

02

,

03

,

04

,

05

,

06

,

07

,

08

,

2a

,

5b

时

DSP

可

以收到。反之,

DSP

通过

0

通道向外发送数据时,串

口助手也可收到数据。其他

15

路串口也根据对应的串

口协议进行测试,数据收发正常。

3.2 1553B

板级验证

3.2.1 BC

发送非周期信号

用

CCS

软件和

BM

软件完成在线测试,通过示波

器观察波形。

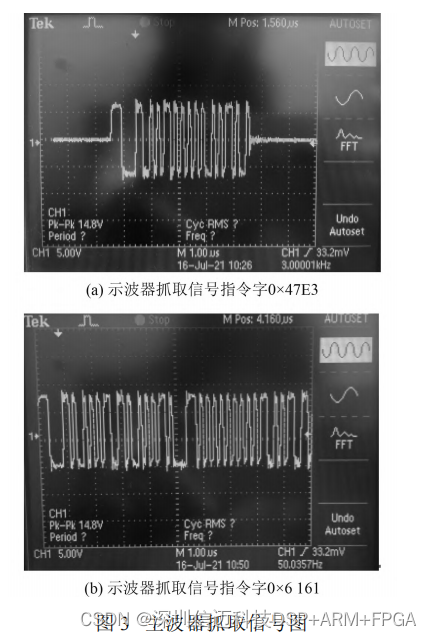

图

3

为在

BC

模式下

1553B

模块发送信号

的波形,可以看出波形良好,受干扰影响小,可以正

确进行信号解码。

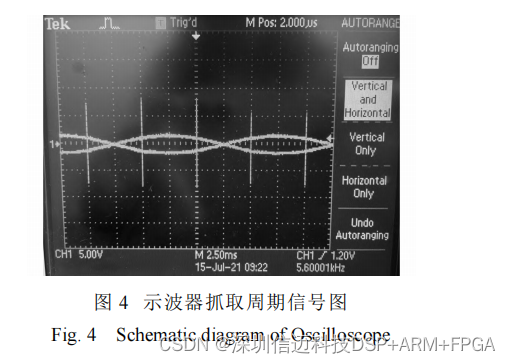

3.2.2 BC

发送周期信号

BC

向

RT

发送指令字为

0×6 161

,数据字为

0×0 022

的周期消息,周期为

5 ms

,

图

4

为实测波形图,横坐标每格为

2.5 ms

。可以看出,周期信号的周期为

5 ms

。

4

结 语

本文采用

DSP+FPGA

的设计实现信息融合系统在

多通道串口和

1553B

通信中的应用。有以下特点:

1)

灵活性。基于

FPGA

进行设计,可根据现场流程的改

变随时修改程序。

2)

扩展性。不用考虑资源限制,可

根据需要增减通道,并且根据需求可以增加更多的通

信协议。

3)

稳定性。模块化的设计,各通道各协议间

的工作互不影响,有利于系统的改进和验证。

4)

高效

性。

FPGA

采用并行数据传送,便于多通道数据交互。本

设计已应用于某大型项目的设备中,经过大量测试和

试验,可以稳定满足使用要求。

本文内容由网友自发贡献,转载请注明出处:https://www.wpsshop.cn/w/我家小花儿/article/detail/528484

推荐阅读

相关标签