- 1Hadoop/Hive/HBase/数据集成阶段测试_hbase与hive性能测试

- 2回溯法--切割问题与子集问题_分割等和子集回溯法

- 3基于K210和stm32的智能巡逻车_k210能驱动电机吗

- 4国产芯片龙迅LT8712EXI TYPE-C或者DP 1.2桥接到VGA+两个HDMI,扩展坞批量产品

- 5Shell入门学习_shell在线学习

- 6单链表的逆置(带头结点)_单链表中头结点c程序

- 7最新:Lodash 严重安全漏洞背后你不得不知道的 JavaScript 知识_lodash漏洞

- 8linux unzip解压失败( cannot find zipfile directory)

- 9FPGA原理与结构_fpga原理和结构

- 10爬取豆瓣电影评论内容、星级、评论时间、支持人数_怎么爬取星级

FPGA结构分析——IDELAY2,网口储备点3

赞

踩

写在前面:IDELAY2有4种工作模式( FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE),本篇主要对“FIXED”模式即固定数值延迟模式进行说明,后面择机再出一篇聊聊剩余的3种模式,先解决“从无到有”的问题,再想着“从有到优”的问题。

本篇所说的IDELAY2与前代的IDELAY存在一些差异,具体可在Virtex-4 User Guide 中查阅

还是像之前一样,先抛出几个问题:

1.什么是 IDELAY2?IDELAY2的作用是什么?使用场景?

2. IDELAY2结构是什么样?都有哪些端口?端口属性都是什么?

3. IDELAY2原语结构,参数属性说明?

4. IDELAYCTRL

5. IDELAY2时序是什么样?

1.什么是 IDELAY2?IDELAY2的作用是什么?使用场景?

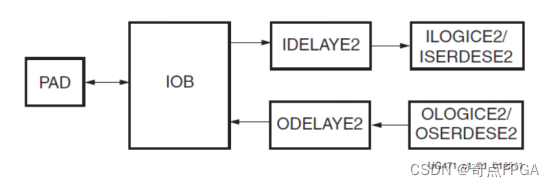

IDELAY2也即 input delay,用于在信号通过引脚进入FPGA芯片内部之前,进行延时调节,如下图,信号由PAD通过IOB后,经过IDELAY2后到达ILOGIC再到达FPGA内部或直接到达FPGA内部,用于由于器件差异或PCB走线较差导致的时钟和数据未对齐问题,从而进行微调。

2.IDELAY2结构是什么样?都有哪些端口?端口属性都是什么?

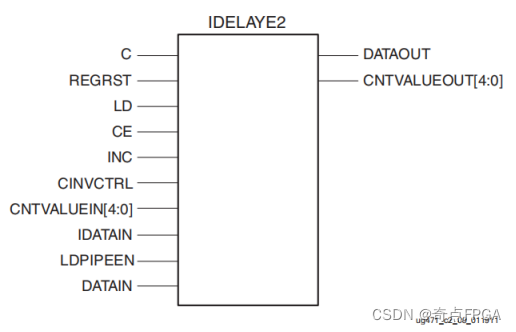

IDELAY2结构如下图:

端口说明:

C、REGRST、LD、CE、INC、CINVCTRL、CNTVALUE[4:0]、LDPIPEEN、CNTVALUEOUT[4:0]共9个端口用于VARIABLE,、VAR_LOAD,、VAR_LOAD_PIPE模式下,本篇不讨论;

IDATAIN:从IOB输出的延迟输入管脚;

DATAIN:从FPGA fabric侧输出的延迟输入管脚;

DATAOUT:延迟输出管脚。

3.IDELAY2原语结构,参数属性说明?

IDELAY原语如下:

(* IODELAY_GROUP = <iodelay_group_name> *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRL IDELAYE2 #( .CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE) .DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN) .HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE") .IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE .IDELAY_VALUE(0), // Input delay tap setting (0-31) .PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE .REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0). .SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal ) IDELAYE2_inst ( .CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output .DATAOUT(DATAOUT), // 1-bit output: Delayed data output .C(C), // 1-bit input: Clock input .CE(CE), // 1-bit input: Active high enable increment/decrement input .CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input .CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input .DATAIN(DATAIN), // 1-bit input: Internal delay data input .IDATAIN(IDATAIN), // 1-bit input: Data input from the I/O .INC(INC), // 1-bit input: Increment / Decrement tap delay input .LD(LD), // 1-bit input: Load IDELAY_VALUE input .LDPIPEEN(LDPIPEEN), // 1-bit input: Enable PIPELINE register to load data input .REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input );

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

参数说明:

IDELAY_TYPE:用于设置四种延迟模式的一种,默认FIXED,即固定延迟模式;

DELAY_SRC:用于选择延迟输入源端口,是IDATAIN或 DATAIN,默认IDATAIN;

IDELAY_VALUE:延迟数据,对于不同的参考时钟,每一拍代表的延迟时间不同;

HIGH_PERFORMANCE_MODE:TRUE用于减少抖动,FALSE用于减少功耗,默认TRUE;

SIGNAL_PATTERN:延迟输入信号类型,时钟或数据,默认为数据;

REFCLK_FREQUENCY:延迟数值IDELAY_VALUE的参考时钟,默认200MHz,即1个tap为78ps,具体参考7系列FPGA的数据手册;

CINVCTRL_SEL:动态改变时钟极性,默认FALSE;

PIPE_SEL:在VAR_LOAD_PIPE模式下,选择pipeline mode。

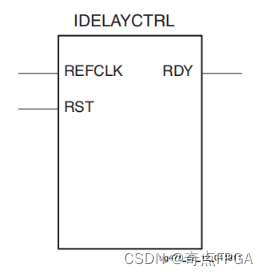

4.IDELAYCTRL:

IDELAYCTRL 和 IDELAYE 需要同时使用,IDELAYCTRL用于对 IDELAYE 延时进行校准:

REFCLK:参考时钟输入引脚,实际参考时钟频率与IDELAY_VALUE应相同;

RST:复位引脚;

RDY:校准完成信号。

原语:

(* IODELAY_GROUP = <iodelay_group_name> *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRL

IDELAYCTRL IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(REFCLK), // 1-bit input: Reference clock input

.RST(RST) // 1-bit input: Active high reset input

);

- 1

- 2

- 3

- 4

- 5

- 6

- 7

通过IODELAY_GROUP将IDELAY和IDELAYCTRL关联起来

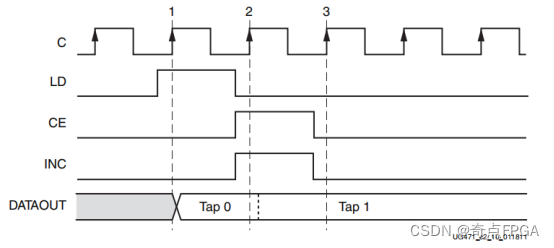

5.IDELAY2时序

Clock event 1:LD拉高,相当于复位IDELAY,输入直接到DATAOUT,未进行延迟;

Clock event 2:CE和INC同时拉高,tap值加1,即DATAOUT延迟于输入1拍;

Clock event 3:继续保持Clock event 2后的延迟拍数。

注意:在FIXED模式下,延迟tap数在一开始就被 IDELAY_VALUE配置后定下来,不可改动,所以我们可以在VARIABLE或VAR_LOAD模式下进行动态调整,当调整结束后,再使用FIXED模式将程序固定下来。