- 1git教程 .gitignore忽略文件_.gitleaksignore

- 2Python PIL库详细介绍与用法指南

- 3【STM32笔记】STM32的看门狗详解(独立看门狗和窗口看门狗)

- 4关于 Github 的三两事_com.github.bookong zest

- 5Unity中的插件机制_unity native dll

- 6基于非线性模型预测控制的STM32MPC Target-Tracking UAV目标跟踪约束及casadi插件的应用_stm32 mpc算法

- 7git 无法识别_could not get read version information from git.ex

- 8android调用flutter页面,Android上使用flutter boost从flutter页面跳转到原生页面,再返回到flutter页面时,有一定概率出现flutter页面不响应onTap事...

- 9机器学习--线性回归

- 10C++多线程学习笔记

STM32-一文搞懂ADC_stm32 adc 的注入组转换结束时能产生中断,规则组则不会。

赞

踩

目录

4.3 ADC采样时间寄存器 1~3(ADC_SMPR1~3)

4.4 ADC规则序列寄存器 1~3(ADC_SQR1~3)

1 STM32ADC简介

STM32 拥有 1~3 个 ADC(STM32F101/102 系列只有 1 个 ADC,F103系列至少有两个ADC),这些 ADC 可以独立使用,也可以使用双重模式(提高采样率)。STM32 的12位ADC是一种逐次逼近型模拟数字转换器,它有多达18个通道,可测量16个外部和2个内部信号源。各通道的A/D转换可以单次、连续、扫描或间断模式执行。ADC的结果可以左对齐或右对齐方式存储在16位数据寄存器中。模拟看门狗特性允许应用程序检测输入电压是否超出用户定义的高/低阀值。ADC的输入时钟不得超过14MHz,它是PCLK2经分频产生。

1.1 ADC特性

- 12位分辨率

- 转换结束、注入转换结束和发生模拟看门狗事件时产生中断

- 单次和连续转换模式

- 从通道0到通道n的自动扫描模式

- 自校准

- 带内嵌数据一致性的数据对齐

- 采样间隔可以按通道分别编程

- 规则转换和注入转换均有外部触发选项

- 间断模式

- 双重模式(带2个或以上ADC的器件)

- ADC转换时间:

- STM32F103xx增强型产品:时钟为56MHz时为1μs(时钟为72MHz为1.17μs)

- STM32F101xx基本型产品:时钟为28MHz时为1μs(时钟为36MHz为1.55μs)

- STM32F102xxUSB型产品:时钟为48MHz时为1.2μs

- STM32F105xx和STM32F107xx产品:时钟为56MHz时为1μs(时钟为72MHz为1.17μs)

- ADC供电要求:2.4V到3.6V

- ADC输入范围:VREF- ≤ VIN ≤ VREF+

- 规则通道转换期间有DMA请求产生。

1.2 STM32的ADC模块结构

单个ADC模块的框图如下所示

其中绿色部分为输入部分,蓝色为ADC模块核心部分,红色部分为输出部分。下面分别介绍。

2 ADC模块详解

这里分为输入单元、核心单元、输出单元进行分析。

2.1 ADC核心单元

2.1.1 规则通道和注入通道

STM32有18个多路通道,为了保证这些通道上的转换有序地、有优先级地进行,把 ADC 的转换分为 2 个通道组:规则通道组和注入通道组。任意多个通道上以任意顺序进行的一系列转换构成组转换。例如,可以如下顺序完成转换:通道3、通道8、通道2、通道2、通道0、通道2、通道2、通道15。

规则组由多达16个转换组成。规则通道和它们的转换顺序在ADC_SQRx寄存器中选择。规则组中转换的总数应写入ADC_SQR1寄存器的L[3:0]位中。

注入组由多达4个转换组成。注入通道和它们的转换顺序在ADC_JSQR寄存器中选择。注入组里的转换总数目应写入ADC_JSQR寄存器的L[1:0]位中。

如何理解规则通道组合注入通道组?

所谓过则通道就是一般的转换规则组,所有该组内的通道按顺序进行转换,而注入通道组的转换则是有较高优先级的,可以打断规则通道组的转换。规则通道相当于你正常运行的程序,而注入通道呢,就相当于中断。在你程序正常执行的时候,中断是可以打断你的执行的。同这个类似,注入通道的转换可以打断规则通道的转换, 在注入通道被转换完成之后,规则通道才得以继续转换。

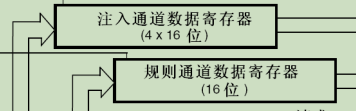

2.1.2 规则/注入通道数据寄存器

通道数据寄存器用来保存AD转换的结果,数据以左对齐或右对齐的方式存储。可以看到有四个注入通道数据寄存器,而所有的规则通道组只有一个数据寄存器!而每个注入通道都有一个单独的数据寄存器。因为规则通道转换的值储存在一个仅有的数据寄存器中,所以当转换多个规则通道时需要使用DMA,这可以避免丢失已经存储在ADC_DR寄存器中的数据。

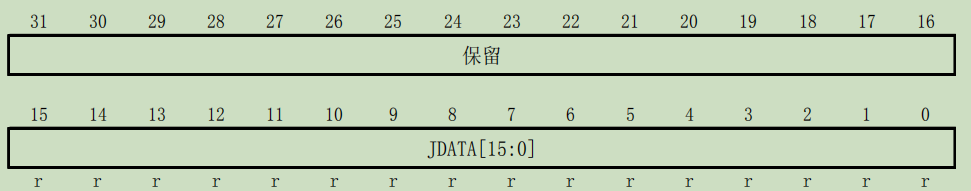

ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4)

JDATA[15:0]:注入转换的数据 (Injected data)

这些位为只读,包含了注入通道的转换结果,数据是左对齐或右对齐。

ADC规则数据寄存器(ADC_DR)

ADC2DATA[15:0]:ADC2转换的数据 (ADC2 data)

在ADC1中:双模式下,这些位包含了ADC2转换的规则通道数据。见11.9:双ADC模式

在ADC2和ADC3中:不使用这些位。

DATA[15:0]:规则转换的数据 (Regular data)

这些位为只读,包含了注入通道的转换结果,数据是左对齐或右对齐。

2.2 ADC输入单元

输入单元主要包括电源和参考电压、时钟、模拟输入通道、触发通道。

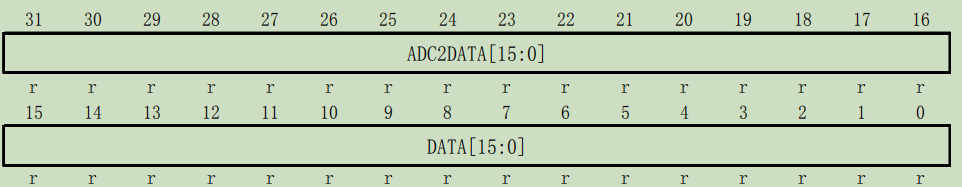

2.2.1 电源和参考电压

工作电源VDDA、VSSA

ADC使用一个独立于VDD的电源供电,过滤和屏蔽来自印刷电路板上的毛刺干扰,ADC的电源引脚为VDDA,以及独立的电源地VSSA。

参考电压VREF+、VREF-

为了确保输入为低压时获得更好精度,用户可以连接一个独立的外部参考电压ADC到VREF+和 VREF-脚上。VREF+的电压范围为2.4V~VDDA(一般直接接VDD)。64脚或以下的封装上没有VREF+和VREF-引脚,他们在芯片内部与ADC的电源(VDDA)和地(VSSA)相联。

ADC所能测量的电压范围就是VREF- ≤ VIN ≤ VREF+。因为一般接VDD(3.3V),故一般使用下,测量范围为0~3.3V。

注(1).VDDA和VSSA应该分别连接到VDD和VSS。

2.2.2 时钟

时钟来源

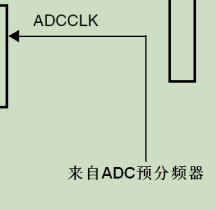

RCC控制器为ADC时钟提供一个专用的可编程ADC预分频器,如下图(时钟树部分截取)。ADC的时钟是由高速APB2时钟PCLK2经该分频器2、4、6或8分频后获得。注意ADC的输入时钟不得超过14MHz。