S32K1xx 系列安全手册_s32k1xx mcu family - reference manual

赞

踩

第 1 章 前言

1.1 概述

注意 S32K118 的具体信息在此设备合格之前是初步的。

本文档讨论了在安全相关系统中集成和使用 S32K1xx 微控制器单元 (MCU) 的要求。它旨在支持安全系统开发人员使用 S32K1xx 的安全机制构建他们的安全相关系统,并描述为实现所需的系统级功能安全完整性而应实施的系统级硬件或软件安全措施。

S32K1xx 是根据 ISO 26262 开发的,具有集成的安全概念。

1.2 安全手册假设

在 S32K1xx 的开发过程中,对 MCU 的系统级安全要求进行了假设。在系统级开发过程中,安全系统开发人员需要在特定安全相关系统的上下文中建立 MCU 假设的有效性。为实现这一点,所有相关的 MCU 假设都在安全手册中公布,可按如下方式确定:

• 假设:与特定安全系统中的功能安全相关的假设。假设安全系统开发人员满足设计中的假设。

• 特定条件下的假设:在特定条件下相关的假设。如果满足相关条件,则假定安全系统开发人员满足设计中的假设。

示例: 假设:假设系统设计为在进入 MCU 的安全状态(Safe stateMCU)时进入安全状态(Safe statesystem)。

示例:特定条件下的假设:如果输出的高阻抗状态不安全,则应将上拉或下拉电阻器添加到安全关键输出。对此的需求将取决于 S32K1xx 的未通电或复位条件(三态 I/O)的应用。

安全系统开发人员需要谨慎决定这些假设是否对其特定的安全相关系统有效。在 MCU 假设不成立的情况下,安全系统开发人员应从影响分析开始启动变更管理活动。例如,如果不满足特定假设,则应证明替代实现在满足所讨论的功能安全要求方面同样有效(例如,实现了相同级别的诊断覆盖率,相关故障的可能性同样低, 等等)。如果替代实施被证明不那么有效,则必须指定由于偏差导致的增加的故障率和减少的度量(SFF:安全故障分数,SPFM:单点故障度量,LFM:潜在故障度量)的估计. FMEDA 可用于帮助进行此分析。

1.3 安全手册指南

本文档还包含有关如何在安全相关系统中配置和操作 S32K1xx 的指南。这些指南之前有以下文本声明之一:

• 建议:建议是关于实施假设的提议,或者是在没有假设的情况下建议应用的合理措施。安全系统开发人员可以选择是否遵守该建议。

• 基本原理:特定假设和/或建议的动机。

• 实施提示:实施提示提供有关在 S32K1xx 上实施假设和/或建议的具体细节。安全系统开发人员可以选择遵循实施提示。

安全系统开发人员需要谨慎决定这些指南是否适用于他们特定的安全相关系统。

1.4 功能安全标准

假定本文档的用户熟悉功能安全标准 ISO 26262 道路车辆 - 功能安全和 IEC 61508 电气/电子/可编程电子安全相关系统的功能安全。 S32K1xx 是在 ISO 26262 上下文中看到的组件,在这种情况下,它的开发与项目或系统的开发完全分离。因此,S32K1xx 的开发被认为是一种安全元件脱离上下文 (SEooC) 开发,如 ISO 26262-10.9 脱离上下文的安全元件中所述,更具体地详述于 ISO 26262-10.9.2.3 硬件组件开发作为安全脱离上下文的元素和 ISO 26262-10 附录 A ISO 26262 和微控制器。

1.5 相关文档

S32K1xx 是根据 ISO 26262 开发的,具有针对需要高安全完整性等级的安全相关系统的集成安全概念。为了支持将 S32K1xx 集成到安全相关系统中,将提供以下文档:

• 参考手册 - 描述 S32K1xx 功能

• 数据表 - 描述 S32K1xx 操作条件

• 安全手册 - 描述 S32K1xx 安全概念和可能安全机制(集成在 S32K1xx、系统级硬件或系统级软件中),以及减少相关故障的措施

• FMEDA - 能够定制系统级安全机制的归纳分析,包括 ISO 26262(SPFM、LFM 和PMHF) 和 IEC 61508(SFF 和 β 因子 βIC)

• FMEDA 报告 - 描述 FMEDA 支持的 FMEDA 方法和安全机制,包括故障率的来源、故障模式和分析期间做出的假设。

FMEDA 和 FMEDA 报告可根据要求提供。 S32K1xx 是一种 SafeAssure 解决方案;有关恩智浦功能安全的更多信息,请访问 www.nxp.com/safeassure。

1.6 其他注意事项

在使用 S32K1xx 开发安全相关系统时,应考虑以下信息:

• S32K1xx 的处理符合 JEDEC 标准 J-STD-020 和 J STD-033。

• S32K1xx 数据表中给出的操作条件。

• 如果适用,任何已发布的 S32K1xx 勘误表。

• S32K1xx 质量协议中给出的推荐生产条件。

• 安全系统开发人员必须向NXP 报告S32K1xx 的所有现场故障。

与任何技术文档一样,读者有责任确保他或她使用的是最新版本的文档。

第 2 章 MCU 安全背景

2.1 目标应用

作为 SafeAssure 解决方案,微控制器针对需要汽车安全完整性等级 (ASIL) 的应用,尤其是:

• 汽车 - S32K 产品系列由通用 MCU 组成,适用于各种汽车应用,例如

• BCM

• 网关

• 信息娱乐连接模块

• 泊车辅助

• 电子泊车制动

• 胎压监测系统

• 电池管理

• 被动无钥匙启动

• 照明

• HVAC

• 车窗升降

• 车门控制单元

• 天窗控制单元

• 雨刮器控制单元

• DC/ BLDC 电机控制

• 工业 - 该系列还可用于需要 125°C 环境温度等级的通用工业应用。

该系列中的所有器件均围绕针对 ISO26262 ASIL-B 的集成安全概念构建。

2.2 安全完整性等级

S32K1xx 设计用于需要满足功能安全完整性等级定义的功能安全要求(例如,ISO 26262 的 ASIL B 或 IEC 61508 的 SIL 2)的汽车或工业应用。 S32K1xx 是在 ISO 26262 上下文中看到的组件,在这种情况下,它的开发与项目或系统的开发完全分离。因此,S32K1xx 的开发被认为是脱离上下文的安全元件 (SEooC) 开发。

S32K1xx 在 IEC 61508(“复杂”,参见 IEC 61508-2,第 7.4.4.1.3 节)的上下文中被视为 B 类子系统,HFT = 0(硬件容错),可用于任何模式操作(参见 IEC 61508-4,第 3.5.16 节)。

2.3 安全功能

2.3.1 MCU 安全功能

鉴于 S32K1xx 的应用独立性,无法指定特定的安全功能。因此,在 S32K1xx 的 SEooC 开发过程中,假设了 MCU 安全功能。在安全相关系统的开发过程中,MCU 的安全功能被映射到特定的系统安全功能(取决于应用程序)。假定的 MCU 安全功能是:

• 软件执行功能(独立于应用程序):从 S32K 闪存中读取指令,在指令缓存中缓冲这些指令(如果支持),执行指令,从 S32K 系统 SRAM 或闪存中读取数据,缓冲这些在数据缓存中(如果支持),处理数据并将结果数据写入 S32K 系统 SRAM。软件执行功能的功能安全主要通过集成在 S32K 上的安全机制来实现。

此外,输入/输出相关功能和调试功能采用以下方法:

• 输入/输出功能(取决于应用):S32K1xx 的输入/输出功能具有高度的应用依赖性。功能安全将主要通过系统级安全措施来实现。

• 与安全无关的功能:假设某些功能与安全无关(例如调试)。

有关详细信息,请参阅模块分类部分。

2.3.2 正确运行

S32K1xx 的正确运行定义为:

• MCU 安全功能和安全机制模块按照规范运行。

• 外围模块可通过使用系统级安全措施来限定数据或通过冗余使用模块来使用。资格认证应具有较低的相关失败风险。通常,外围模块安全措施是在系统级软件中实施的。

• 非安全相关模块不干扰其他模块的操作。

2.4 安全状态

系统的安全状态称为Safe statesystem,而S32K1xx 的安全状态称为Safe stateMCU。安全状态系统是一种操作模式,不会发生不合理的身体伤害或对任何人的健康造成损害的可能性。安全状态系统可以是预期的操作模式或系统已被禁用的模式。

假设: [SM_200] 假设进入 MCU 的安全状态(Safe stateMCU)时系统能够管理其安全状态(Safe statesystem)行为。[结尾]

2.4.1 MCU安全状态

S32K1xx的安全状态(Safe stateMCU)有:

• 运行正常(参见图 2-1 和“正确操作”部分)

• 复位中(参见图 2-1)

• 完全断电(参见图 2-1)

2.4.2 转换到安全状态系统

假设: [SM_016] 当 MCU 处于复位状态时,系统会自行转换到安全状态系统。 [结束]

假设:[SM_017] 当 MCU 断电时,系统会自行转换到安全状态系统。 [end]

假设:[SM_018] 当 MCU 没有活动输出(例如,三态)时,系统将自身转换为安全状态系统。 [结束]

原理:如果MCU没有主动输出到外部环境,MCU的状态是未知的。在这种情况下,整个系统应置于需要在系统级别完成的安全状态系统。

2.4.3 连续复位转换

如果系统在标准操作状态和复位状态之间连续切换,而没有任何设备关闭,则不认为它处于安全状态。

假设: [SM_019] 假设应用程序将复位和标准操作模式之间的连续切换识别并发出信号作为故障条件。 [结尾]

2.5 故障和故障

故障是对功能安全的主要有害影响:

• 系统故障以确定的方式表现在某个原因(系统故障)上,只能通过改变设计过程、制造过程、操作来消除程序、文件或其他相关因素。因此,针对系统故障的措施可以减少系统故障(例如,实施和遵循适当的流程)。

• 随机硬件故障可能在硬件元件的生命周期内不可预测地发生并且遵循概率分布。硬件固有故障率的降低将降低随机硬件故障发生的可能性。

当随机硬件故障确实发生时,检测和控制将减轻它们的影响。随机硬件故障是由永久性故障(例如物理损坏)、间歇性故障或暂时性故障引起的。永久性故障是不可恢复的。例如,间歇性故障是与特定操作条件或噪声相关的故障。例如,瞬态故障是粒子(α、中子)或 EMI 辐射。受影响的配置寄存器可以通过设置所需的值或通过电源循环来恢复。由于瞬态故障,元件可能会切换到自毁状态(例如,单事件闩锁),因此可能会导致永久性损坏。

• 假设:[SM_020] 假设导致失去正确操作的随机硬件故障的最小数量为 1。假设 MCU 的硬件容错 (HFT) 为 0。 MCU 设计为无故障或故障指示。 [结尾]

2.5.1 故障

以下随机故障可能会产生故障,从而可能导致违反功能安全目标。引文依据 ISO 26262-1。随机硬件故障发生在随机时间,这是由硬件中一种或多种可能的降级机制引起的。

• 单点故障(SPF):安全机制未涵盖的元件中的故障并导致单点故障。这直接导致违反安全目标。图 2-2 中的“a”显示了元素内部的 SPF,它会生成错误的输出。 IEC 61508 中与单点故障的等效项是随机故障。

无论何时在本文档中提及 SPF,都应将其视为 IEC 61508 应用的随机故障。

• 潜在故障(LF):安全机制未检测到汽车驾驶员也未察觉到的故障。 LF 是一种不违反功能安全目标本身的故障,但在与至少一个额外的独立故障相结合时会导致双点或多点故障,然后直接导致违反功能安全目标安全目标。图 2-2 中的“b”显示了元素内部的 LF,它仍然会生成正确的输出。 IEC 61508 中没有指定 LF 的等效项。

• 双点故障(DPF):单个故障与另一个独立故障相结合,导致双点故障。这直接导致违反功能安全目标。图 2-2 中的“d”显示了一个元素内的两个 LF,它们会生成错误的输出。

• 多点故障(MPF):单个故障与其他独立故障相结合,导致多点故障。这直接导致违反功能安全目标。除非另有说明,多点故障被认为是安全故障,不包含在 S32K1xx 的功能安全概念中。

• 残余故障(RF):独立导致违反功能安全目标的故障部分,其中该部分故障未被功能安全机制覆盖。图 2-2 中的“c”显示了一个元件内部的射频,尽管功能安全机制已设置到位,但它会生成错误输出,因为功能安全机制未涵盖此特定故障。

• 安全故障(SF):其发生不会显着增加违反功能安全目标的可能性的故障。本文档不涉及安全故障。 SPF、RF 或 DPF 不是安全故障。

2.5.2 相关故障

• 共因故障 (CCF):由于共同原因,两个或多个组件故障状态同时存在或在短时间内存在的相关故障的子集(见图 2- 3)。

CCF 是冗余元素的不同通道上的两个或多个元素的随机故障状态的巧合,导致定义的元素无法执行其预期的安全功能,这是由单个事件或根本原因(偶然原因,非偶然原因)引起的。 -可分配的原因、噪音、自然模式等)。 CCF 导致多个通道 (N) 的故障率大于 λsingle channel N (λredundant element > λsingle channel N) 的概率。

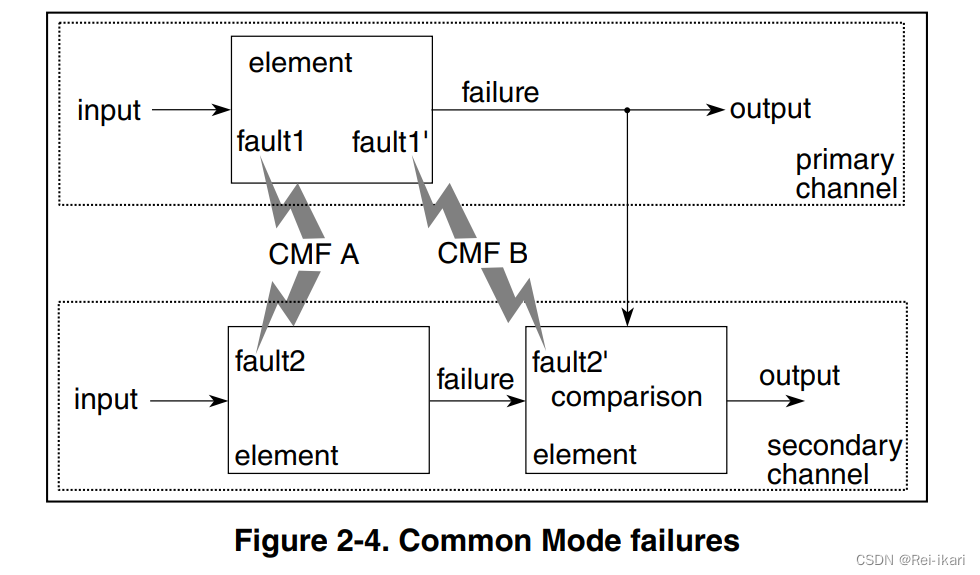

• 共模故障(CMF):单一根本原因导致冗余通道中的两个或多个(不一定相同)元件发生类似的巧合错误行为(关于安全功能),从而导致无法检测到故障。图 2-4 显示了两个冗余通道中的三个元素。一个单一的根本原因(CMFA 或 CMFB)导致主通道和冗余通道的元素之一中未检测到的故障。

• 级联故障(CF):当系统中某个元件的局部故障波及互连元件,导致同一系统和同一通道内的另一个或多个元件发生故障时,就会发生CF。级联故障是非共因故障的相关故障。图 2-5 显示了单个通道中的两个元素,其中单个根本原因导致一个元素中的故障(故障 1)导致故障(故障 a)。然后,此故障会级联到第二个元素,导致第二个故障(故障 2)导致故障(故障 b)。

2.6 单点容错时间间隔和过程安全时间

单点容错时间间隔 (FTTI)/过程安全时间 (PST) 是有可能导致危险事件的故障和为防止危险事件发生而必须完成应对措施的时间。

假设: [SM_211] 假设应用程序容错时间间隔为 100 ms。硬件措施的反应时间列表附于安全手册中。 [结束]

图 2-6 显示了系统的 FTTI:

• 正常的 MCU 操作 (a)。

• 使用适当的功能安全机制来管理故障 (b)。

• 如果没有任何合适的功能安全机制,在 FTTI 结束后可能会出现危险 (c)。

IEC 61508 中与 FTTI 等效的是过程安全时间 (PST)。每当本文档中提到单点容错时间间隔或 FTTI 时,对于 IEC 61508 应用,它应被解读为 PST。

故障指示时间是从故障发生到 S32K1xx 切换到安全状态 MCU 的时间(例如,通过驱动错误输出引脚、强制 S32K1xx 的输出为高阻抗状态或通过复位断言) 。

2.6.1 MCU 故障指示时间

故障指示时间是故障检测时间和故障反应时间之和。

• 故障检测时间(诊断测试间隔 + 识别时间)是安全机制检测到故障的最长时间,包括:

• 诊断测试间隔是在线测试之间的间隔(例如,基于软件的自检)来检测故障。

• 识别时间是安全机制检测故障所需的时间。时间最长的机制是:

• ADC 识别时间在时序方面是一项非常苛刻的硬件测试。

• 与SPLL 时钟丢失相关的识别时间:它取决于SPLL 的配置方式。

• 基于软件的功能安全机制的软件执行时间。这个时间与软件实现密切相关。

• 故障反应时间(内部处理时间 + 外部指示时间)是所有涉及的功能安全机制的反应时间的最大值,包括内部处理时间和外部指示时间:

• 内部处理时间是向其传达故障的时间/间隔相应的错误标志状态寄存器。

• 通知观察者S32K1xx 外部故障的外部指示时间(例如,更高优先级的IRQ、交叉开关争用、寄存器保存等)。

S32K1xx 故障指示时间和系统故障反应时间之和应小于功能安全目标的 FTTI。

2.7 潜在故障的潜在容错时间间隔

潜在故障容错时间间隔 (L-FTTI) 是潜在故障之间的时间跨度,它有可能与其他潜在故障同时发生并引起危险的多点事件,以及反作用的时间。完成以防止危险事件的发生。 L-FTTI 定义了各个最坏情况故障指示时间和执行相应对策的时间之和。图 2-7 显示了系统中多点故障的 L-FTTI。

IEC 61508 中没有等效的 L-FTTI。

潜在故障指示时间是从发生多点故障到故障指示迫使 S32K1xx 的输出进入高阻抗状态或通过复位断言所用的时间。

假设:[SM_212] 假设应用程序潜在容错时间间隔 (L FTTI) 通常为 12 小时。假设 MCU 将在 L-FTTI 内经历一个完整的上电/断电周期。 [结束]

理由:消除任何瞬态故障的影响。

2.7.1 MCU 故障指示时间

故障指示时间是故障检测时间和故障反应时间之和。一般来说,多点故障的故障检测时间和故障反应时间可以忽略不计,因为 L-FTTI 明显大于启动、关闭或周期性执行的典型潜在故障(小时,而不是秒)安全系统的诊断测试间隔要求。

潜在故障指示时间与潜在多点故障反应时间之和应小于功能安全目标的 L-FTTI。

注意 潜在故障检测机制对潜在故障的检测和处理必须在多点故障 (MPF) 检测间隔内完成。之后,假设故障导致多点故障,潜在故障检测不再保证正常工作。

2.8 MCU 故障指示

2.8.1 故障处理

故障处理可以分为两类:

• 启用系统级安全功能之前的故障处理(例如,在S32K1xx 初始化期间/之后)。这些故障需要在系统启用安全功能之前处理,或者在启用安全功能后比相应的 FTTI 或 L-FTTI 更短的时间内处理。

• 在启用安全功能的情况下,通过重复监督处理运行期间的故障。这些错误将在比相应的 FTTI 或 L-FTTI 更短的时间内处理。

假设:[SM_022] 假设在启用安全功能时,单点和潜在故障诊断措施在比相应 FTTI 或 L-FTTI 更短的时间内完成操作(包括故障反应时间)。 [结束]

建议:建议在启用系统级安全功能之前识别启动失败。

关于上电/启动诊断措施的典型故障反应是不初始化和启动安全功能,而是向用户提供故障指示。

软件可以读取故障源(指示时钟错误、电压错误的寄存器),并且可以在功能复位之前或之后进行。如有必要,软件也可以复位 S32K1xx。

第 3 章 MCU 安全概念

3.1 一般概念

图 3-1 是 S32K14x 功能组织的顶层图。

图 3-2 是显示 S32K11x 功能组织的顶层图。

S32K1xx 具有针对需要高安全完整性级别的安全相关系统的集成安全概念。通常,安全完整性通过以下方式实现:

• 时钟和电源、生成和分配由专用监视器监控(参见时钟和电源监控部分)

• 通过允许并发执行的分层内存保护架构确保操作干扰保护具有不同(较低)ASIL 的软件(参见操作干扰保护部分)

3.2 ECC

3.2.1 用于存储的 ECC

在 S32K14x 中,Flash 和 SRAM 存储器,除了 1400_0000h – 1400_0FFFh 区域中用作系统 RAM 的 4 KB FlexRAM 外,使用带有 SEC/DED(单错误纠正和双错误检测)的 ECC 算法) 计算存储的数据。

在 S32K11x 中,Flash 和 SRAM 存储器,除了 1400_0000h – 1400_07FFh 区域中用作系统 RAM 的 2 KB FlexRAM 和 1FFF_FC00h – 1FFF_FFFFh 区域中用作系统 RAM 的 1 KB SRAM_L 使用 ECC 算法和 SEC/DED(单错误纠正和双重错误检测)计算存储的数据。

3.2.2 ECC 故障处理

在“读取闪存”访问期间:

• 在 FTFC 中报告检测到的双位不可纠正故障,如果启用则触发中断。客户软件可以根据错误是发生在代码空间(例如:进入安全状态)还是数据空间(例如:如果数据与安全无关,则继续)以不同方式处理双位错误中断。如果在机器异常执行过程中出现不可纠正的 ECC 故障,则应进入安全状态。

• 检测到的单位错误会在不通知的情况下得到纠正。

系统 RAM 中的一位可纠正故障和双位不可纠正故障以及相应的访问地址在错误报告模块 (ERM) 中报告,如果启用,则会触发中断。系统 RAM 中的一位可纠正故障和双位不可纠正故障也会在 MCM 中报告(如果启用)。

假设:[SM_111] ECC SRAM 报告必须由软件应用程序(在 LMEM 模块中)启用,然后才能启动安全应用程序。 [结束]

错误注入模块 (EIM) 允许您在访问系统 RAM 时对读取的数据进行单位和多位反转。由于 ECC 纠正机制,ECC 中的错误可能直接违反安全目标。 ECC 应在 FTTI 内检查一次。

假设: [SM_112] 假设客户软件可以根据错误是发生在代码空间(例如:进入安全状态)还是数据空间(例如:如果数据不安全则继续)以不同的方式处理双位错误中断相关的)。如果在机器异常执行过程中出现不可纠正的 ECC 故障,则应进入安全状态。 [结束]

3.3 时钟和电源监控

3.3.1 时钟

对于安全应用,始终使用 PLL(在 S32K14x 部件中为 LOL 和 LOC 启用时钟监控)和 FIRC(在 S32K11x 部件中启用 CMU)作为系统时钟。在 S32K1xx 中,FXOSC 对系统的时钟复位指示丢失可能需要长达 512 微秒,而在 S32K11x 中,CMU 将在 5 微秒内指示 FIRC 时钟丢失。

3.3.2 电源

S32K1xx 上的低压检测(LVD)监视器和低压复位(LVR)是电压监控器。监控安全相关电压(推荐的工作电压)是否超出这些范围。由于任何超出安全相关范围的电压都有可能禁用 MCU 的故障指示机制,因此这些电源电压错误的指示可用于导致 MCU 直接转换到安全状态(复位断言)(参见S32K1xx 参考手册和 S32K1xx 数据手册中的“电源管理控制器块 (PMC)”章节了解详细信息)。

3.4 操作干扰保护

S32K1xx 是一个多主机系统。因此,它提供了安全机制来防止非安全主控器干扰内核的运行,以及处理具有不同(较低)ASIL 的软件的并发执行的机制。通过分层内存保护架构保证无干扰,包括:

• 系统内存保护单元 (MPU)

• 外设桥

• 寄存器保护

S32K1xx 上的系统 MPU 可防止不同总线主机访问地址范围。它通常供安全应用程序使用,以防止非安全相关模块访问应用程序的安全相关资源。

此外,外围网桥可以根据访问的来源及其状态(用户模式/管理员模式)限制对各个 I/O 模块的读写访问。

最后,寄存器保护可防止单个寄存器受到任何操纵,直到寄存器被解锁。

第 4 章硬件要求

4.1 系统级硬件要求

本节介绍了补充S32K1xx 集成安全机制所需的系统级硬件安全措施。

S32K1xx 集成安全概念能够以高诊断覆盖率检测 SPF 和潜在故障。然而,并不是所有的 CMF 都可以被检测到。为了检测 S32K1xx 可能无法检测到的故障,假设将有一些单独的方法使系统进入安全状态系统。

图 4-1 描绘了与外部 IC 结合的功能安全相关应用的简化应用示意图(仅显示了与功能安全相关的元件)。外部 IC 产生的电源应受到保护,以防止电压超过器件的绝对最大额定值(如 S32K1xx 数据表中“绝对最大额定值”部分所述)。

S32K1xx通过数字接口(例如SPI)反复触发外部IC的看门狗。如果存在已识别的故障(例如,看门狗未得到服务,则外部 IC 的复位输出将被置位以复位 S32K1xx。

为安全起见,冗余看门狗系统外部看门狗监视器 (EWM) 旨在监控外部电路以及 MCU 软件流程。这为重置 MCU 的 CPU 和外围设备的内部看门狗 (WDOG) 提供了备份机制。一个输出端口 EWM_out 在置位时用于复位或将外部电路置于安全模式。一个输入端口 EWM_in 允许外部电路控制 EWM_out 信号的置位。

建议:[SM_037] 建议使用外部看门狗,作为 MCU 的强大外部监控安全机制在系统级实施。不要求这些外部措施应在 IC 中提供,甚至以所述的特定方式提供(例如,外部看门狗功能可以由系统的另一个组件提供,该组件可以识别芯片已停止发送周期性数据包通信网络)。 [结尾]

4.1.1 由独立电路承担的功能

本节描述了与 S32K1xx 一起用于安全相关系统的系统中使用的外部组件。

需要注意的是,外部服务的故障模式在 S32K1xx 的 FMEDA 中只是部分考虑(例如,时钟、电源),必须由安全系统开发人员在系统 FMEDA 中进行全面分析。

4.1.1.1 高阻抗输出

如果认为 S32K1xx 处于安全状态 MCU(例如,未通电和输出三态),则包含 S32K1xx 的系统可能不符合安全状态系统。实现安全状态系统的一种可能的系统级安全措施可能是在高阻抗状态不安全时在 I/O 上放置上拉或下拉电阻。

假设: [SM_038] 如果输出引脚上的高阻抗状态不安全,则应将上拉或下拉电阻添加到安全相关输出。对此的需求将取决于未通电或复位(三态 I/O)S32K1xx 的应用程序。[结束]

基本原理:为了将与安全相关的输出提高到这样的水平,实现了安全状态系统。

4.1.1.2 复位

复位焊盘默认拉高(具体值见S32K1xx 数据手册),输入复位功能可配置。专用复位引脚功能在复位退出前可用;之后,必须将引脚配置为执行输入复位功能,以便应用程序(安全机制)可以使用它。

每当启用复位延迟时,应用程序应确保 LPO 时钟可用。

4.1.1.3 电源监控

超出规定工作范围的电源电压可能会对 S32K1xx 造成永久性损坏,即使它处于复位状态。

假设: [SM_042] 假设系统级别的安全措施在任何电源电压高于指定操作范围期间和之后保持安全状态系统。[结束]

S32K1xx 微控制器数据表提供了必须保持的特定工作电压范围。

假设: [SM_087] 假设在 MCU 上未提供监控的情况下,监控外部电源的高偏差和低偏差。 [end]

假设:[SM_088] 假设如果外部电压超出规范,MCU 将保持复位状态,并且受到保护以防止电压超过设备的绝对最大额定值(如数据表中“绝对最大额定值”部分中所述”)。 [结束]

如果电源超出范围,S32K1xx 应保持复位或断电,或必须采取其他措施保持系统处于安全状态。超出技术规定范围的过电压可能会对 S32K1xx 造成永久性损坏,即使保持复位状态也是如此。

实施提示:外部独立设备可以为外部 S32K1xx 电源提供过压监视器。如果提供的电压高于 S32K1xx 的推荐工作电压范围,则 S32K1xx 应保持断电状态。外部电源监视器将系统切换到 FTTI 内的安全状态系统,并将其保持在安全状态系统(例如,具有功能安全关闭的过压保护,或切换到第二个电源单元) .

如果 S32K1xx 电源可以设计为避免任何潜在的过压,则可以将外部电压监控排除在系统设计之外。

S32K1xx 本身会检测某些电源上的过压,但可能需要系统级措施来维持安全状态系统,以防过压情况可能导致 S32K1xx 损坏。

4.1.1.4 错误监控

如果 S32K1xx 在其状态寄存器中发出内部故障(错误标志)信号,则系统可能不再依赖其他 S32K1xx 输出的完整性来实现安全功能。如果指示错误,系统必须切换到并保持在安全状态系统,而不依赖 S32K1xx。根据其功能,系统可能会禁用或重置设备作为对错误指示的反应(请参阅安全状态下的假设)。

假设:[SM_043] 整个系统需要包括监控 MCU 寄存器中的错误标志并在指示错误时将系统移至安全状态系统的措施。 [结尾]

第 5 章软件要求

5.1 系统级别的软件要求

本节列出了在安全系统中使用S32K1xx 时应采取的必要或推荐的安全措施。

此处未明确提及的 S32K1xx 片上模块不需要在安全系统中使用特定的安全措施。复制的模块无需在应用程序或系统级别采取额外的专用安全措施即可达到非常高的诊断覆盖率。

5.2 电源

5.2.1 电源管理控制器(PMC)

PMC 管理设备上所有模块的电源电压。该单元包括用于逻辑电源的内部稳压器和一组用于低压检测器 (LVD) 和低压复位 (LVR) 的电压监视器。如果监控的电压低于 LVR 给定的阈值,则会启动复位以控制错误电压,以免导致潜在故障(有关正确的工作电压范围,请参阅 S32K1xx 数据表)。

LVD 具有警告、中断和复位(掉电)功能。有关详细信息,请参阅 S32K1xx 系列参考手册的“复位和启动”一章中的“低电压检测 (LVD)”部分。

假设: [SM_084] 应用软件必须检查 RCM 的状态寄存器是否有错误标志。 [结尾]

假设: [SM_204] 假设 ADC 用于监控 PMC 的带隙参考电压并监控连接到 ADC 的内部电源。 [结尾]

除了监视错误标志和 ADC 监视带隙参考电压之外,将 PMC 用于安全相关应用对用户来说是透明的。

欠压情况主要报告给 RCM,在那里它们通过复位直接导致转换到安全状态。之所以选择此解决方案,是因为与安全相关的电压可能会禁用 S32K1xx 的故障指示机制。

假设: [SM_085] 软件不得因过压或欠压指示而禁止 RCM 直接转换为安全状态。 [结束]

应按照电源监控中的说明从外部监控过压电源。

5.2.1.1 3.3 V 电源监控

电压检测器 LVD 和 LVR 监控 VDD 电源相对于参考电压的欠压。下图描述了电压检测器的逻辑方案。如果 LVD 在 S32K1xx 正常运行期间检测到欠压情况,则(取决于 SW 配置)触发低电压检测标志、低电压警告标志、低电压中断或破坏性复位。低电压检测系统(低电压检测标志、低电压警告标志和低电压检测复位产生)在低功耗模式下被禁用。如果电源电压低于复位触发点 (VLVR),无论工作模式如何,LVR 都会产生系统复位。

5.3 时钟

5.3.1 系统锁相环 (SPLL)

S32K14x 具有系统锁相环 (SPLL),用于生成高速时钟。 SPLL 提供了发送到 RCM 的失锁错误指示。晶体时钟上可能出现的毛刺被 SPLL 过滤(低通滤波器)。专用于系统时钟的 SPLL 分配给大多数 S32K14x 模块

5.3.1.1 初始检查和配置

系统复位后,外部晶振掉电,PLL 停用。软件应启用振荡器。系统复位后,S32K1xx 使用快速内部 RC 振荡器时钟 (FIRC) 作为其时钟源(有关 FIRC 配置的详细信息,请参见 S32K1xx 参考手册和内部 RC 振荡器中的“时钟”和“FIRC 数字接口”章节)。

假设: [SM_078] 在执行任何安全功能之前,应将基于外部时钟源的高质量时钟(低噪声、低毛刺可能性)配置为 S32K14x 的系统时钟。 [结束]

理由:由于时钟监视器使用 SIRC 作为参考来监视 SPLL 的输出,因此它不能用作 SPLL 的输入。

实施提示:系统振荡器时钟 (SOSC) 是 SPLL 源时钟。

实现提示:RCM_SRS[LOL]、RCM_SSRS[SLOL] 和 SCG_SPLLCSR[SPLLVLD] 表示发生了失锁事件。您可以配置 SCG_SPLLCSR[SPLLCM] 和 SCG_SPLLCSR[SPLLCMRE] 以在失去锁定时启用中断/复位请求。对于复位事件,将 SCG_SPLLCSR[SPLLCM] 和 SCG_SPLLCSR[SPLLCMRE] 编程为 1。对于中断,编程 SCG_SPLLCSR[SPLLCM]=1 和 SCG_SPLLCSR[SPLLCMRE]=0。

特定条件下的假设: [SM_079] 当时钟毛刺危及系统级功能安全完整性测量时,应使用 PLL 生成的时钟信号为各个功能安全相关模块提供时钟,因为 PLL 用作过滤器以减少时钟毛刺的可能性由于外部干扰。或者,应使用具有低噪声和低时钟毛刺可能性的高质量外部时钟。 [结束]

理由:减少由外部晶体及其与 S32K14x 的硬件连接引起的毛刺的影响。

实施提示:通过对系统时钟发生器 (SCG) 进行适当编程来满足此要求。

实施提示:在初始化期间或之后,但在执行任何安全功能之前,应用软件可以通过检查 SCG_CSR[SCS] 位字段来检查当前系统时钟。 SCG_CSR[SCS] = 0110b 表示系统 PLL (SPLL) 时钟被用作系统时钟。

假设:[SM_213] 应实施检查以验证使用预期的 PLL 配置,PLL 锁定正确的输出时钟。 [结束]

实施提示:您可以根据配置为在 SOSC 上运行另一个在 SPLL 上运行的 2 个定时器来比较 PLL 输入时钟和 PLL 输出时钟。如果在某个时间窗口内没有触发定时器中断来确认输出时钟 SPLL 是否正确,您可以在这种情况下选择复位器件。

5.3.2 时钟监控单元 (CMU)

S32K11x 变体没有 SPLL,系统时钟应由 FIRC 驱动。启动时,CMU 未初始化,FIRC 是默认系统时钟。CMU 由 8 MHz SIRC 驱动,以确保独立于受监控时钟 (FIRC)。由于时钟超出可编程界限和监控时钟丢失,CMU 会标记与条件相关的事件。如果监控时钟离开设备的编程频率范围,则配置的反应由 CMU 生成。 S32K11x 器件包括 CMU,它仅监控作为系统时钟主要来源的 FIRC。 CMU 使用 SIRC(8 MHz 慢速内部振荡器)作为参考时钟,以独立于被监控时钟运行。

目的是检查:

• FIRC(系统时钟的主源)丢失

• FIRC(系统时钟的主源)超出可编程频率范围(频率过高或过低)

对于安全相关应用,CMU 的使用是强制的。如果 CMU 监控的模块被应用安全功能使用,用户应确认 CMU 未被禁用。

5.3.2.1 初始检查和配置

假设:[SM_083] 需要以下监控功能:

• 快速内部参考时钟丢失

• 系统 FIRC 频率高于(可编程)频率参考上限

• 系统 FIRC 频率低于(可编程)频率参考下限

[结束]

基本原理:监控系统时钟信号的完整性。

建议:CMU 应用于监控 firc 时钟以实现功能安全相关应用。应用软件应检查 CMU 是否已启用,因为它默认是禁用的。建议在时钟丢失或时钟超出范围的情况下始终生成复位。对于超出范围的时钟条件,应在中断条件内产生复位事件。在进入任何低功耗模式之前,必须通过配置 PCC 模块中 CMU 控制寄存器的 CGC 字段来禁用 CMU 并关闭 CMU 时钟。

实施提示:一般而言,在启用 CMU 监控之前,应执行以下依赖于应用程序的配置。

• 第一个配置与 CMU0 实例中的低频参考 (CMU_FC_LTCR[LFREF]) 有关,用于丢失 FIRC 时钟检测和复位生成。

• 第二个配置与CMU1 实例中用于中断生成的高频(CMU_FC_HTCR[HFREF])和低频参考(CMU_FC_LTCR[LFREF])有关。

通过写入 CMU_FC_GCR[FCE]=1 启用 CMU 后,CMU 需要几个周期才能开始内部操作,如 CMU_FC_SR[RS]=1 所示。必须在 CMU_FC_SR[RS]=1 后启用安全应用程序。

5.3.3 带有 SPLL 的器件的时钟监视器

在启动时,时钟监视器没有初始化,FIRC 是默认的系统时钟。

上电时时钟监视器不会检测到系统振荡器时钟 (SOSC) 上的卡滞故障,因为监视单元未初始化并且 S32K14x 仍在 FIRC 上运行。

时钟监视器由 8 MHz 慢速内部 RC 时钟 (SIRC) 驱动,以确保独立于被监视时钟。由于时钟超出可编程界限和参考时钟丢失,时钟监控与条件相关的标志错误。如果监控时钟离开设备的指定范围,则在相应的状态寄存器中设置错误标志。 S32K14x 包括 SOSC 和 SPLL 的时钟监视器。

时钟监视器使用 SIRC(8 MHz 内部振荡器)作为参考时钟,独立于被监视时钟运行。它们的目的是检查由于以下原因导致的错误情况:

• 外部晶振 (SOSC) 时钟丢失

• SPLL 时钟超出可编程频率范围(频率过高或过低 - 时钟丢失)

• SPLL 时钟丢失

时钟监控监督各种时钟源的频率范围。如果出现异常行为,则将信息转发到相应的 SCG 状态寄存器。

假设: [SM_080] 对于安全相关应用,必须使用时钟监视器。如果 SCG 监控的模块被应用安全功能使用,用户应确认时钟监控没有被禁用,并且它们的故障由软件管理。 [结束]

5.3.3.1 初始检查和配置

假设:[SM_081] 需要以下管理器功能:外部时钟丢失、SPLL 频率高于(可编程)频率参考上限和 SPLL 频率低于(可编程)频率参考下限.[结束]

基本原理:监控时钟信号的完整性

建议:时钟监控器应用于功能安全相关模块正在监控和使用的每个时钟。应用软件应检查时钟监视器是否已启用以及它们的故障是否由软件管理。为防止时钟复位事件意外丢失,在进入任何低功耗模式之前,应禁用所有时钟监视器。

实现提示:一般来说,在开启时钟监控之前,需要执行以下两个应用相关的配置。

• 第一个配置与晶体振荡器时钟(SOSC)监视器有关。

软件配置 SCG_SOSCCSR[SOSCM] 并启用系统 OSC 时钟监视器。仅当锁定寄存器 (LK) 位为零时,才能写入 SCG SOSC 控制状态寄存器 (SCG_SOSCCSR)。将分频后的 SIRC 频率与 SOSC 进行比较。

• 第二个配置与被监控的PLL 时钟有关。

SCG_SPLLCSR[SPLLCM] 使能 PLL 时钟监视器。仅当锁定寄存器 (LK) 位为零时,才能写入SCG PLL 控制状态寄存器 (SCG_SPLLCSR)。

5.3.4 系统振荡器时钟 (SOSC)

FlexCAN、CLKOUT 和其他外设具有直接从 SOSC 提供时钟的模式。如需完整列表,请参阅 S32K1xx 系列参考手册的“时钟分配”一章。

每当需要严格的容差(高达 0.1%)时,都应选择振荡器时钟。晶振时钟也比外设时钟具有更好的抖动性能。

5.3.4.1 初始检查和配置

假设:[SM_075]FlexCAN 和 CLKOUT 都具有由 SOSC 直接提供时钟的模式,除非时钟毛刺的影响被 SOSC 充分检测到,否则不应在正常操作中使用这些模式应用 FT-COM 层。[结束]

5.3.4.2 运行时检查

假设:[SM_076] 在运行任何安全元件功能之前,软件应检查系统时钟是否可用,并且由 SOSC 提供。[结束]

5.3.5 内部 RC 振荡器

三个内部 RC 振荡器是实施:

• 快速内部RC (FIRC) 的标称频率为48 MHz。

• 慢速内部RC (SIRC) 的标称频率为8 MHz。

• LPO_CLK,提供 128 kHz。可以从中导出 32 kHz 和 1 kHz 时钟。

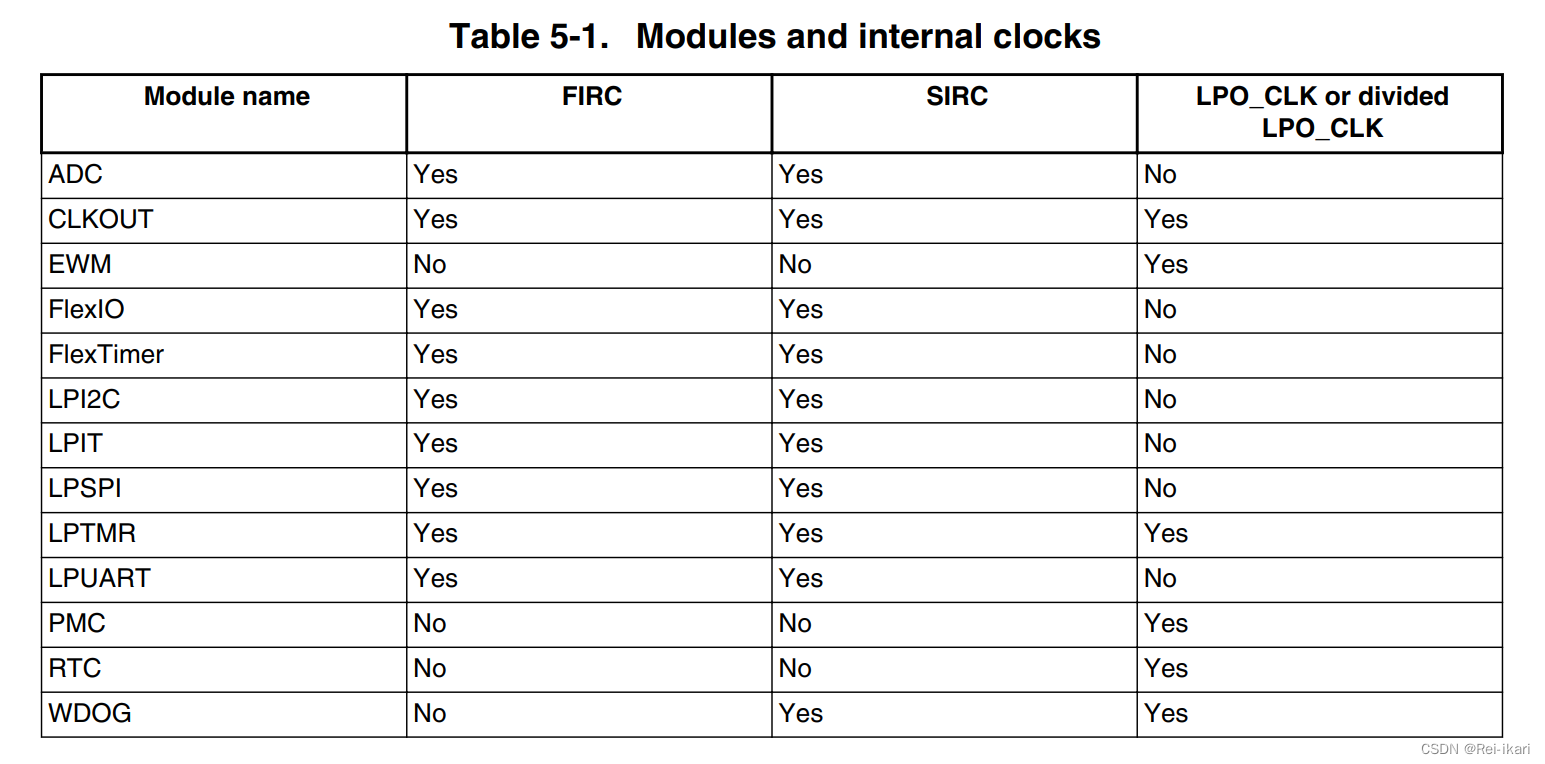

必须考虑整个电压和温度范围内的频率精度(参见 S32K1xx 数据表)。可以使用内部时钟产生的时钟的功能安全相关模块如下表所示。更多详细信息,请参见 S32K1xx 系列参考手册的“时钟分配”章节。

5.3.5.1 初始检查和配置

快速 IRC 时钟错误标志 (SCG_FIRCCSR[FIRCVLD]) 应用于检查快速内部 RC 振荡器 (FIRC) 的可用性。此外,应通过执行一个软件测试例程来验证标称 FIRC 频率,该程序比较基于不同时钟源(FIRC 和 SOSC)的两个独立定时器(例如 FTM 和 WDOG)的计数器值。

假设:[SM_073] 通过比较独立定时器基于不同时钟源生成的计数器值,测量 FIRC 频率并将其与预期频率进行比较。此测试在上电后但在执行任何安全功能之前执行。 [结束]

理由:检查 FIRC 的完整性

5.3.5.2 运行时检查

应使用基于不同时钟源比较两个独立定时器的计数器值来验证 FIRC 的可用性和频率。这种方法允许使用 SOSC 作为参考时钟源来测量 FIRC 频率。

假设: [SM_074] 为检测 FIRC 故障,应用软件应利用基于不同时钟源比较两个独立定时器的计数器值的方法,将 FIRC 频率与预期值 48 MHz 进行比较。[结束]

实施提示:有关如何检查 FIRC 的说明,请参阅假设:在初始检查和配置中。

如果测得的 FIRC 频率与预期值不匹配,则存在所有安全措施完全失效的可能性。然后,软件应使系统进入安全状态系统,而不依赖于 FIRC 驱动的模块。

建议:为了增加故障检测,该功能安全完整性措施应在每个 FTTI 执行一次。

5.4 闪存

5.4.1 闪存

S32K1xx 提供带有ECC 的可编程非易失性闪存(NVM),可用于指令和/或数据存储。

用于闪存的 ECC 将 All-0 标记为错误,但允许 All-1 情况考虑读取已擦除、未初始化的闪存。

闪存子系统有一个带有内部存储器的内部嵌入式控制器,如果在安全应用期间完成嵌入式控制器的激活,则应将其视为安全相关。嵌入式闪存控制器的激活在以下情况下完成:

• 擦除/编程闪存阵列

• EEPROM 仿真

• 使用安全引擎

5.4.1.1 EEPROM

我们建议您使用软件仿真将安全相关数据直接存储到 DFLASH 中。但是,如果使用 EEPROM 仿真来存储与安全相关的数据,则必须在这种情况下实施软件检查,以验证内存控制器的功能是否正确。

在这种情况下,用户需要通过 PGMPART 命令将 FlexNVM 配置为 EEPROM。

实施提示:可以根据 SETRAM 命令实施检查。此命令会将活动记录从 FlexNVM 复制到 EEEPROM 仿真,并且 EEPROM 仿真可以在命令执行前后进行 CRC 检查,以确保在 FlexNVM 中备份了正确的数据。

S32K116 和 S32K118 提供一个 FlexNVM 块 (32 KB),由 2 KB 扇区组成,用于 EEPROM 仿真。 S32K142、S32K144 和 S32K146 提供一个 FlexNVM 块 (64 KB),由 2 KB 扇区组成,用于 EEPROM 仿真。 S32K148 提供高达 512 KB(作为程序闪存的一部分)的 FlexNVM,包括用于 EEPROM 仿真的 2 KB 扇区。执行 ECC 算法来纠正单位故障和检测双位故障。双位错误通过状态寄存器和中断(如果已配置)发出信号。

假设: [SM_114] 使用 EEPROM 存储信息的软件将使用检查来检测从 EEPROM 仿真返回的不正确数据。 [结束]

通常,将存储 CRC 以验证数据。

执行闪存编程操作后,您必须检查安全相关代码的完整性。为此,您可以使用 CRC 检查或 CMAC 检查,具体取决于应用程序。

5.4.1.2 运行时检查

如果嵌入式闪存控制器在安全应用过程中被激活,应进行应用软件检查以检查预期操作的状态以及闪存阵列中保存的安全相关数据的内容。在编程/擦除操作的情况下,应在编程/擦除操作结束时检查编程/擦除扇区的内容。编程/擦除操作的结果可以基于回读方案,其中写入的字被回读并与预期值进行比较。安全相关数据应通过 CRC 校验保存以进行验证。为此,您可以使用内置的 HW CRC。

假设:[SM_116] 应实施软件测试以检查由闪存控制器中的永久故障引入的潜在多位错误。假设如果嵌入式控制器被归类为安全相关,则嵌入式控制器的激活伴随着闪存完整性检查。首先,应检查启动的闪存相关命令是否已完成并返回通过状态。根据安全应用,应对代码闪存或/和数据闪存进行闪存完整性检查。安全相关代码和数据应使用 CRC 或哈希签名保存在闪存中,以检测任何完整性违规。 [end]

假设: [SM_117] 应实施软件安全机制以确保对闪存的任何写操作的正确性。 [end]

理由:检查写入数据是否与预期数据一致 您应该在每次写入操作后或对闪存进行一系列写入操作后执行此测试。

实施提示:闪存的编程可以通过检查 FTFC_FSTAT[MGSTAT0] 内存控制器命令完成状态标志的值来验证。此外,写入的数据可以被读回,然后通过软件检查是否与编程数据相同。数据回读可以在边距读取模式下执行(FCMD = 0x02(程序检查))。这可以使用对弱编程或擦除状态更敏感的读取裕量来验证编程数据。

假设:[SM_119] 应检查闪存 ECC 故障报告路径,以验证检测到的 ECC 故障是否被正确报告。[结束]

基本原理:此测试的目的是确保正确报告故障检测。

实施提示:闪存ECC故障报告检查在软件中执行。

5.4.1.3 安全

由于安全子系统中的永久性/暂时性故障,数据可能在加密或解密过程中被破坏,安全引擎的错误输出可能在安全应用程序中用作安全相关变量。

建议:[SM_118] 根据应用类型及其对安全子系统的安全要求,建议实施一组软件检查以保证安全操作中涉及的数据完整性。 [结尾]

5.5 SRAM

5.5.1 纠错码 (ECC)

S32K1xx 包括纠错码 (ECC) 支持,以提高功能和瞬态故障检测能力。由传统 ECC/EDC 保护的内存生成并检查内存单元本地的附加错误奇偶校验信息,以检测和/或纠正内存中存储数据发生的错误。

内存中的 All-X 错误有特殊处理,因为人们认为 All-X 错误的概率可能高于随机错误位。

RAM 的 ECC(不包含地址)将 All-X 标记为错误。

对于用作系统 RAM 的 4 KB(对于 S32K14x 系列)或 2 KB(对于 S32K11x 系列)FlexRAM 或(对于 S32K11x 系列)1 KB SRAM_L 位置(也可用作消息跟踪缓冲区),不会产生 ECC 和访问错误。

假设:[SM_113]假设如果安全相关数据存储在该内存中,则进行额外的完整性检查。 [完]

详情见ECC存储。

5.6 处理模块

5.6.1 Cortex-M4/M0+ 结构核心自测 (SCST)

Cortex-M4/M0+ 结构核心自测 (SCST) 是 NXP 的软件产品。它需要在 Core 中检测 SPF,并且必须在 FTTI 中执行一次。它被开发用于通过使用一组固定的操作数执行机器操作码并比较它们的执行结果来检测内核中的硬件永久性故障。该库被认为是脱离上下文的安全元素,是根据 ASIL-B 开发的。

SCST 交付包含 SCST 库、质量包和安全包。

• 质量包包含代码覆盖分析、MISRA 报告、软件需求规范和测试规范。

• 安全包包括SCST 故障覆盖估计、安全分析和概念以及SCST 安全手册。

结构内核自检库安全手册包含一系列建议和假设,用户应满足和验证这些建议和假设,以便正确使用 Cortex-M4/M0+ 内核的 SCST 库。

5.6.2 禁用操作模式

系统级和应用软件必须确保在运行与功能安全相关的操作时不会激活本节中描述的功能。

5.6.2.1 调试模式

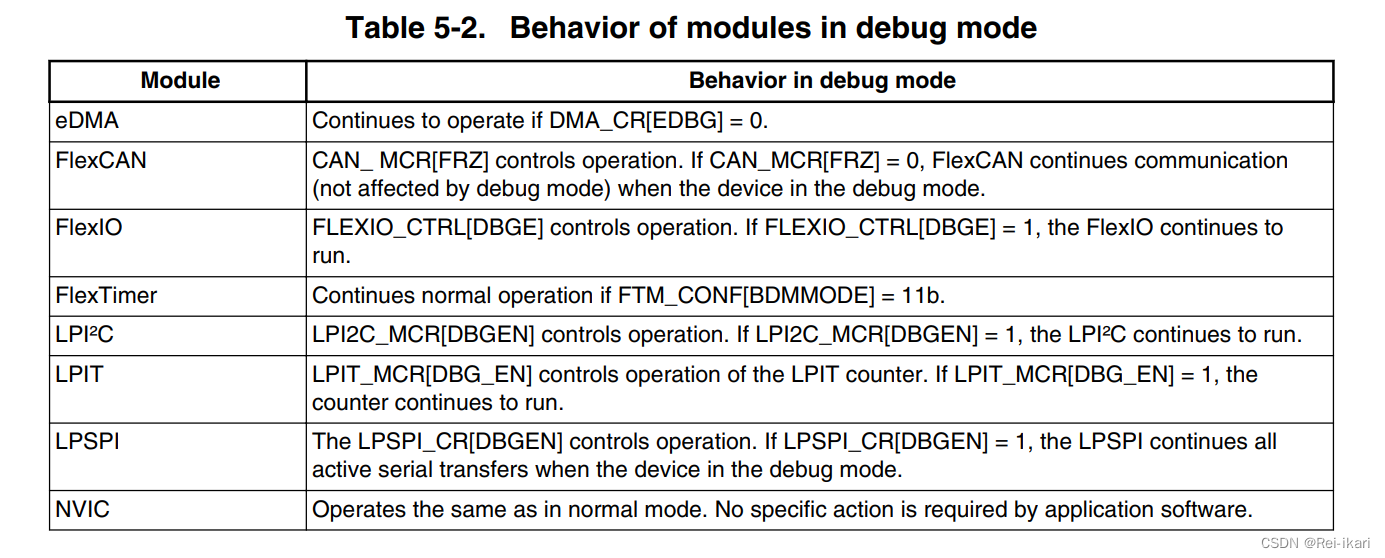

S32K1xx 的调试功能如果在功能安全相关应用程序运行期间被激活,则可能会导致故障。它们可以暂停内核、触发断点、写入内核寄存器和地址空间,等等。为减少干扰应用软件正常运行的可能性,S32K1xx 不得进入调试模式。

JTAG_TMS 信号的状态决定了系统是否正在调试或系统是否在正常工作模式下运行。当 JTAG_TMS 为逻辑低电平时,JTAGC TAP 控制器保持复位以进入正常操作模式。当它为逻辑高时,JTAGC TAP 控制器被启用以进入调试模式。在引导期间,必须采取措施确保 JTAG_TMS 不会被外部源断言,从而可以避免进入调试模式。在现场,应将 JTAG_TMS 拉低以确保禁用 JTAGC TAP 控制器。

假设:[SM_047] 当设备用于安全相关功能时,将在现场禁用调试。 [结束]

特定条件下的假设:[SM_048] 如果看门狗定时器 (WDOG)、低功耗串行外设接口 (LPSPI)、低功耗周期性中断定时器 (LPIT)、FlexCAN 等模块,或通常任何可以冻结的模块在调试模式下,与功能安全相关,要求应用软件配置这些模块以在调试模式期间继续执行,并且在进入调试模式时不冻结模块操作。 [结束]

原理:提高对调试模式错误激活的恢复能力

实施提示:在调试模式下,看门狗控制和状态寄存器 (CS) 中的 DBG 位控制 WDOG 的操作。如果 CS[DBG] = 1,WDOG 计数器继续在调试模式下运行。

在调试模式下,模块的行为如下:

5.6.3 附加配置信息

5.6.3.1 堆栈

堆栈上溢和堆栈下溢是由于应用软件中的系统故障导致的共模故障。在堆栈上使用过多内存(推送大量数据)时会发生堆栈溢出。从内存中读取(弹出)过多数据时会发生堆栈下溢。堆栈包含有限数量的内存,通常在应用软件的开发过程中确定。当程序尝试使用比堆栈上保留(可用)更多的空间时(当访问超出堆栈上限和下限的内存时),堆栈被称为溢出或下溢,通常会导致程序崩溃。

在堆栈溢出和堆栈下溢的情况下实施监督堆栈并分别生成故障信号的措施可能是有益的。

5.6.3.1.1 初始检查和配置

假设条件:[SM_139] 当应用软件内部的系统故障导致堆栈下溢和堆栈溢出危及系统级时,可以实施功能安全机制来检测堆栈下溢和堆栈溢出故障. [结尾]

基本原理:在堆栈溢出或堆栈下溢错误的情况下发出通知

实现提示:可以使用 DWT 中的数据观察点比较器在堆栈上溢和下溢时触发调试监视器异常。

5.6.3.2 S32K1xx 配置

假设:[SM_140] 应用软件必须在激活安全相关功能之前验证 S32K1xx 的初始化是正确的。[end]

启动后,应用软件必须确保满足本节描述的条件之前启用安全相关功能。

下面是在执行任何安全功能之前必须通过的安全完整性功能检查的最少数量列表:

• 启用 LPO

• 启用 WDOG

• SCG 和 RCM 状态寄存器中的错误标志处理:

• 检查 SCG 中的时钟源和时钟错误寄存器

• 检查 RCM_SRS 寄存器中最多复位的来源

• IRC_SW_CHECK(另请参阅初始检查和配置)

• WDOG 快速测试(请参阅看门狗的快速测试)

• ERM SW 检查与系统中的 ECC 相关的内存错误事件的通知RAM

• 启用时钟监视器

未列出先决条件。如果这些检查中的任何一个失败,则无法确保功能安全。

建议:将微控制器配置为在对设备上未使用的外设插槽进行任何访问时触发异常。

建议:引导后,对未实现的内存空间执行预期访问并检查是否发生预期的中止。

基本原理:检测地址和总线逻辑中的错误寻址和故障。

建议:将未使用的中断向量配置为指向或跳转到非法执行、包含非法指令或以某种其他方式导致检测到它们的执行的地址。

建议:在超级用户模式下仅运行硬件相关软件(操作系统、驱动程序)。

基本原理:降低意外写入配置寄存器影响 S32K1xx 安全功能执行的风险,或因更改而禁用安全机制。

建议:使用硬锁保护(如果该选项可用于寄存器)或使用外设访问控制来保护所有配置寄存器,以及在应用程序执行期间未修改的寄存器。

基本原理:为了降低意外写入配置寄存器影响 S32K1xx 安全功能执行的风险,或者由于它们的变化而禁用安全机制。

实现提示:一些平台外的外设有自己的寄存器保护。可以通过寄存器保护来保护的每个外设都有一个锁定位。该位可置位以启用相关外设的保护。

可以设置锁定寄存器位 (PORT_PCRn_LK = 1) 以获得最佳引脚控制寄存器写保护。

5.6.4 交叉开关(AXBS-Lite)

交叉开关设计用于最小化门数,并允许从任何主机(例如内核、eDMA)到任何从机(例如存储器、外设桥等)的并发事务。

5.6.4.1 运行时检查

交叉开关不需要初始化。您可以检查与交叉开关从属和主控配置相关的 MCM 寄存器中是否存在总线从属连接或主连接。

5.6.5 内存保护单元

作为一个多主机并发总线系统,S32K1xx 提供了安全机制来防止非安全主机干扰安全内核的运行。

S32K1xx 还包含处理具有不同或更低 ASIL 等级的软件任务的并发操作的机制。

建议:对于与安全相关的应用,应使用系统 MPU 确保只有授权的软件任务才能配置模块,并且只能根据其访问权限访问其分配的资源。

5.6.5.1 内存保护单元 (MPU)

系统内存保护单元 (MPU) 在交叉开关 (AXBS-Lite) 处提供内存保护。系统 MPU 允许将物理内存分成 16 个不同的区域。每个 AXBS-Lite 主机(Core、eDMA)可以被分配到每个区域的不同访问权限。系统 MPU 可用于防止非安全主机(包括 eDMA)访问受限内存区域。

允许完成具有足够访问控制权限的内存访问,而未映射到任何区域描述符或权限不足的访问会以保护错误响应终止。系统 MPU 实现了一组程序可见的区域描述符,用于监视所有系统总线地址。结果是具有二维连接矩阵的硬件结构,其中区域描述符代表一维,各个系统总线地址和属性代表第二维。

假设: [SM_094] 假设系统 MPU 在用于安全应用之前已检查其功能是否正确。可以配置每个当前主站的可能访问权限并检查预期的系统反应。检查应在 L-FTTI 内完成一次(在启动时)。 [结束]

5.6.5.2 初始检查和配置

某些条件下的假设:[SM_095] 系统级功能安全完整性措施必须涵盖总线操作,以减少共享资源被当前主设备(核心、eDMA)错误修改的可能性。 [结束]

基本原理:系统 MPU 级别的访问限制是防止特定软件例程(进程)对某些预定义的内存映射地址位置进行不必要的读/写访问。

实施提示:系统 MPU 应用于确保只有授权的软件例程才能配置模块,并且所有其他总线主控器(eDMA,核心)只能根据其访问权限访问其分配的资源。

5.6.6 嵌套向量中断控制器 (NVIC)

嵌套向量中断控制器 (NVIC) 提供了对中断请求 (IRQ) 进行优先级排序、阻止和引导的能力。 NVIC 可能会因丢弃或延迟 IRQ、将它们引导到错误的核心或处理程序或创建虚假的而失败。没有提供特定的硬件保护来降低由 IRQ 之前的故障引起的虚假或丢失中断请求的可能性,例如中断线上的电磁干扰 (EMI)、外设中断寄存器中的位翻转或故障在外围设备中。嵌套向量中断控制器 (NVIC) 可以丢弃、延迟或创建虚假中断。

假设: [SM_098] 假设应用软件将针对所有安全关键中断检测 NVIC 的关键故障模式。 [end] 实现

提示:检测虚假或多个意外中断的一种方法是应用软件在执行中断服务程序(ISR)之前读取相应外设的中断状态寄存器。这将检查各个外设是否确实请求了中断。

5.6.6.1 周期性低延迟IRQ

可以配置片上定时器在产生中断请求时启动,并且应用软件可以读取定时器值以确定何时进入ISR。该方法可用于确定测量的中断延迟是否超过要求。

假设:[SM_099] 周期性低延迟 IRQ 将使用正在运行的定时器/计数器来确保它们的调用周期是预期的。[end]

5.6.6.2 运行时检查

假设在某些条件下:[SM_100] 对虚假或丢失中断没有弹性的应用程序请求可能需要包括系统级别的检测或保护措施。 [结束]

基本原理:管理虚假或丢失的中断请求。

实现提示:检测虚假中断的一种可能方法是在执行中断服务程序(ISR)服务代码之前检查相关外设的中断状态寄存器(轮询)中的相应中断状态。

5.6.7 增强型直接存储器访问 (eDMA)

eDMA 提供了在内核干预最少的情况下执行数据传输的能力。它支持可编程的源地址和目标地址以及传输大小。

软件必须检测 eDMA 内部和外部的安全相关故障。

实施提示:作为软件检查示例,可以将签名写入目标地址,然后在传输完成后执行检查以验证签名已被覆盖。通道链接可用于在 DMA 传输期间链接完成次要或主要循环的通知。

5.6.7.1 运行时检查

假设:[SM_101] eDMA 将由检测虚假、过度或持续激活的软件监督。 [结束]

基本原理:防止 eDMA 消耗交叉开关上的传输带宽,并防止它在错误的时间点复制数据

实施提示:可能的软件实施以防止虚假或丢失的中断,或传输超过MCU 的负担如下:

• 软件计算在控制周期内触发的eDMA 传输次数,并将该值与预期值进行比较。

• 如果eDMA 用于管理PDB 和ADC 的模拟采集,则转换后的ADC 通道数与采集值一起保存到ADC_RN 和ADC_SC2 中。 eDMA 将该值从 ADC 传输到相应的 SRAM 位置。通过将转换后的通道与预期通道进行比较,可以检测到虚假或丢失的传输请求。

• 可以在传输之前在源处对安全关键数据计算校验和,然后在传输后在目的地重新计算校验和。

特定条件下的假设:[SM_102] 对虚假或缺少与功能安全相关的 eDMA 请求没有弹性的应用程序不能使用 LPIT 模块来触发与功能安全相关的 eDMA 传输请求。 [结束]

基本原理:降低故障 LPIT(非冗余)触发意外 eDMA 传输的可能性

5.6.7.1.1 非复制 eDMA 传输

在使用 eDMA 将数据传输到非复制外设(如 GPIO)的情况下,需要额外的软件措施,因为 eDMA 通道多路复用器的两半不会隐式地相互监督。

假设:[SM_104] 如果安全相关软件正在使用 eDMA 将数据传输到非复制外设或 RAM 内,则以下情况成立:不应使用 eDMA 通道多路复用器的“始终开启”通道。相反,eDMA 应该由软件触发。如果使用“始终开启”通道,则必须通过软件检测它们的故障。在这种情况下,软件必须确保 eDMA 传输按预期以正确的速率和正确的次数触发。此测试应检测意外的虚假中断。 [结束]

5.6.8 复位控制模块 (RCM)

5.6.8.1 初始检查和配置

建议:要启用关键事件以触发复位序列,您应该将 RCM 系统复位中断启用寄存器 (RCM_SRIE) 寄存器写入零。如果客户想要排除特定的关键事件触发复位序列,您应该设置相应的位 (= 1)。

在任何时候,客户软件都可以启动重置序列。您可以通过软件设置 ARM 内核的应用中断和复位控制寄存器中的 SYSRESETREQ 位来触发芯片复位。或者,您可以使用 WDOG 计时器来生成复位。

5.6.9 看门狗定时器(WDOG)

看门狗定时器(WDOG)的目的是在程序的各个元素以错误的顺序或在过长的时间段内处理时检测有缺陷的程序顺序。一旦 WDOG 启用,它需要定期和及时地执行看门狗服务程序。服务过程必须在配置的时间窗口内执行,在服务超时到期之前。当发生超时时,WDOG 可以首先产生一个中断。

假设: [SM_067] 在执行安全功能之前,必须启用 WDOG 并硬锁定配置寄存器以防止修改。此外,应验证时钟源是否配置为 LPO。 [结尾]

假设:[SM_202] WDOG 时间窗口设置必须设置为小于 FTTI 的值。检测延迟应小于 FTTI。 [end]

实现提示:所有看门狗控制位、超时值和窗口值在复位后只写一次。这意味着在发生写入后,除非发生复位,否则它们无法更改。这提供了一种强大的机制来配置看门狗,并确保在配置后不会错误地禁用或修改看门狗配置。这是由用户首先配置窗口和超时值,然后是其他控制位,并确保 CS[UPDATE] 也设置为 0 来保证的。只有在复位后除 CNT 之外的所有寄存器都写入一次后,新配置才会生效.否则,WDOG 默认使用复位值。如果不使用窗口模式(CS[WIN] 为 0),则无需写入 WIN 即可使新配置生效。超时寄存器 (WDOG_TOVAL) 应包含一个 32 位值,表示小于 FTTI 的超时。看门狗计数器使用可选择的时钟源连续运行,并期望得到定期服务。如果不是,则生成复位触发事件。超时周期、窗口模式和时钟源都是可编程的,但必须在复位后的 128 个总线时钟内进行配置。有关如何解锁和重新配置 WDOG,请参阅 S32K1xx 参考手册。

一般来说,预计 WDOG 有助于检测丢失或显着变慢的时钟。

因此,WDOG 也需要用于检测硬件故障,而不仅仅是检测软件故障。使用 WDOG 检测时钟问题是次要措施,因为存在检查时钟完整性的主要方法(例如,通过时钟监视器)。

S32K1xx 提供硬件支持 (WDOG) 来实现控制流和时间监控方法。如果启用了看门狗窗口模式,则可以实现高效的时间流监控。

假设: [SM_069] 应用软件有责任按照应用程序的要求插入具有所需粒度的控制流检查点。[结束]

由向 WDOG_CNT 寄存器写入两个修复值(A602h、B480h)表示的修复服务序列。写入服务序列会使用超时周期重新加载内部递减计数器。

WDOG 模块具有以下可选时钟源:

• 内部低功耗振荡器 (LPOCLK)

• 内部慢速 IRC 时钟 (SIRC)

• 系统振荡器时钟 (SOSC)

• 总线时钟

5.6.9.1 运行时检查

建议:可以使用 WDOG 实现控制流监控。然而,也可以使用不使用 WDOG 的其他控制流监控方法。使用 WDOG 时,应使能 WDOG,并对其配置寄存器进行硬锁定,以禁止应用软件修改。

5.6.9.2 看门狗的快速测试

在安全关键应用程序中执行应用程序代码之前,您必须测试看门狗是否按预期工作并重置 MCU。为了帮助最大限度地减少复位后应用程序代码的启动延迟,您可以使用看门狗测试功能和更快的时钟作为计数器参考。

看门狗测试的实现在参考手册中有描述。

在启动安全应用程序之前,您应该验证看门狗测试是否已成功执行。

根据应用程序,您可以扩展 WDOG 自检并检查其针对不同时钟源和配置的时间窗口的正确功能。

5.6.10 低功耗周期性中断定时器(LPIT)

5.6.10.1 运行时检查

建议:[SM_107] 当使用 LPIT 模块时,它的使用方式应该是看门狗定时器检测到可能的功能安全相关故障( WDOG)。 [结束]

原理:捕获可能的 LPIT 故障

可以使用 CRC 计算其配置寄存器的校验和,并与预期值进行比较,以验证 LPIT 配置是否正确。

5.6.11 低功耗模式监控

特定条件下的假设: [SM_082] 如果应用程序使用低功耗模式,则需要监控 LP 模式的持续时间。如果系统在指定时间段内没有唤醒,系统将被监控电路复位。 [end]

实施提示:WDOG 可提供时间监控。

基本原理:如果应用程序使用低功耗模式,要克服唤醒和中断输入中的故障。

5.6.12 循环冗余校验 (CRC)

循环冗余校验 (CRC) 减轻 CPU 计算 CRC 校验和的负担。CRC 模块可用于在传输或存储期间检测数据的错误损坏。 CRC 模块提供了实现 16 位或 32 位 CRC 标准所需的可编程多项式和其他参数。一次为 32 位数据计算 16/32 位代码。

5.6.12.1 运行时检查

S32K1xx 配置寄存器的一部分不提供功能安全完整性 IEC 61508 系列和 ISO 26262 要求的高功能安全完整性目标。这与系统故障(例如,应用软件错误地覆盖寄存器)以及随机硬件故障(寄存器中的位翻转)有关。

假设:[SM_070] 每个 FTTI 应至少检查一次安全相关配置寄存器,以验证其内容是否正确。 [结束]

建议:为了检查安全相关配置寄存器的内容,可以使用如下所述的 CRC 检查。如果检查配置寄存器的 CRC 方法不可行,则可以实施替代寄存器检查,例如读取配置寄存器并检查预期值。

实施提示:涉及安全功能的模块的配置寄存器的CRC应离线计算。如果预期寄存器内容的独立来源可用,则可以进行在线 CRC 计算(例如,如果某些寄存器被动态修改)。

在运行时,CRC 模块计算的值需要与离线值相同。为避免内核过载,eDMA 模块可用于支持从检查中的寄存器到 CRC 模块的数据传输。

实现提示:为了验证涉及安全功能的模块的S32K1xx配置寄存器的内容,可以使用CRC模块计算寄存器内容的签名,并将该签名与开发时计算的值进行比较。

或者,可以使用 CPU 代替 CRC 模块来检查配置寄存器的值是否未被修改。但是,使用 CRC 模块更有效。

仅当 CRC 模块用作安全完整性措施或在安全功能内时,应用程序才应包括针对 CRC 模块可能的故障的检测或保护措施。

实施提示:当安全功能处于活动状态(应用程序运行时)时,另一种方法是使用 eDMA 重新初始化与相应 FTTI 中的安全功能相关的模块的配置寄存器的内容。这种方法可能需要额外的措施来检测永久性故障(不是通过重新初始化来解决的)。它还需要针对传输错误采取措施,并忽略某些配置寄存器只能通过模式更改才能更改的事实。

5.6.12.1.1 实施细节

eDMA 和CRC 模块应用于实施这些安全完整性措施以卸载CPU。

注意 注意:仅当这些寄存器不包含任何易失性状态位时,才会以正确的方式计算配置寄存器的签名。

5.6.12.1.1.1 <module>_SWTEST_REGCRC

本文档建议使用以下用于寄存器配置检查的安全完整性函数。根据应用,您可以选择以不同方式检查它们,或者可以根据安全考虑其他外设:

• FLEXTIMERn_SWTEST_REGCRC

读取 FlexTimer 配置寄存器并计算 CRC 校验和。

校验和与预期值进行比较。

• PORT_SWTEST_REGCRC

读取 PORT 的配置寄存器并计算 CRC 校验和。

校验和与预期值进行比较。

• ADCn_SWTEST_REGCRC

读取ADC 配置寄存器并计算CRC 校验和。

校验和与预期值进行比较。

• PDBn_SWTEST_REGCRC

读取PDB 配置寄存器并计算CRC 校验和。

校验和与预期值进行比较。

• LPIT_SWTEST_REGCRC

读取LPIT_SWTEST_REGCRC 配置寄存器并计算CRC 校验和。

校验和与预期值进行比较。

5.6.13 错误报告路径测试

ECC 错误可以注入 SRAM 以检查此类错误的报告。

例如,由中子或 α 粒子或单元之间的短路引起的多单元故障可能会导致 ECC 保护字中的三个或更多位被破坏。因此,可用性可能会降低,或者 ECC 逻辑可能会执行标记为单位校正的附加数据损坏。这在 S32K1xx 的设计中通过使用位加扰(列多路复用)来防止,这会导致 RAM 阵列的物理相邻列不包含相同逻辑字的位,而是相邻逻辑字的相同位。因此,信息在逻辑上分布在多个字中,导致每个字中仅出现一位错误,ECC 可以正确纠正这些错误(有关每个存储器的列多路复用因子的存储,请参见 ECC)。

5.7 外围设备

以下部分包含有关如何测试外围设备以及安全系统开发人员如何选择是否实施的建议。

5.7.1 通信

安全相关应用中使用的任何通信外围设备都应使用适当的安全软件协议(例如,容错通信层,FTCOM)。

建议:[SM_051] 建议通过 CAN 接口进行的通信由容错通信协议保护。 [结束]

CAN 没有除其协议规范中包含的安全机制之外的其他安全机制。应用软件或操作系统需要为这些模块提供安全措施以满足安全要求。

5.7.1.1 系统资源的多样性和冗余通信

集成的 LPSPI 和 FlexIO 通信控制器的部分本身不能提供功能安全完整性 IEC 61508 系列和 ISO 26262 对高功能安全完整性目标的要求。由于这些通信协议通常处理复杂度较低的从通信节点,因此容错通信协议中描述的更高级别的功能安全协议可能不可行。因此,可能需要适当的通信信道冗余。通信控制器的多个实例可用于建立单个故障鲁棒通信链路。

建议:如果通过以下接口进行通信是安全功能的一部分,则应使用硬件通信控制器的冗余实例,最好使用不同的数据编码(例如,反转):

• 低功耗 SPI (LPSPI)

• FlexIO

没有LSPI 和 FlexIO 的特殊功能安全机制,协议规范中包含的内容除外。系统级通信架构需要在模块的接口上提供功能安全机制,以满足功能安全要求。

FLexIO 是一个高度可配置的模块,提供广泛的功能,包括模拟各种通信协议(UART、i2C、SPI、I2S 和 PWM/波形生成)。如果配置为作为上述模块之一工作,则为该模块提供硬件冗余。例如,FlexIO 配置为 UART,并且它们都连接到传感器的发送引脚。然后,UART 和 FlexIO 的 UART 应该从传感器接收到相同的数据。比较数据可以检测到 UART 模块的故障。

5.7.1.2 容错通信协议

集成 LPUART (LIN) 和 FlexCAN 通信通道的一部分不能独立地提供 IEC 61508 和 ISO 26262 对高功能安全相关应用所要求的功能安全完整性。

如果通过以下接口进行通信是功能安全功能的一部分,则需要符合 IEC 61784-3 或 IEC 62280 系列的硬件通信通道的软件接口:

• FlexCAN 通信控制器

• 低功耗通用异步接收器/发送器 (LPUART)

FlexCAN 和 LPUART 除了 SRAM 阵列的 ECC 保护及其协议规范中包含的内容外,没有特定的功能安全机制。应用软件、中间件软件或操作系统需要在IP模块的接口上提供功能安全机制,以满足功能安全要求。

典型的机制是:

• 序列编号来检测消息重复、删除、插入和重新排序

• 确认机制或时域复用来检测消息延迟或丢失

• 发送方识别来检测伪装

LPUART 发送和接收路径可以通过使用环路模式或单线模式,其中发射器输出在内部连接到接收器输入。

由于“黑色通道”通常包括物理层(例如,通信线路驱动器、电线、连接器),因此功能安全软件协议层是从消息源到消息目的地的端到端功能安全机制。

可能需要适当的功能安全软件协议层(例如,容错通信层、FTCOM、CANopen 安全协议)来确保通信过程的故障性能。软件协议层根据 IEC 61784-3 或 IEC 62280 系列(所谓的“黑通道”)实现与硬件通信通道的软件接口。

提高 CAN 功能安全完整性的另一种方法可能是使用 FlexCAN 通道的多个实例并使用适当的协议来冗余通信数据(例如,使用 CANopen 安全协议)。这种方法使用不同的通信控制器来通信冗余数据(例如,一个消息有效负载反转,另一个消息有效负载未反转)。 CRC 模块或 CSEc 可用于保护 CAN 或以太网的有效负载数据。

由于有限的带宽和 LIN 的点对点通信架构,可能只需要一个简化的功能安全协议层。

5.7.2 I/O 功能

功能安全相关外设的完整性主要通过应用层措施来保证(例如,将一个传感器连接到不同的I/O模块,通过传感器融合验证传感器等)。

假设以某种方式冗余使用与功能安全相关的外围设备。可以使用不同的方法,例如,通过实现复制输入(例如,将一个传感器连接到两个 LSPI,或者甚至将测量相同数量的两个传感器连接到两个 ADC)或通过交叉检查一些 I/O 操作与不同的操作(例如,使用不同数量的传感器值来检查有效性)。此外,如果从传感器传输的数据包含校验和形式的冗余信息,则智能自检传感器也是可能的。优选地,复制的模块使用不同的编码样式(例如,在电压域中反转或对冗余通道使用电压和时域编码)来生成或接收复制数据。安全系统开发人员可以选择最适合他们需求的方法。

建议:[SM_133] I/O 模块冗余操作的比较是应用软件的责任,因为没有为此提供硬件机制。[end]

实施提示:可能的措施可以在每个冗余 I/O 通道内使用不同的编码方案(例如,反相信号、不同的时间段)。

实施提示:可能的措施可能是使用不同的复制外设来实施多个独立和不同的通道。

5.7.2.1 数字输入

特定条件下的假设:[SM_137] 当安全功能使用数字输入时,必须实施系统级功能安全机制以实现所需的功能安全完整性。[结束]

5.7.2.1.1 硬件

实现提示:功能安全数字输入可能需要冗余采集。为降低 CMF 的风险,冗余通道不得使用彼此相邻的 GPIO(请参阅相关故障的原因)。

• 数字输入的双读操作由 PORT 单元的两个通用输入 (GPI) 实现。两次读取(例如,从两个 GPIO 读取)之间的比较(通过软件)检测到错误(请参见图 5-2)。

• 双读PWM 输入是通过将两个模块用作两个通道来实现的。功能安全完整性是通过双重读取和软件比较来实现的。一个通道由 FlexTimer_0 提供,另一个由 FlexTimer_1 提供。读取 PWM 输入是指与信号转换(上升或下降)相关的任何输入读取。这也可能包括信号为高、低或两者兼有的时间(见图 5-2)。

对于双读的每个信号,PORT 可以提供额外的通道来支持每个信号的基于中断的读取(见图 5-3)。

实施提示:如果通过对特定应用的单个采集进行合理性检查可以获得足够的诊断覆盖率,则该检查可以代替冗余采集。

5.7.2.1.2 软件

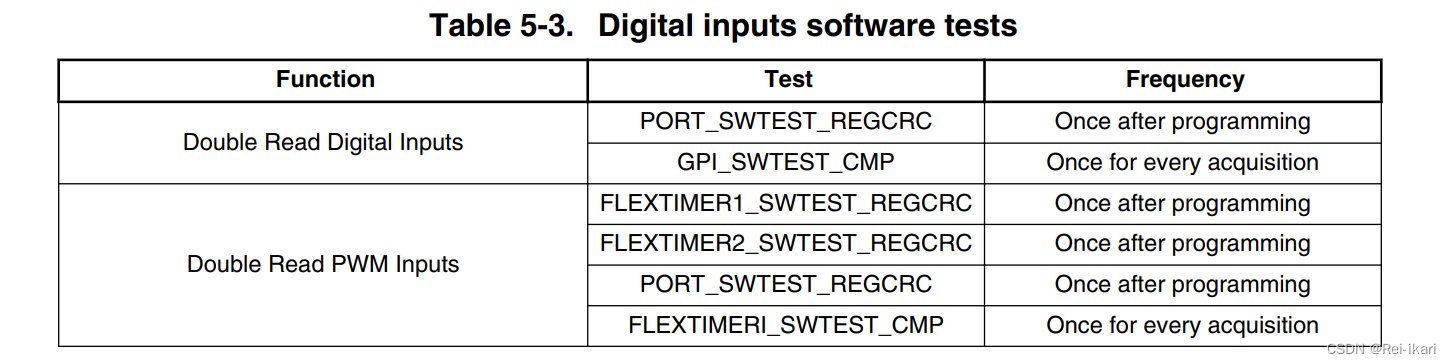

用于功能安全目的的数字输入假定为冗余输入,如本节所述。下表列出了“功能”栏中输入的两个元素安全功能、“测试”栏中相应的安全完整性功能及其执行频率。在“频率”列中可以找到具有足够诊断覆盖率的替代解决方案。

5.7.2.1.2.1 双读数字输入

原理:检查所使用的两个 I/O 的配置是否与预期的配置相符,以减少由错误配置的 I/O 引起 CMF 的可能性,并检查两个输入读取的值相似。

实施提示:功能安全完整性是通过处理功能的重复读取和软件比较来实现的。应用程序可以实现测试 PORT_SWTEST_REGCRC 和 GPI_SWTEST_CMP。

5.7.2.1.2.1.1 实施细节

唯一可用于安全功能的硬件元件是通用输入/输出 (GPIO)。

实现提示:每个不专用于单一功能的 I/O 都可以配置为 GPIO。专用于 ADC 的 I/O 是此规则的一个例外,因为它们只能配置为输入。

注意 注意:冗余 GPIO 的选择方式应确保它们的信号不相邻,这有助于将 CMF 的可能性降至最低。

5.7.2.1.2.1.2 PORT_SWTEST_REGCRC

关于<module>_SWTEST_REGCRC 函数的实现细节,请参考循环冗余校验(CRC)。

5.7.2.1.2.1.3 GPI_SWTEST_CMP

该软件测试用于执行独立通道执行的双读之间的比较。它按顺序读取输出。这允许使用任何 GPIO,但如果输入状态在读取第一个和第二个输入之间发生变化,则可能导致错误结果。

5.7.2.1.2.2 双读 PWM 输入

这种方法使用两个 FlexTimer 并行读取两个 PWM 输入,然后比较结果。

基本原理:检查此安全功能使用的模块配置是否与预期配置相比较,并验证两组读取数据是否相关。

实施提示:应用程序可以实施的软件测试是:

• FLEXTIMER1_SWTEST_REGCRC

• FLEXTIMER0_SWTEST_REGCRC

• PORT_SWTEST_REGCRC

此外,应用程序应将双重读取与以下测试的实施进行比较:

• FLEXTIMERI_SWTEST_CMP。

PORT模块可以配置为提供输入GPIO的配置和输入方向。

5.7.2.1.2.2.1 实施细节

理由:降低由于共享资源而导致级联故障的风险。

实施提示:以下硬件元件应用于安全功能:

• FlexTimer_1 通道

• FlexTimer_0 通道

系统集成商可以从 FlexTimer_1 模块中选择一个通道,从 FlexTimer_0 中选择另一个通道。

5.7.2.1.2.2.2 FLEXTIMERx_SWTEST_REGCRC 和 PORT_SWTEST_REGCRC

这些函数检查所有相关模块的正确配置。请参阅循环冗余校验 (CRC) 以了解 <module>_SWTEST_REGCRC 函数的实现。

5.7.2.1.2.2.3 FLEXTIMERI_SWTEST_CMP

该测试用于执行由不同 FlexTimer 的两个通道执行的 PWM 输入的双重读取之间的比较。由于异步输入信号的不同捕获,比较可以考虑可能的近似。

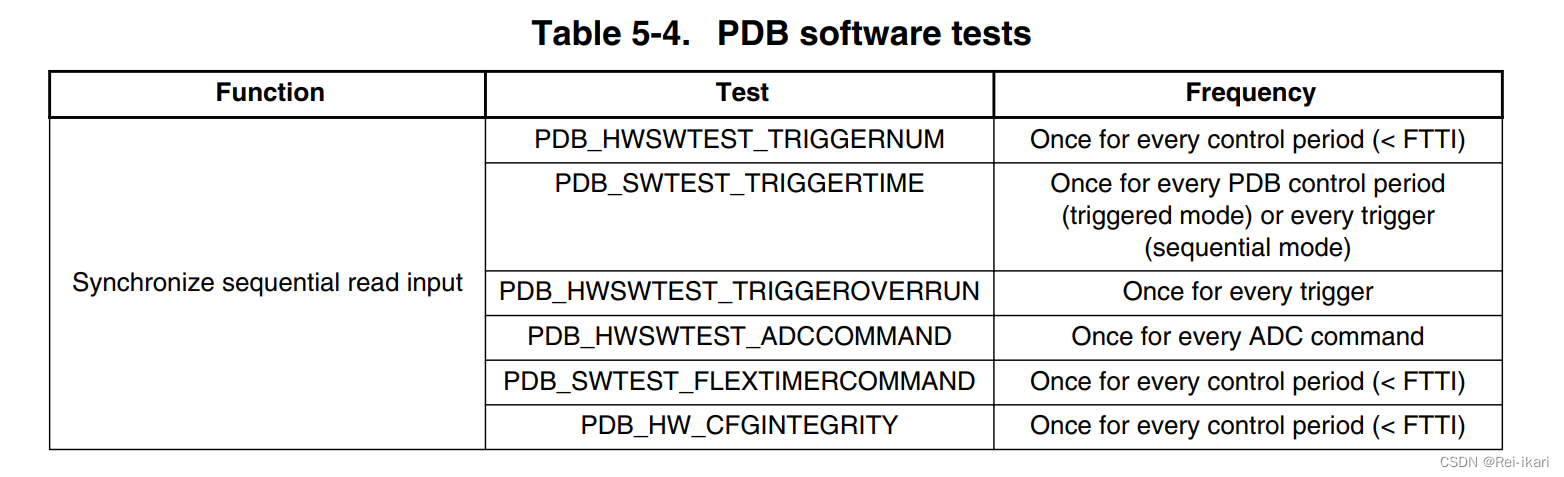

5.7.2.1.2.3 同步顺序读输入

同步顺序读输入由PDB实现,根据触发方式或顺序方式产生事件触发。如果需要将某些输入的读取与某些事件同步,则可以使用 PDB。在应用程序级别实施的以下硬件机制和软件安全完整性措施的组合提供了各自的功能安全完整性:

• PDB_HWSWTEST_TRIGGERNUM

• PDB_SWTEST_TRIGGERTIME

• PDB_HWSWTEST_TRIGGEROVERRUN

• PDB_HWSWTEST_ADCCOMMAND(仅当输入是模拟信号时)

• PDB_SWTEST_FLEXTIMERCOMMAND

• PDB_HW_CFGINTEGRITY

5.7.2.1.2.3.1 硬件元件

同步顺序读输入由 PDB 实现,它根据图 5-4 所示的两种操作模式之一生成触发事件。

PDB 接收来自不同来源的各种传入信号(图 5-4 中的事件 X)。然后处理这些信号以生成触发事件(图 5-4 中的触发 X)。事件可以是每个输入信号的上升沿、下降沿或两个沿。

输出触发可以是脉冲、ADC 命令(或连续命令流)或两者都发送到一个或多个外设(例如,ADC、FlexTimers 等)。

在触发模式下,输入事件也可以是多个信号的组合(逻辑或),它决定了 PDB 计数器的重新加载/重启,并且多达 8 个比较器可用于生成多达 8 个具有给定延迟的输出触发相对于重载信号。在顺序模式下,一个比较器可用于针对八分之一的输入事件(事件 0 用作重新加载事件)生成具有给定延迟的触发。

实施提示:PDB 已配置为使用与输入事件相关的所需时间安排生成输出触发器。

对于每个触发,定义了一组 ADC 命令和要生成的脉冲。

特别是,每个 ADC 命令指定哪个通道由哪个 ADC 获取,如果两个 ADC 执行并发转换或其中只有一个是可操作的,以及结果将存储在哪个内部 FIFO 中。在同时采集的情况下,两个结果使用相同的 FIFO。 ADC 配置为接受来自 PDB 的命令(而不是通过软件提供的命令)。可以为每个触发事件安排多个单次或并发采集。当 ADC 发出先前采集完成的信号时,发送下一个命令。

建议:可以将 PDB 配置为在触发发生时生成中断请求(例如,触发 READ DIGITAL INPUTS)。

5.7.2.1.2.3.2 实施细节 以下硬件元件可用于安全功能:

• PDB

• 一个 FlexTimer 通道

• 另一个 FlexTimer 通道

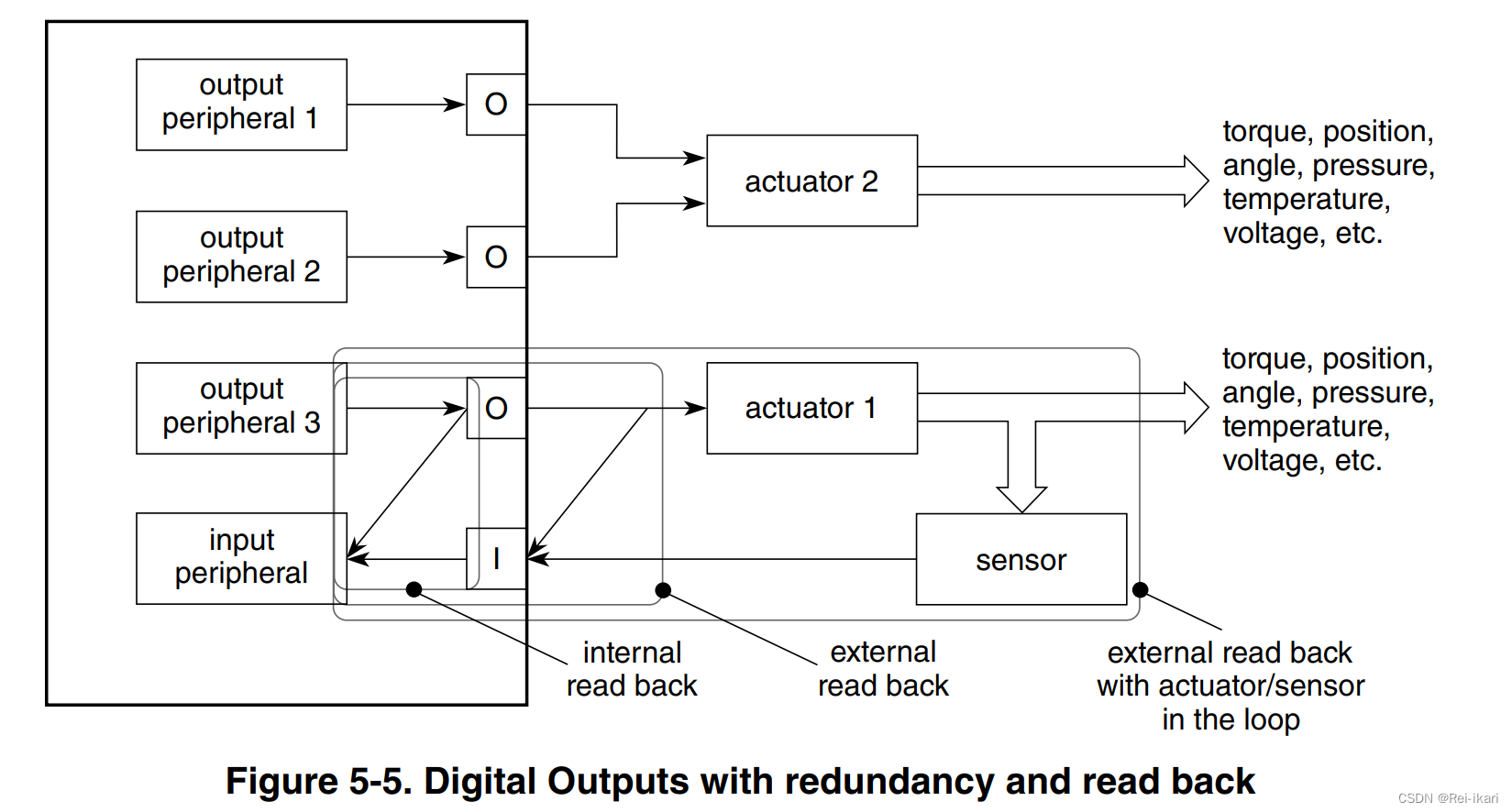

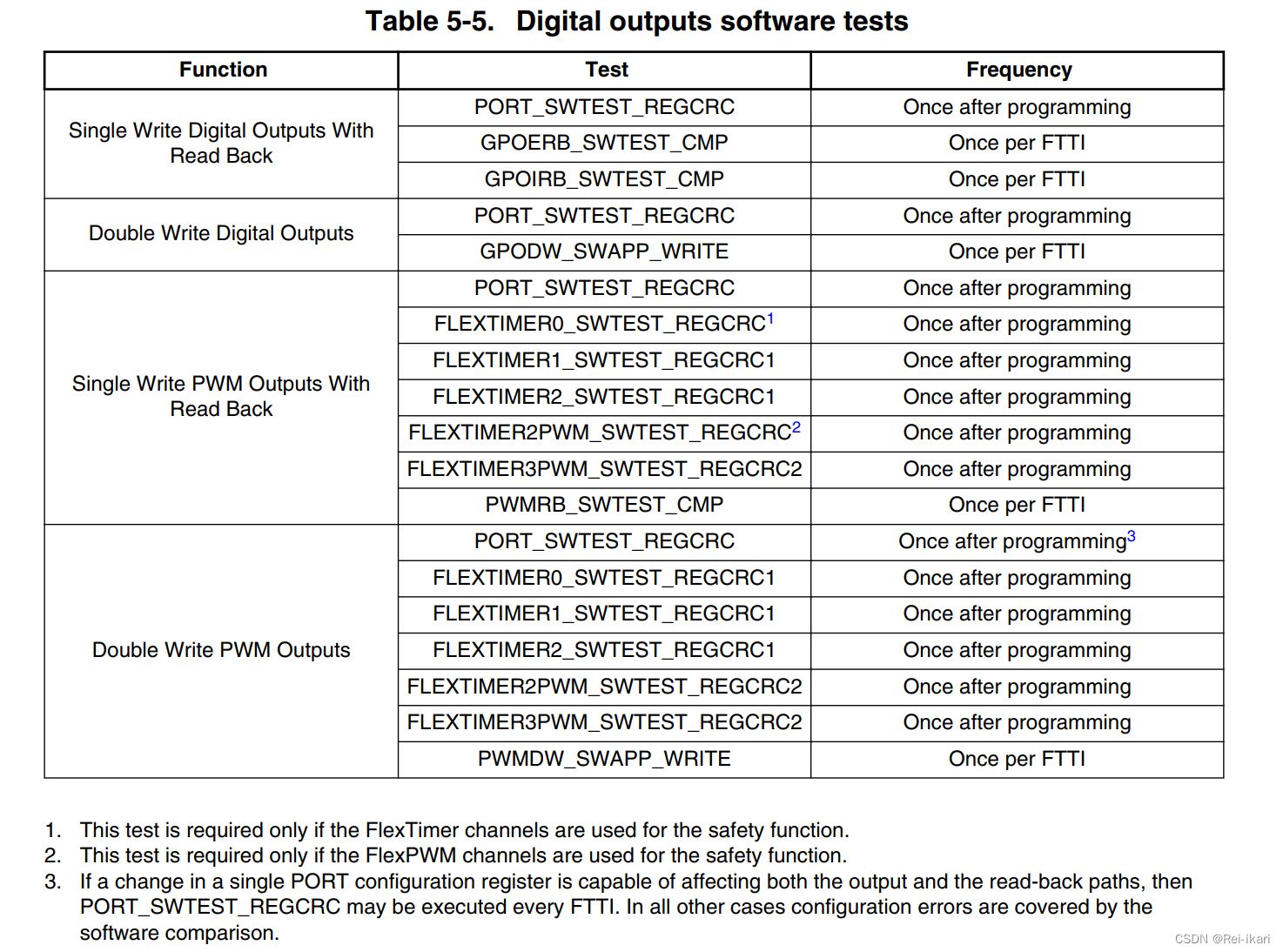

5.7.2.2 数字输出

功能安全数字输出始终假定为冗余写入或回读。在带有回读的单输出的情况下,反馈回路应尽可能大,以覆盖系统级的故障。下图描述了连接到 S32K1xx 的两个(功能安全关键)执行器的连接。

执行器 1 连接到输出外设,例如,电机连接到 PWM 输出(输出外设 3)。输出外设3产生的信号可以输入到输入外设,例如FlexTimer。该措施是为了确认生成的输出信号是正确的。此回读可能是 S32K1xx 内部(内部回读)或外部(外部回读)。与内部回读相比,外部回读涵盖更多类型的故障(例如,损坏的焊线或焊点),但仍不能保证执行器确实按预期运行。这是通过将执行器和传感器包含在回读循环中来实现的。另一种解决方案是冗余输出信号。例如,执行器 2 由两个串联的继电器组成,用于关闭与功能安全相关的电源电压。选择合适的输出连接是系统级 I/O 功能安全概念的一部分。

实施提示:如果通过对特定应用的单个输出通道的合理性检查可以达到足够的诊断覆盖率,则该检查可以替代冗余写入或回读。这个提示是偏离前言中描述的假设的一种特殊情况。

5.7.2.2.1 硬件

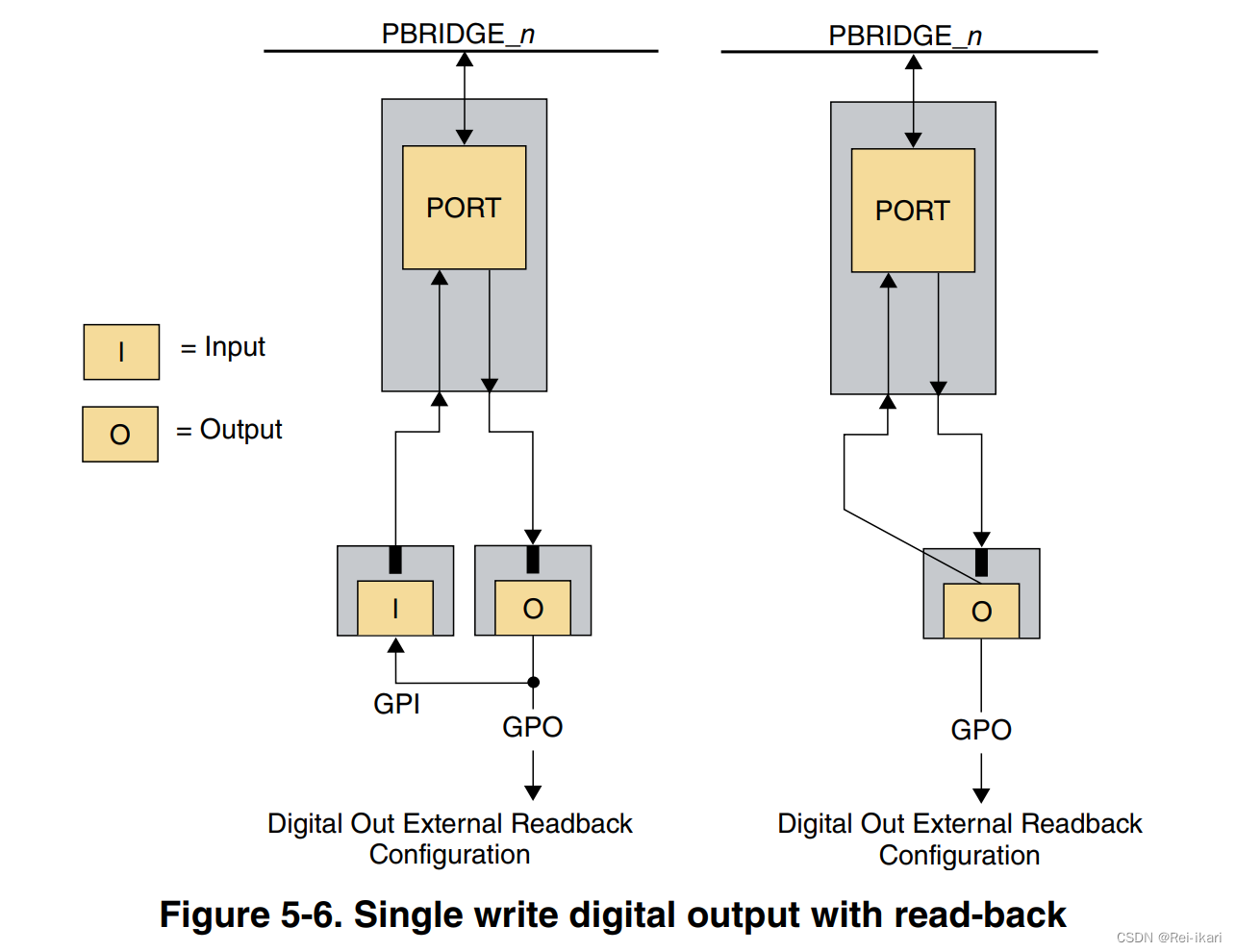

5.7.2.2.1.1 单写数字输出

• 带外部回读的单写数字输出(图 5-6,左):

所需输出值与通过外部读回读回的值之间的比较后台配置完成。写入输出值后,将评估数字输入的状态。

• 带内部回读的单写数字输出(图 5-6,右):

所需输出值与通过内部回读配置回读的值之间的比较。写入输出值后,评估内部回读状态。

• 具有外部回读功能的单次写入 PWM 输出(图 5-7,左):

此过程输出将 FlexTimer_0 的单个通道(FlexTimer_1、FlexTimer_2)提供的 PWM 回读与已写入 FlexTimer_3_PWM 输出通道的外部焊盘的预期值进行比较。

• 带内部回读 3 的单次写入 PWM 输出(图 5-7,右):

此过程输出将 FlexTimer_0 的单个通道(FlexTimer_1、FlexTimer_2)的 PWM 回读与已写入的预期值进行比较FlexTimer_PWM 输出通道。

5.7.2.2.1.2 双写数字输出

• 双写数字输出 PORT

硬件元件用于执行双写数字输出。

• 双写 PWM 输出

• 硬件元件用于执行双写 PWM 输出:

• FlexTimer_0 和 FlexTimer_1

• FlexTimer_1 和 FlexTimer_2

• FlexTimer_2_PWM 和 FlexTimer_3_PWM

5.7.2.2.2 软件

用于功能安全目的的软件数字输出被假定为冗余写入或回读,如本节所述。表 5-5 列出了输出的四个元素安全功能、相应的安全完整性功能及其执行频率。具有足够诊断覆盖率的替代解决方案是可能的。

5.7.2.2.2.1 带回读的单写数字输出

PORT 硬件元件用于执行带回读的单写数字输出(参见图 5-6)。

基本原理:检查写入的数据是否与预期的数据一致

实施提示:回读可以通过外部或内部回读来实现。

正确配置 PORT 元件以提供如下输出写入和焊盘方向:

• 外部回读—— PORT 配置为通过附加焊盘回读信号,并在器件外部执行环回。在此配置中,只有一半的可用数字输出可用作功能安全输出。

• 内部回读——PORT 配置为通过内部读取路径回读填充值。所有专用于数字输入/输出的焊盘都能够使用输入逻辑读取焊盘数字状态。

基本原理:减少因焊盘配置错误导致 CMF 的可能性

实施提示:应用软件在应用程序中集成软件测试 PORT_SWTEST_REGCRC 以检查焊盘的正确配置,并将回读与数字输出写入进行比较。

GPOERB_SWTEST_CMP 可用于外部回读或

GPOIRB_SWTEST_CMP 用于内部回读。

5.7.2.2.2.1.1 实施细节

PORT 硬件元件可用于安全功能。

注意 不专用于单一功能的焊盘可以配置为 GPIO。专用于 ADC 的焊盘是此规则的一个例外,因为它们只能配置为输入。

5.7.2.2.2.1.2 PORT_SWTEST_REGCRC

要实现 <module>_SWTEST_REGCRC 功能,请参阅循环冗余校验 (CRC)。

5.7.2.2.2.1.3 GPOERB_SWTEST_CMP

该软件测试用于执行所需输出值与通过外部回读配置回读的值之间的比较。写入输出值后,测试读取数字输入的状态。

原理:检查读取的数据是否等于写入的数据

实现提示:输出在外部(在系统级别)连接到输入 I/O。将值写入输出信号后,读取输入以检查是否存在正确的输出。

从图 5-5 描述的场景来看,GPOERB_SWTEST_CMP 支持内部回读场景和外部回读场景。 GPOERB_SWTEST_CMP 仅在特定条件下支持在循环场景中使用执行器/传感器进行外部回读。这将取决于传感器作为响应给出的信号类型以及 MCU 是否可以处理它。

5.7.2.2.2.1.4 GPOIRB_SWTEST_CMP

原理:检查读取数据是否等于写入数据。

此软件测试用于执行所需输出值与通过内部回读配置回读的值之间的比较。写入输出值后,测试读取状态。

5.7.2.2.2.2 双写数字输出 PORT

硬件元件用于执行双写数字输出。

基本原理:配置此安全功能使用的焊盘,并减少因焊盘配置不正确而导致 CMF 的可能性

实施提示:端口由应用软件配置,以正确定义所用输出的配置。软件执行双重写入。

基本原理:为了减少因焊盘配置不正确而导致 CMF 的可能性

实现提示:为了实现两个输出通道的完整性,应用程序验证实现 PORT_SWTEST_REGCRC 的 PORT 配置。

基本原理:通过利用冗余写入数字输出

实现提示:应用软件实现由 GPODW_SWAPP_WRITE 定义的双输出写入。

5.7.2.2.2.2.1 实施细节

唯一可用于安全功能的硬件元件是 GPIO。

每个不专用于单一功能的焊盘都可以配置为 GPIO。专用于 ADC 的焊盘是此规则的一个例外,因为它们只能配置为输入。

5.7.2.2.2.2.2 GPODW_SWAPP_WRITE

原理:防止 PORT 中的 SPF 以危险的方式影响执行器控制

实现提示:冗余通道的输出写入可以通过将两个输出写入适当的寄存器和该寄存器来实现可以通过回读来检查。

5.7.2.2.2.3 带回读的单写 PWM 输出

以下元素组合可用于执行带回读的写 PWM 输出:

• FlexTimer_0 – FlexTimer_2_PWM

• FlexTimer_1 – FlexTimer_3_PWM

• FlexTimer_2 – FlexTimer_2_PWM

这些单元应配置为实现一个 PWM 输出通道和(通过内部回读)FlexTimer_0 输入 PWM 通道。 PORT 应配置为定义所使用的输出焊盘的配置。软件先执行写操作,然后执行读操作。为了实现两个输出通道的完整性,应用程序应测试实现 PORT_SWTEST_REGCRC 的 PORT 配置(以减少因焊盘配置不正确而导致 CMF 的可能性)。

基本原理:检查此安全功能使用的模块配置是否符合预期配置。

实施提示:FlexTimer 的单通道与 FlexTimer_2_PWM 不同输出的内部回读的多路复用一起使用。回读路径限制为六个信号,FlexTimer_2_PWM 的每个子模块两个。

以下测试验证 FlexTimer 的正确配置:

• FLEXTIMER2PWM_SWTEST_REGCRC

• FLEXTIMER3PWM_TEST_REGCRC

• FLEXTIMER0_SWTEST_REGCRC

• FLEXTIMER1_SWTEST_REGCRC

• FLEXTIMER2_SWTEST_REGCRC

基本原理:检查写入的数据是否符合预期。

实现提示:应用软件写入输出端口,然后通过回读(PWMRB_SWTEST_CMP)比较写入的值。

5.7.2.2.2.3.1 实施细节

以下硬件元素可用于安全功能:

• FlexTimer_0 通道

• FlexTimer_1 通道

• FlexTimer_2 通道

• FlexTimer_2_PWM 通道

• FlexTimer_3_PWM 通道

5.7.2.2.2.3.2 FLEXPWMx_SWTEST_REGCRC 和 FLEXTIMERx_SWTEST_REGCRC

用于实施<module>_SWTEST_REGCRC 函数请参考循环冗余校验(CRC)。

5.7.2.2.2.3.3 PWMRB_SWTEST_CMP

此测试将 FlexTimer_1 (FlexTimer_0) 的单个通道提供的 PWM 回读与已写入 FlexTimer_2_PWM (FlexTimer_3_PWM) 输出通道的预期值进行比较。

对于此测试,FlexTimer_2_PWM 用于生成 PWM 输出,FlexTimer_1 用于回读和验证输出。如果在应用程序中需要,可以使用另一种组合。

5.7.2.2.2.4 双写 PWM 输出

原理:硬件元件 FlexTimer_0、FlexTimer_1、FlexTimer_2、FlexTimer_2_PWM 和 FlexTimer_3_PWM 用于执行双写 PWM 输出。

实施提示:这些单元配置为实施两个独立的 PWM 通道。 PORT 被配置为定义所使用的输出焊盘的配置。软件执行双重写入(参见 PWMDW_SWAPP_WRITE)。

理由:降低由于空间接近而导致的 CCF 风险

实施提示:使用相邻焊盘作为冗余 I/O 会增加 CMF 的可能性。因此,最好使用在 PORT 中不共享相同配置和数据寄存器的 I/O。

基本原理:为减少因焊盘配置不正确而导致 CMF 的可能性

实施提示:为提高两个输出通道的完整性,应用程序应测试实现 PORT_SWTEST_REGCRC 的 PORT 配置。

基本原理:检查此安全功能使用的模块配置是否符合预期配置

实施提示:应用软件应对寄存器配置实施测试:

• FLEXTIMER0_SWTEST_REGCRC(用于 FlexTimer_0)

• FLEXTIMER1_SWTEST_REGCRC(用于 FlexTimer_1)

• FLEXTIMER2_SWTEST_REGCRC(用于 FlexTimer_2)

• FLEXTIMER2PWM_PWM_SWTEST_REGCRC(用于 FlexTimer_2_PWM)

• FLEXTIMER3PWM_SWTEST_REGCRC(用于 FlexTimer_3_PWM)

基本原理:为减少共享电路级联故障的可能性,应使用不同的模块。

实现提示:冗余 PWM 通道的输出写入是通过将新输出值写入两个 PWM 通道来实现的。

5.7.2.2.2.4.1 实施细节

以下硬件元素用于安全功能:

• FlexTimer_0 通道

• FlexTimer_1 通道

• FlexTimer_2 通道

• FlexTimer_2_PWM

• FlexTimer_3_PWM 通道

5.7.2.2.2.4.2 PORT_SWTEST_REGCRC

要实现 <module>_SWTEST_REGCRC 功能,请参阅循环冗余校验 (CRC)。

5.7.2.2.2.4.3 PWMDW_SWAPP_WRITE

如果 PWM 输出的内容发生变化,必须小心,因为输出不能同步更新。因此,在短时间内,两种输出可能不同。

5.7.2.3 模拟输入

5.7.2.3.1 硬件

有两个选项可用于读取模拟输入:

• 单读模拟输入

• 双读模拟输入

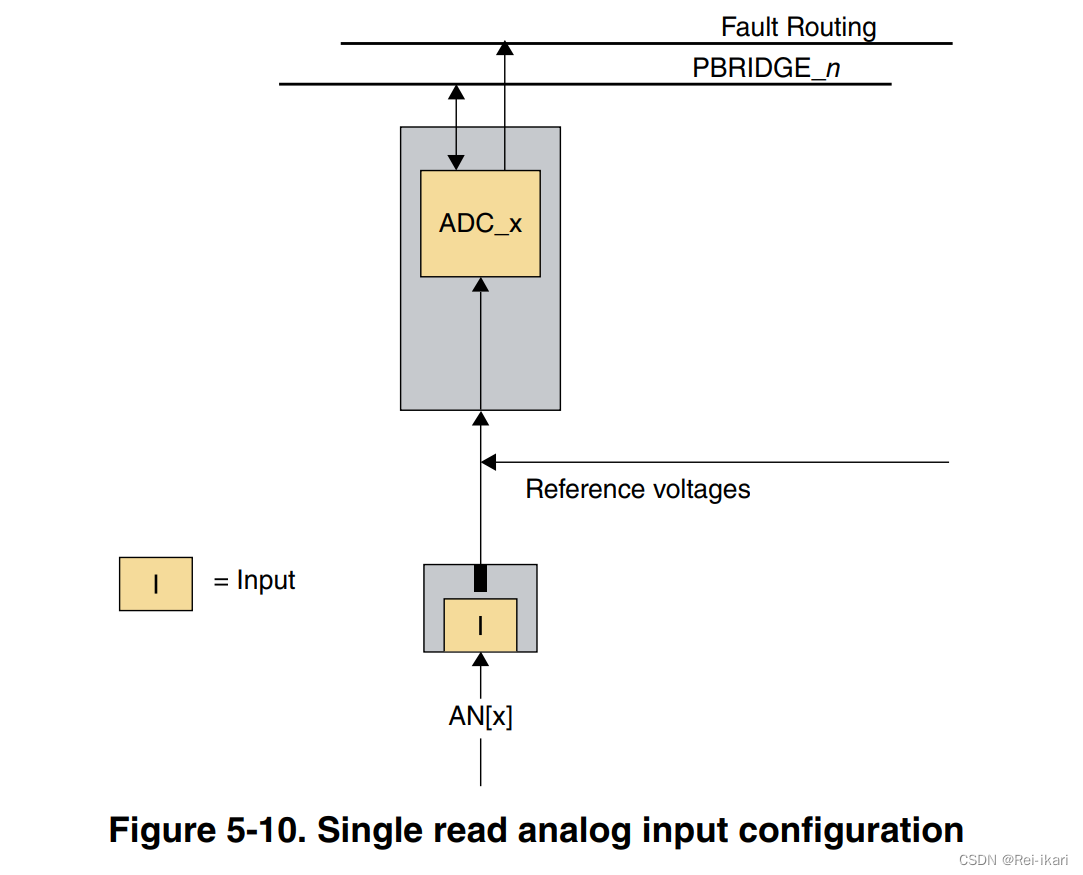

5.7.2.3.1.1 单读模拟输入

单读模拟输入使用单读模拟输入- ADC_0 或 ADC_1 的输入通道,用于获取模拟电压信号(见下图)。

5.7.2.3.1.2 双读模拟输入

双读模拟输入使用两个模拟输入通道来获取复制的模拟输入信号。两个 ADC 单元采集并数字化连接到输入的冗余模拟信号的两个副本。在这种配置中,只有一部分模拟输入可用。结果的比较由系统级应用软件进行(见下图)。

以下是可与双读模拟输入功能一起使用的 S32K14x ADC 通道列表:

• ADC0_SE[4:5] 和 [8:9]

• ADC1_SE[8:9] 和 [14:15]

基本原理:ADC_0和 ADC_1 共享输入通道。在这些共享通道上使用双读可能是 CCF 的来源。

实施提示:一个共享的 ADC 通道不能用于双读模拟输入功能的两个输入。

以通道 ADC0_SE4 和 ADC1_SE14 为例,这两个通道可以独立工作,但也可以硬件交错。在硬件交错模式下,引脚 PTB0 上的信号可以被 ADC0 和 ADC1 采样。交错模式由 SIM_CHIPCTL[ADC_INTERLEAVE_EN] 启用。双读 ADC 输入的可能组合如下:

• 通道 ADC0_SE5 和 ADC1_SE15 在引脚 PTB1 上交错

• 通道 ADC0_SE4 和 ADC1_SE14 在引脚 PTB0 上交错

• 通道 ADC0_SE8 和 ADC1_SE8 在引脚 PTB0 上交错引脚 PTB13

• 通道 ADC0_SE9 和 ADC1_SE9 在引脚 PTB14 上交错

功能安全完整性是通过具有分离的模拟输入通道的复制采集和处理功能的软件比较来实现的(参见下图)。

注意 S32K11x 变体只有一个 ADC。在这种情况下,仅使用两个模拟输入并在 ADC 上连续测量两个输入。这将降低高于 ADC 模拟故障率的引脚故障率。

5.7.2.3.2 软件

用于功能安全目的的模拟输入假定为冗余输入,如本节所述。表 5-6 列出了模拟输入的两个元素安全功能、相应的安全完整性功能及其执行频率。具有足够诊断覆盖率的替代解决方案是可能的。

5.7.2.3.2.1 单次读取模拟输入

为了支持高诊断覆盖率,两个已知的参考电源电压被两个软件测试使用,这两个软件测试将在以下部分(ADC_SWTEST_TEST1 和 ADC_SWTEST_TEST2)中进行描述。

参考电源电压如下:

• VREFH(ADC0/ADC1 高电压参考)

• VREFL(ADC0/ADC1 参考地) PORT 单元配置为正确启用ADC 输入。用于模拟输入的焊盘只能配置为输入。

单读模拟输入可以在应用层使用以下安全完整性功能来实现:

• ADC_SWTEST_TEST1

• ADC_SWTEST_TEST2

• ADC_SWTEST_VALCHK

• ADC0_SWTEST_REGCRC、ADC1_SWTEST_REGCRC

• PORT_SWTEST_REGCRC

• ADC_SWTEST_OVERSAMPLING

5.7.2.3.2.1.1 实施细节

以下 S32K1xx 硬件元件可用于安全完整性功能:

• 模拟输入通道 ADC0_SE[0:3]、ADC0_SE[6: 7] 和 ADC0_SE[10:15]

• ADC0_SE[4:5]、ADC1_SE[8:9] 和 ADC1_SE[14:15] 的模拟输入通道 AN[11:14](共享通道)

• 模拟输入通道 ADC1_SE[ 0:7] 和 ADC1_SE[10:13]

5.7.2.3.2.1.2 PORT_SWTEST_REGCRC

要实现 <module>_SWTEST_REGCRC 功能,请参阅循环冗余校验 (CRC)。

5.7.2.3.2.1.3 ADCn_SWTEST_REGCRC

如果使用 ADC_0,则可以使用 ADC0_SWTEST_REGCRC。如果使用 ADC_1,则可以使用 ADC1_SWTEST_REGCRC。

对于 <module>_SWTEST_REGCRC 函数的实现,请参阅循环冗余校验 (CRC)。

5.7.2.3.2.1.4 ADC_SWTEST_TEST1

检查 ADC 功能是否正确。

基本原理:检测 ADC 转换逻辑可能出现的故障。

实施提示:启用并配置 ADC 内部电源监控功能以对 0 V 和 5 V 的固定内部电压进行采样和转换。然后,将转换结果与相应的预期值进行比较。

5.7.2.3.2.1.5 ADC_SWTEST_TEST2

检查模拟输入路径是否浮动。

基本原理:检测通道多路复用电路的故障。

实施提示:或者,将 ADC 配置为转换两个固定的内部常数值,后跟一个取决于应用的电压值。然后,将转换结果与预期值进行比较。选择一个介于两个固定常数值之间的与应用相关的电压值。在两个方向上执行转换——从低压到高压,以及从高压到低压。

5.7.2.3.2.1.6 ADC_SWTEST_VALCHK

当 ADC 转换由 PDB 触发时,采集的数字样本数据连同有关执行采集的通道的信息一起存储到双队列中。对预期通道的检查提供了控制逻辑和部分队列逻辑的覆盖范围。检查所获取通道的预期序列提供了控制逻辑和部分队列逻辑的覆盖范围。

此软件测试的目标是验证 ADC 以及 PDB(如果使用)的控制和队列逻辑的正确操作。该软件测量的实施方式取决于 ADC 的配置方式(例如,PDB 或 CPU 模式):

• 当 ADC 在 CPU 模式下使用时,采集的值由 ADC_Rn 读取。ADC_SC1n[COCO] 提供有关数据采集的状态信息。应用软件应在每次采集后读取并验证这些字段。

• 当PDB 触发ADC 转换时,还应考虑状态和控制寄存器2 (ADC_SC2) 中的状态位。对预期通道的检查提供了控制逻辑和部分队列逻辑的覆盖范围。

5.7.2.3.2.1.7 ADC_SWTEST_OVERSAMPLING

在单次读取模拟输入期间,可以实施 ADC_SWTEST_OVERSAMPLING 作为对抗随机故障的对策。

ADC_SWTEST_OVERSAMPLING 是时间上的采集冗余。

它是指以明显高于与输入信号相关的奈奎斯特频率的速率对信号进行采样。如果有故障,获取的值将不会关联。此安全完整性测量比较获取的值以检查相关性。

针对随机故障,每次采集都会转换三个连续的模拟值以实现 ADC_SWTEST_OVERSAMPLING。下图显示了模拟信号在不同时间点(A1、A2 和 A3)的采样。每个转换都由一个箭头指示,该箭头通过其长度指示转换后的数字值。第二次采集 (A2 ) 是错误的,因为第一次转换的值与其他两个完全不同。

5.7.2.3.2.2 双读模拟输入

原理:验证此安全功能使用的模块配置是否符合预期。减少因焊盘配置不当而导致 CMF 的可能性。

实施提示:双重读取模拟输入可以在应用程序级别使用以下安全完整性功能来实施:

• ADCx_SWTEST_REGCRC

• PORT_SWTEST_REGCRC

基本原理:验证两组读取数据是否相关。

实施提示:可以使用软件测试 ADC_SWTEST_CMP 来实施双读模拟输入,以比较通道读取。此外,您可以使用 ADC_SWTEST_TEST3 的交错功能来验证两个 ADC 是否将模拟输入转换为相同的数字值。有关详细信息,请参阅 ADC_SWTEST_TEST3。

5.7.2.3.2.2.1 实施细节

以下硬件元素可用于安全功能:

• ADC_0 的模拟输入通道 AN[0:8]

• ADC_1 的模拟输入通道 AN[0:8]

来自不同 ADC 的一个通道可以使用模块,例如,一个来自 ADC0,一个来自 ADC1。

5.7.2.3.2.2.2 PORT_SWTEST_REGCRC

有关<module>_SWTEST_REGCRC 功能的实现,请参见循环冗余校验(CRC)。

5.7.2.3.2.2.3 ADC_SWTEST_CMP

该软件测试用于执行两个ADCn 模块通道的任意组合所执行的双重读取之间的比较。该比较可以考虑可能的转换容差。

5.7.2.3.2.2.4 ADC_SWTEST_TEST3

此软件测试使用交错功能,可用于验证所涉及的 ADC 是否将模拟输入转换为相同的数字值。为了增加覆盖范围,您可以为使用的 ADC 使用不同的时钟源。

5.7.2.4 其他要求

基本原理:检测丢失的 FlexTimer 采集。

实现提示:在 FlexTimer 模块中,可以使用捕获标志(FTM_n_STATUS_[CHnF])。

实施提示:使用故障输入进行全局故障控制和相应的故障条件中断以及 FlexTimer 输入捕捉测试功能。 .

实施提示:

• 当应用程序需要访问 ADC 结果 FIFO 时,32 位读取访问可以验证执行转换的正确通道号。

• 当电机控制周期中断发生时,应检查所有FIFO 空中断标志

• 在FlexTimer 模块中,捕捉标志应用于检测丢失的FlexTimer 采集。

• 如果ADC 模拟看门狗功能用于功能安全相关信号,则两个模拟看门狗通道应监控同一信号。

5.7.3 PBRIDGE 保护

PBRIDGE 访问保护可用于限制对各个外围模块的读写访问,并根据主设备的访问属性限制访问。

• 主权限级别——与每个主设备关联的访问权限级别是可配置的。每个主机都可以配置为可信任的读写访问。

• 外设访问级别——每个平台上和平台外外设的访问级别是可配置的。外设可以配置为要求访问外设的主设备具有主管访问属性。此外,如果启用了外设写保护,则会终止对外设的写访问。

外设还可以配置为阻止来自不受信任的主机的访问。

建议:使用应用软件,定期检查连接到PBRIDGE的模块的配置寄存器(10多个寄存器)的内容,以帮助检测PBRIDGE中的故障。

5.7.3.1 初始检查和配置

应用软件应配置PBRIDGE,为每个需要访问保护的从模块定义访问权限。

应用软件应配置 PBRIDGE 以防止除内核之外的所有主设备对 RCM 地址空间进行写访问。

5.7.4 模数转换器 (ADC)

S32K1xx 的逐次逼近寄存器 (SAR) 模数转换器 (ADC) 的部分不提供功能安全完整性来实现高功能安全完整性目标。因此,需要系统级措施。

5.7.4.1 初始检查和配置

假设在某些条件下: [SM_130] 当 S32K1xx 的模数转换器 (ADC) 用于安全功能时,每个 L-FTTI 必须实施一次合适的系统级功能安全完整性措施. [结束]

基本原理:检查 ADC 模块的完整性以防止出现故障

实施提示: 复位后,但在执行任何安全功能之前,应用软件可以对一个或两个 ADC 模块执行以下软件测试以检测故障:

• ADC_SWTEST_TEST1

• ADC_SWTEST_TEST2

• ADC_SWTEST_TEST3 破坏性复位后需要完成校准。

将 ADC 用于模拟输入功能时,需要进行额外的软件测试(请参阅模拟输入)。

5.7.5 异步唤醒中断控制器(AWIC)/外部 NMI

假设在某些条件下:[SM_126] 如果外部 NMI 和唤醒被用作安全机制,特别是如果在某个时间跨度内唤醒或根本不考虑唤醒安全相关,需要实施相应的系统级措施来检测 AWIC 中的潜在故障。 [结束]

基本原理:测试 AWIC 的外部 NMI 和唤醒事件。

实施提示:为了测试外部 NMI 的 AWIC,应用软件可以在启动期间配置 NMI 以仅导致关键中断,然后触发外部 NMI 并检查关键中断是否发生。

第 6 章 故障率和 FMEDA

6.1 故障率

为了分析和量化 S32K1xx 集成安全架构处理随机硬件故障的有效性,在开发过程中进行了 FMEDA(故障模式影响和诊断分析)的归纳分析方法。 S32K1xx。以下用于推导 S32K1xx 基本故障率的方法用作 FMEDA 的输入:

• 永久性故障(芯片和封装):IEC TR 62380 - 可靠性数据手册 - 电子元件、PCB 和设备可靠性预测的通用模型

•瞬态故障(芯片):JEDEC 标准 JESD89 - 半导体器件中阿尔法粒子和地球宇宙射线引起的软错误的测量和报告

6.2 FMEDA

为了支持将 S32K1xx 集成到安全相关系统中,并支持安全系统开发人员要执行系统级安全分析,可使用以下文档:

• FMEDA - 对 S32K1xx 进行感应分析,支持自定义系统级安全机制,包括针对 ISO 26262(SPFM、LFM 和 PMHF)和 IEC 61508(SFF)生成的安全指标和 β 因子 βIC)

• FMEDA 报告 - 描述 FMEDA 支持的 FMEDA 方法和安全机制,包括故障率的来源,分析过程中的失效模式和假设。

FMEDA 和 FMEDA 报告可根据要求提供。

6.2.1 模块分类

用于计算 ISO 26262(单点故障度量 (SPFM)、潜在故障度量 (LFM) 和随机硬件故障概率度量 (PMHF))和 IEC 61508(安全故障分数 (SFF) 的安全度量) 和βIC 因素) S32K1xx 的模块分类如下:

• MCU 安全功能:所有直接影响MCU 安全功能正常运行的模块。

• 安全机制:检测故障或控制故障以实现或保持安全状态的所有模块。在单个故障的情况下,这些模块不能独立地直接影响安全功能之一的正确运行。

• 外围设备:所有参与I/O 操作的模块。外围模块可通过使用系统级安全措施来限定数据或通过冗余使用模块来使用。资格认证应具有较低的相关失败风险。通常,外围模块安全措施是在系统级软件中实施的。

• 调试功能:所有与安全无关的模块,即它们的任何故障都不会影响安全功能之一的正确运行。

第 7 章 相关故障

7.1 针对相关故障的规定

7.1.1 相关故障的原因

ISO 26262-9 列出了以下相关故障,适用于芯片级别的 S32K1xx:

• 随机硬件故障,例如:

• 可能发生的相关故障影响片上功能及其各自的安全机制

• 环境条件,例如:

• 温度

• EMI

• 公共信号(外部资源)的故障,例如:

• 时钟

• 电源

• 非应用控制信号(用于例如,测试、调试)

• 来自未复制的模块的信号

此外,还提到了以下主题,这些主题超出了本文档的范围,此处不予处理:

• 开发故障:

• 开发故障是通过设计解决的系统故障- 过程

• 制造故障:

• 制造故障通常是通过设计过程和生产测试解决的系统故障

• 安装和维修故障:

• 安装需要在系统级别考虑调整和修复故障

• 特定情况造成的压力:

• 可以在系统级别考虑特定情况。此外,应力的结果(例如,由于电迁移引起的磨损和老化)通常会导致单点故障,并且不被视为相关故障。

7.1.2 针对相关故障的措施 环

7.1.2.1 境条件

7.1.2.1.1 EMI 和 I/O

为了应对数字输入上的噪声,I/O 电路在所有数字输入上提供输入滞后。此外,包括中断和定时器输入在内的数字输入以及 RESET 引脚包含毛刺过滤功能,这些功能在端口控制和中断 (PORT)、FlexTimer 模块 (FTM)、低功耗定时器 (LPTMR) 和重置控制模块 (RCM)。

为了减少数字输出造成的干扰,I/O 电路在适用的情况下提供驱动强度控制。还提供了一个内部弱上拉或下拉结构来定义输入状态。

7.1.2.2 公共信号故障

7.1.2.2.1 时钟

为了覆盖由时钟问题引起的相关故障,实施了用于监督的时钟监视器,在 SCG(系统时钟发生器)中进行了描述。 WDOG(看门狗定时器)也检测时钟系统中的主要故障。

7.1.2.2.2 电源

为了解决由电源问题引起的相关故障,实施了监控模块(参见电源管理控制器 (PMC))。由于软件将不再能够触发外部看门狗(外部看门狗监视器 (EWM)),因此会检测到一些相关故障(例如,断电)。

7.1.3 系统级相关故障避免

建议不要使用相邻的外设输入和输出信号,这些信号是冗余使用的,以减少相关故障。由于内部焊盘位置和外部引脚/焊球位置不一定相互对应,安全系统开发人员可能会考虑以下建议:

• 使用非连续封装球

• 使用非连续硅焊盘

• PCB 上这些信号的非连续路由

假设在某些条件下:[SM_142] 如果系统需要针对相关故障的稳健性,则应避免在相邻焊盘或引脚上放置冗余信号的配置。 [结束]

实施提示:应考虑焊盘位置以及销/球位置。

可以从 S32K1xx 微控制器数据表中提取各个外设的引脚/球分配。以下部分解释了如何实现这一点。

7.1.3.1 I/O pin/ball 配置

两个信号上的两个功能是否相邻,可以通过查看封装的机械图(参见 S32K1xx 数据表)以及封装的球号信息来确定见 S32K1xx 参考手册。

器件焊球的布局和芯片焊盘信号的顺序都需要考虑。封装球的邻接是直截了当的,因为它可以在封装布局中看到。确定裸片上的邻接更加困难。 S32K1xx 参考手册中的信号多路复用和引脚分配章节可用于帮助确定芯片上信号的邻接性。为了帮助避免潜在问题,冗余信号不能位于相邻的球或相邻的芯片焊盘上。避免邻接限制了串扰、信号驱动强度和其他相关问题。

7.1.4 βIC 考虑因素

在 S32K1xx 的开发过程中,通过确保片上功能及其各自的安全机制之间的充分独立性来评估 MCU 对相关故障的敏感性。

对 MCU 执行此操作的一种方法是确定 IEC 61508-2 附录 E 中定义的 β 因子 βIC。 βIC 是根据带有相关评分的问题清单计算得出的。 βIC 越小,片上功能及其各自的安全机制就越不容易受到相关故障的影响。最终的 βIC 估计值不应超过 25%。对于每对片上功能及其各自的安全机制,βIC 会计算多次。

FMEDA 包括 βIC 计算,可根据要求提供。

第 8 章 首字母缩略词和缩略语

8.1 首字母缩略词和缩略语

下表显示了本文档中使用的首字母缩略词和缩略语的简短列表。

表 8-1 首字母缩略词

术语 含义

CCF 共因故障

CMF 共模故障

DC 诊断覆盖率

DED 双错误检测

DPF 双点故障

ECC 纠错码

EDC 错误检测码

FMEDA 故障模式、影响和诊断分析

LF 潜在故障

LFM 潜在故障度量

MCU 微控制器单元

MPF 多点故障

PMHF 随机硬件故障的概率度量

PST 过程安全时间

RF 残余故障

SEooC 安全元件脱离上下文

SEC 单错误纠正

SF 安全故障

SFF 安全故障分数

SIL 安全完整性等级

SM 安全手册

SPF 单点故障

SPFM 单点故障度量

TED 三重错误检测