- 1发票识别+发票查验接口助力企业财务工作高效开展_发票查重接口 api

- 2基于数据可视化的豆瓣图书榜单数据分析_数据可视化图书数据

- 3CTF题目学习记录_ctf新手训练题目网页flag

- 4Redis支持的Java客户端都有哪些?官方推荐用哪个?_49.redis 支持的 java 客户端都有哪些?

- 5Zookeeper 集群搭建过程中常见错误_zookeeper 启动失败,报错 “zookeeper jmx enabled by defaul

- 6vscode 打代码光标特效

- 7通俗理解正交匹配追踪(OMP)算法及MATLAB代码实现_matlab omp算法

- 8[spring] Spring Boot REST API - 项目实现

- 9hexo博客5:更新部署&域名配置_hexo更新文章都要重新部署吗

- 10阿里云下载的apche证书做gitleb证书,_chain.crt和_public.crt什么区别

FPGA 控制 RGMII 接口 PHY芯片基础_rgmii时钟

赞

踩

FPGA 控制 RGMII 接口 PHY芯片基础

今天和大侠简单聊一聊FPGA 控制 RGMII 接口 PHY芯片基础,话不多说,上货。

一、前言

网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽小,可以降低电路成本,在实际项目中应用更广泛。

二、从GMII过度到RGMII

先看看GMII和RGMII主要的接口。

GMII:

发送 gmii_tx_clk gmii_tx_d[7:0] gmii_tx_en gmii_tx_er

接收 gmii_rx_clk gmii_rx_d[7:0] gmii_rx_dv gmii_rx_er

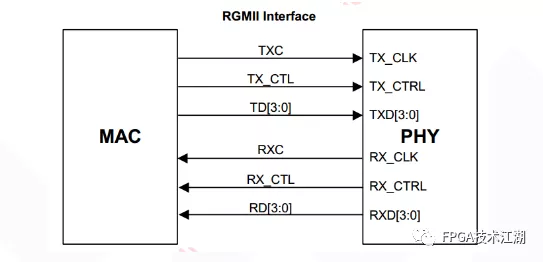

RGMII:

发送 tx_clk tx_d[3:0] tx_ctrl

接收 rx_clk rx_d[3:0] rx_ctrl

为什么接口变少了?首先数据总线从时钟单边沿采样8bit转变为了双边沿采样4bit,从88E1512 Datasheet中时序图可以直观看出这一点。

RGMII中上升沿发送一字节数据的低四位,下降沿发送剩余的高四位数据。接收端时钟双边沿采样,因此125MHZ8bit = 125MHZ4bit*2 = 1000Mbit/s。至于GMII中的数据有效和数据错误指示信号被ctrl信号复用:tx_ctrl在时钟tx_clk上升沿发送是tx_en,在下降沿发送是tx_en ^ tx_er。rx_ctrl在时钟rx_clk上升沿接收是rx_dv,在下降沿接收是rx_en ^ rx_er。综上,RGMII接口引脚数从25个降低到14个。

三、add clock skew

从上边的时序图分析,数据在时钟的边沿变化。因此如果不做额外处理,接收端无法稳定采样。为了解决这一问题,常见的做法是为时钟信号添加延时,使其边沿对准数据总线的稳定区间。可以在控制器端、PCB走线以及PHY芯片内部添加时钟偏移,本文使用最后一种方式实现。

在第三阶段中添加延迟。数据发送方向,FPGA侧的TX_CLK信号不需要额外处理,也就是说FPGA发送与数据边沿对齐的时钟信号。TXD和TX_CLK信号波形如图。

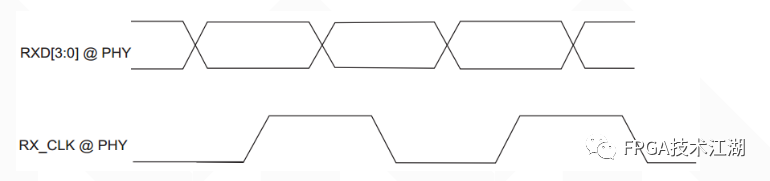

PHY内部会调整TX_CLK,使之能够稳定采样TXD。数据接收方向,由于RX_CLK由PHY提供,PHY芯片直接产生与数据中心对齐的时钟信号。RXD和RX_CLK信号波形如图。

可见,使PHY芯片工作在延迟模式下时,FPGA不需要添加额外的逻辑来保证稳定采样。发送方向直接将数据驱动时钟作为TX_CLK信号发送,接收方向直接利用RX_CLK对RXD信号采样。

四、系统设计方案

本文使用ZYNQ内部的MAC控制器实现数据链路层功能。但由于其接口为GMII,需要用到GMII_to_RGMII IP Core转换接口逻辑。上层网络协议则通过LWIP开源协议栈完成。首先配置ZYNQ IP,使能ENET1并以EMIO方式引出。

系统硬件结构如图:

五、I/O 时序约束

在较高速设计场合下,输入输出接口部分很容易出现数据采样不稳定的现象。这时候就要通过Input delay,output delay约束以及STA来分析设计是否满足稳定采样需求。input/output delay是指数据相对于时钟的延迟,只有设置好上述两个数值,综合工具才会往正确的方向优化并给出合理的时序报告。

FPGA与RGMII接口的PHY芯片之间的时序关系按照数据接口同步和数据采样方式属于源同步DDR采样。input delay约束对应接收方向,时序关系是中心对齐。output delay约束对应发送方向,时序关系是边沿对齐。前者由于很多时候不知道上游器件Tcko信息,会使用示波器测量有效数据窗口来计算。而后者因为是边沿对齐,通过示波器测量抖动窗口并使用skew based method计算。

【QQ交流群】

群号:173560979,进群暗语:FPGA技术江湖粉丝。

多年的FPGA企业开发经验,各种通俗易懂的学习资料以及学习方法,浓厚的交流学习氛围,QQ群目前已有1000多名志同道合的小伙伴,无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有。

【微信交流群】

现微信交流群已建立08群,人数已达数千人,欢迎关注“FPGA技术江湖”微信公众号,可获取进群方式。

完

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

江湖偌大,继续闯荡,愿大侠一切安好,有缘再见!