- 1GPT、Claude、Gemini全系列模型免费白嫖方法_chatgpt镜像

- 2谷粒商城笔记+踩坑(8)——仓库管理_谷粒商城获取spu规格

- 3用于文本去重(相似度计算)的Simhash算法学习及python实现(持续学习中)_simhash算法实例

- 4【leetcode面试经典150题】32.串联所有单词的子串(C++)

- 5【定时同步系列5】Farrow内插器结构原理和MATLAB实现_定时同步内插

- 62024年前端面试真题汇总-3月持续更新中 先收藏慢慢看!(Vue 小程序 css ES6 React 校招大厂真题、高级前端进阶等)_小程序面试题2023

- 7linux mysql dengl_mysql 高性能压力测试

- 8python绘制热力图

- 9探秘Unity ML-StableDiffusion:将AI艺术带入游戏开发的新篇章

- 10各行业都爱用什么编程语言开发?

FPGA_verilog语法整理

赞

踩

FPGA_verilog语法整理

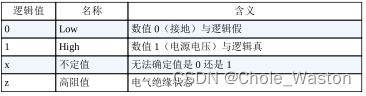

verilog的逻辑值

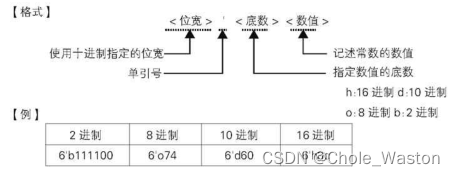

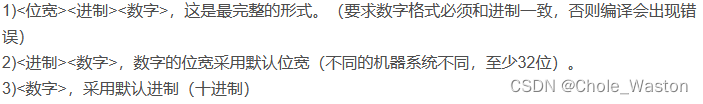

verilog的常数表达

位宽中指定常数的宽度(表示成二进制数的位数),单引号加表示该常数为几进制的底数符号。

二进制底数符号为b,八进制为 o,十进制为d,十六进制为 h

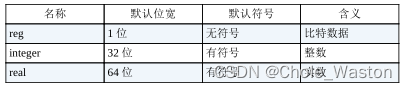

verilog的变量声明

wire与reg

用于声明数据类型

wire型数据常用来表示以assign关键字指定的组合逻辑信号,模块的输入输出端口类型都默认为wire型,wire相当于导线,默认初始值是z。

reg型表示的寄存器类型,用于always模块内被赋值的信号,必须定义为reg型,常用于时序逻辑电路,reg相当于存储单元,默认初始值是x。

对于reg

如果这个条件是时钟的上升沿或下降沿,那么这个硬件模型就是一个触发器;

如果这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;

如果这个条件是赋值语句右侧任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

assign与always

assign(连续赋值)相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,就像把这两个变量连在一起,所以习惯性的当做连线用,比如把一个模块的输出给另一个模块当输入。

always(过程赋值)

1.电平触发,例如always @(a or b or c),a、b、c均为变量,当其中一个发生变化时,下方的语句将被执行。

2.第二种是沿触发,例如always @(posedge clk or negedge rstn),即当时钟处在上升沿或下降沿时,语句被执行。

always @(posedge clk or negedge rstn)//当时钟处在上升沿或下降沿时,语句被执行

- 1

寄存器型变量

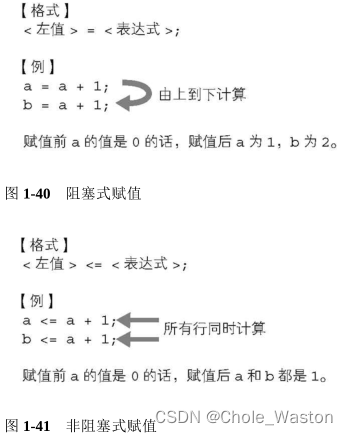

寄存器型变量可以在接下来将要介绍的 always 和 initial 语句中实现过程赋值(Procedural Assignment)。这种方式称为过程赋值。过程赋值分为阻塞式和非阻塞式赋值两种。

寄存器型变量可以在接下来将要介绍的 always 和 initial 语句中实现过程赋值(Procedural Assignment)。这种方式称为过程赋值。过程赋值分为阻塞式和非阻塞式赋值两种。

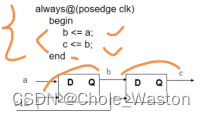

非阻塞赋值–类似于于移位寄存器

阻塞式赋值是一种按照代码顺序进行赋值的方式。在先赋值的代码赋值完成之前阻塞后续代码的赋值,因此得名阻塞式赋值。阻塞式赋值使用 = 运算符。(串行)

非阻塞式赋值中所有代码不会互相阻塞,同时进行赋值。非阻塞式赋值使用 <= 运 算符。(并行)

网络型变量

assign < 网络型变量> = < 表达式>;

< 网络类型> (符号) ( 位宽) < 变量名> = < 表达式>;

- 1

- 2

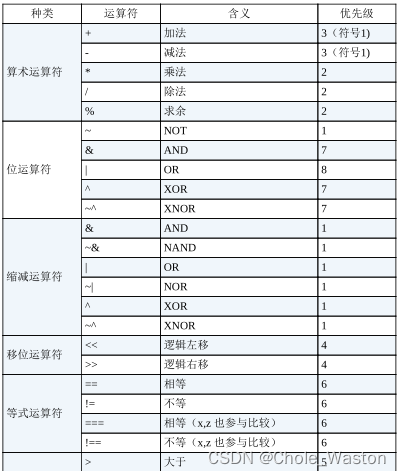

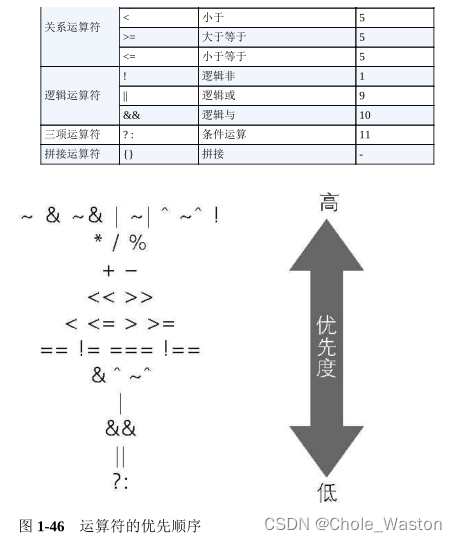

verilog中的运算符

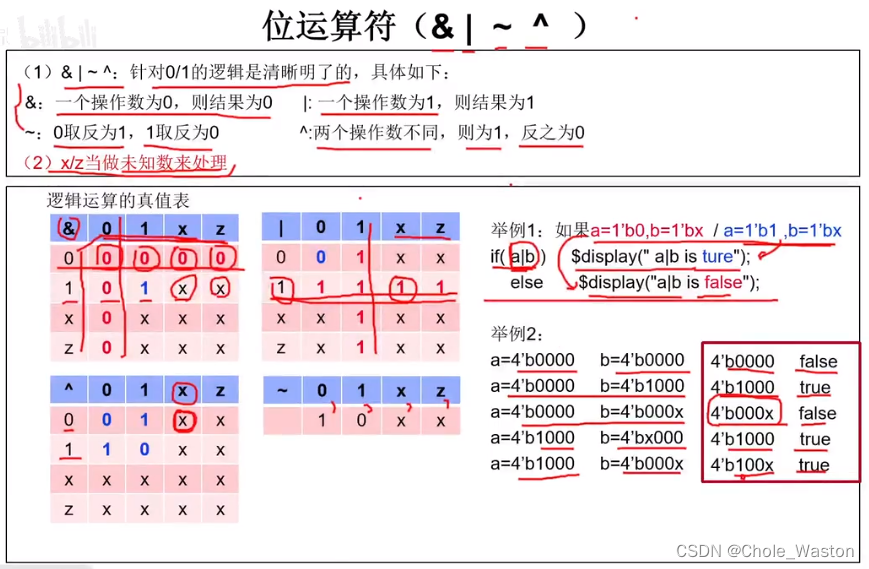

位运算符

逻辑运算符

逻辑语句

条件分支语句if和case

【格式】

if (< 表达式>) < 语句序列>

if (< 表达式>) < 语句序列> else < 语句序列>

【例】

if (a > b) begin

… // 符合a>b 条件的语句

end else if (a == b) begin

… // 符合a==b 条件的语句

end else begin

… // 其他条件(a<b)下的语句

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

case (< 表达式>) < 表达式> : < 语句序列> < 表达式>, < 表达式>, … : < 语句序列> default : < 语句序列> endcase 【例】 case (data[3:0]) 4'h0 : begin … // data[3:0] 为4'h0 时的语句 end 4'h1, 4'h2 : begin … // data[3:0] 为4'h1 或4'h2 时的语句 end default : begin … // 默认语句 end endcase

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

if 和 case 语句可以在 initial 或 always 语句声明的过

程块中使用

循环语句 for 与 while

【格式】

for (< 赋值语句>; < 表达式>; < 赋值语句>) < 语句序列>

【例】

for (i = 0; i < 10; i = i + 1) begin

… // 重复执行10 次

end

- 1

- 2

- 3

- 4

- 5

- 6

【格式】

while (< 表达式>) < 语句序列>

【例】

while (i < 10) begin

… // i 小于10 时重复执行

end

- 1

- 2

- 3

- 4

- 5

- 6

always过程块

always @(< 事件表达式>) < 语句序列>

always #< 常数表达式> < 语句序列>

- 1

- 2

当指定 always 语句中的事件表达式时,所指定的事件触发时执行其中的语句序列。

事件可以是特定信号的变化、信号的上升沿

(posedge)、信号的下降沿(negedge)等。always 语句中如果使用常数,则会在每经过该常数时间便执行一次 always 中的语句序列。

这个功能主要是在仿真时使用。always 过程中可以使用寄存器变量赋值、if、case、for、while 等语句。

使用 always 语句描述组合电路

事件表达式中写入通配符 *。这样一来,任何输入信号变化

时都会执行过程块中的代码。

【格式】

always @(*) begin

… // 组合电路的描述

end

- 1

- 2

- 3

- 4

【例】

module adder (

input wire [31:0] in_0,

input wire [31:0] in_1,

output reg [31:0] out

);

always @(*) begin

out = in_0 + in_1;

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

使用 always 描述时序电路

【格式】

always @(< 边沿> < 信号> [or …]) begin

… // 记述时序电路

end

- 1

- 2

- 3

- 4