- 1llama-factory简介_llama factory

- 2文学-谚语:谚语

- 3NSA的Windows漏洞军火库泄漏:多个零日、利用工具可直接使用

- 42024年最全(一)大数据---Hadoop整体介绍(架构层)----(组件,并发知识体系大全_大数据架构

- 5请做好3年内随时失业的准备?

- 6基于微信小程序的食堂餐厅门店扫码点餐的设计与实现(源码+论文)_v_190_基于微信小程序的微信点餐系统小程序的设计与实现论文

- 7解决Git LFS Smudge过滤器失败的问题 - Python实现_smudge 过滤器 lfs 失败

- 8python编程案例教程答案-Python基础案例教程

- 9三教父神仙打架!AI瓶颈问题的三个解决方案!_如何改进人工智能的泛化瓶颈

- 10springBoot启动提示If you want an embedded database (H2, HSQL or Derby), please put i

DDS信号发生器,FPGA仿真,Verilog语言_fpga的dds信号发生器的仿真

赞

踩

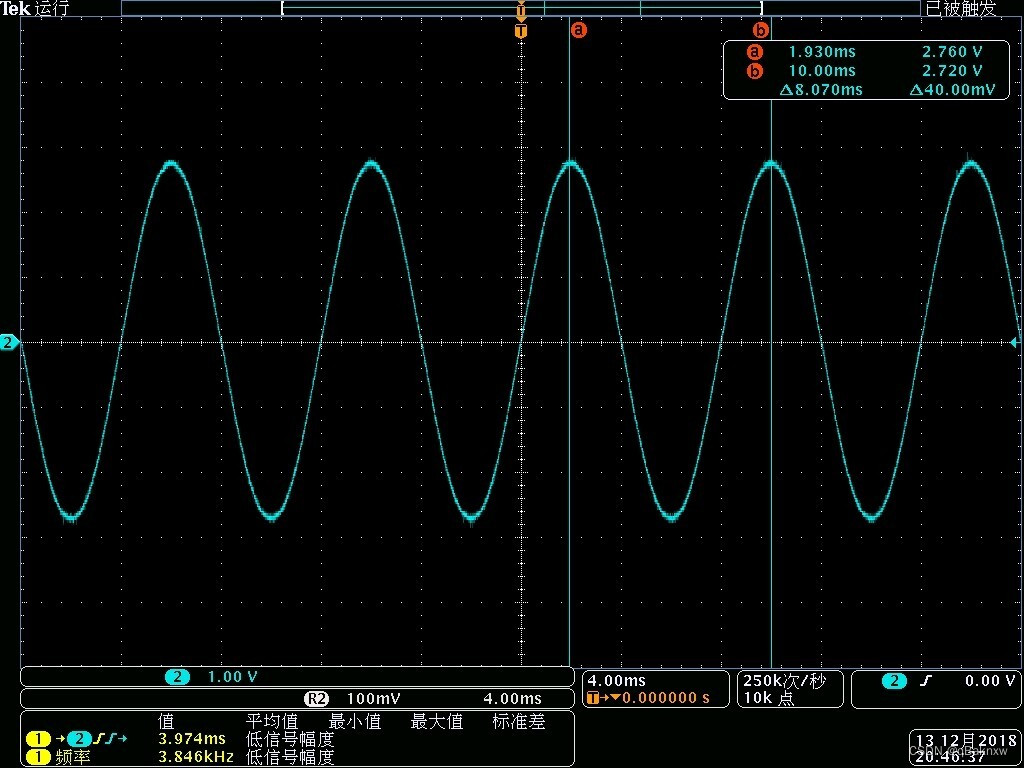

DDS信号发生器,FPGA仿真,Verilog语言。

基于DDS技术的信号发生器波形仿真,可以调节幅度和频率,能产生正弦波方波锯齿波三角波以及四种波形的线性组合。

DDS信号发生器,FPGA仿真,Verilog语言的应用在数字信号处理和通信技术中得到了广泛的应用,特别是在无线电通信系统和雷达信号处理中。本文将探讨基于DDS技术的信号发生器波形仿真,重点关注如何运用FPGA仿真技术以及Verilog语言实现信号发生器的设计。

一、DDS信号发生器的基本原理

DDS技术是指直接数字频率合成技术(Direct Digital Synthesis),它是一种通过数字电路直接产生高精度的波形信号的技术,它以高速数字信号运算为基础,并借助于高速数字信号发生器、高精度数字转换器等器件,通过对数字信号进行运算、滤波、数值控制等过程,实现对模拟信号的产生和处理,从而达到与传统模拟电路相当甚至更高的性能。

DDS信号发生器的基本原理是以参考振荡器为时基,将其经过频率分频后作为数字控制振荡器(NCO)的时钟信号,将NCO的输出通过数字滤波器进行混合、滤波和形状转换,得到需要的波形信号。DDS信号发生器可以调节幅度和频率,能产生正弦波方波锯齿波三角波以及四种波形的线性组合,具有精度高,频率稳定性好,波形稳定、无失真、相位控制能力强等优点。

二、FPGA仿真在DDS信号发生器波形仿真中的应用

FPGA Field Programmable Gate Array 可编程逻辑门阵列,是一种先进的并行处理器,具有高性能和灵活性,可以完成对数字信号的高速处理与计算,并实现复杂的算法,因此在数字信号处理领域中得到了广泛的应用。

在DDS信号发生器波形仿真中,FPGA仿真技术可以实现信号发生器的数字化设计和电路实现。具体的方法是,通过Verilog语言描述DDS信号发生器的逻辑电路实现,然后利用FPGA开发工具对Verilog代码进行综合、布局和时序分析等操作,最终生成相应的电路设计文件,然后通过外部信号输入,控制FPGA实现DDS信号发生器的数字信号处理过程,从而实现波形仿真和调试。

三、Verilog语言在DDS信号发生器波形仿真中的应用

Verilog语言是一种硬件描述语言(Hardware Description Language,HDL),它是一种用于描述数字电路的语言,可以描述数字电路的结构、行为和时序等性能特点。Verilog语言不仅可以用于FPGA、ASIC等数字电路的设计、验证和仿真,还可以用于数字信号处理、通信协议设计等领域。

在DDS信号发生器波形仿真中,Verilog语言可以用于实现DDS信号发生器的逻辑电路设计和验证,具体的方法是,通过Verilog语言描述DDS信号发生器的结构和信号处理过程,然后在仿真工具中对Verilog代码进行调试和验证,最终得到DDS信号发生器的数字电路模型。

四、基于DDS信号发生器的信号处理应用案例

基于DDS信号发生器的应用案例有很多,比如在通信系统中,DDS信号发生器可以用于产生各种复杂的调制信号和解调信号,从而实现通信信号的传输和接收;在雷达信号处理中,DDS信号发生器可以用于产生各种不同频率和相位的载波信号,从而实现雷达信号的处理和图像重构。

例如,在载波相位调制中,采用DDS信号发生器可进行相位控制和频率控制,实现数字调制与解调,降低了模拟信号处理的复杂度,提高了信号质量。

五、总结

本文主要围绕DDS信号发生器、FPGA仿真和Verilog语言展开,探讨了基于DDS技术的信号发生器波形仿真的原理和应用方法,重点关注如何利用FPGA仿真技术和Verilog语言设计和实现数字信号处理电路。同时,本文还介绍了基于DDS信号发生器的信号处理应用案例,表明DDS信号发生器在数字信号处理和通信技术中具有广泛的应用前景。

相关代码,程序地址:http://lanzouw.top/612766592727.html