热门标签

热门文章

- 1深度学习的发展历史与关键技术_深度学习发展历程

- 2基于单片机的RFID门禁系统设计_基于rfid的门禁系统设计

- 3idea 上传代码到 gitee_idea提交代码到gitcode

- 4redis数据库简介、redis下载及安装(win64位)、node操作redis、redis实现短信校验注册接口_redis下载官网

- 52023年中国数据库市场440亿,云数据库四强(阿里、腾讯、亚马逊、华为),本地数据库四强(Oracle、华为、微软、达梦)_idc 关系数据库2023h2

- 6Taro + vue3 小程序封装标题组件_vue 3 封装标题组件

- 7大数据时代的搜索神器:Elasticsearch的发展历程与应用一览

- 8【hadoop】 shell 基本命令_xshell切换hadoop目录命令

- 9使用python+Pyqt5来写一个简易串口调试助手_pyqt5串口助手数据导出功能怎么写

- 10【c语言趣味编程100例】冒泡排序_1024趣味编程题

当前位置: article > 正文

【HDL系列】乘法器(3)——Baugh-Wooley乘法器_booth 乘法与 wooley乘法

作者:知新_RL | 2024-06-12 11:36:37

赞

踩

booth 乘法与 wooley乘法

目录

一、Baugh-Wooley算法

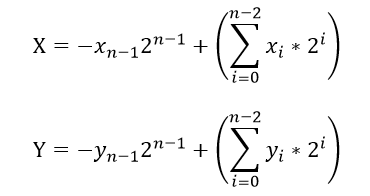

Baugh-Wooley算法是由Baugh和Wooley于1973年提出的二进制补码并行阵列相乘算法。该算法转化为等效并行阵列相加,其中每个部分和为乘数和被乘数比特相与,并且所有的部分和符号位为“+”。将n比特X,Y,乘法结果2n比特的P表示如下:

从上式看出,XY相乘,结果P=XY相当于前两项减去后两项正数,设为A和B.

按顺序用字母表示以上项,即P = C+D-(A+B)。

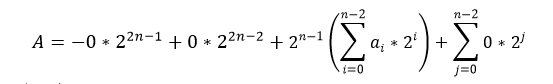

将最后两项A和B,补0扩展表示成2n位,以便在阵列中相加:

其中ai=y(n-1)*xi

A的二进制表示如下:

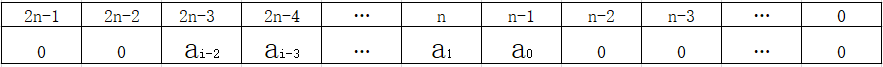

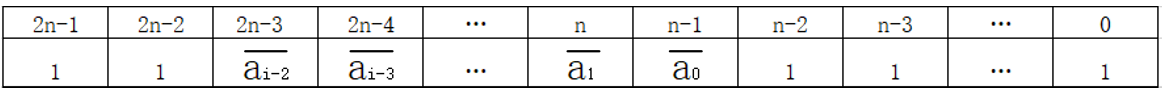

-A,即A的二进制补码,对A“取反加一”,表示如下:

取反:

加一:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/知新_RL/article/detail/707927

推荐阅读

相关标签