- 1大数据毕业设计Hadoop+Spark+Hive租房推荐系统 贝壳租房数据分析 租房爬虫 租房可视化 租房大数据 大数据毕设 机器学习 计算机毕业设计 机器学习 深度学习 人工智能_某省地区租房信息数据本次项目主题是完成hadoop、spark的安装配置,在此基础上使用

- 2使用Ollama+Python本地环境搭建AI大模型_python ollama调用大模型

- 3【JavaScript】66个常用正则表达式!_javascript 常用正则表达式

- 4unity导入模型以及动画_unity导入模型动画

- 5Python语言程序设计

- 6YARN的高可用_yarn高可用

- 7python多线程_为了方式上面情况的发生,就出现了互斥锁(lock) from threading import th

- 8【附源码】计算机毕业设计java校园志愿者服务系统设计与实现

- 9AI降重软件揭秘:免费高效工具大揭秘_ai免费降重

- 10两款 IntelliJ IDEA 的 AI 编程插件_intellij idea ai插件

基于FPGA的交通信号灯设计(一)_fpga交通信号灯控制电路设计

赞

踩

设计任务

- 模拟十字路口交通信号灯的工作过程,利用交通信号灯上的两组红,黄,绿LED发光二极管作为交通信号灯,设计一个交通信号灯控制器。

- 模拟两条公路,一条交通主干道,一条交通支干道,在主干道和支干道的交叉路口上设置红,绿,蓝灯进行交通管理。

- 应用VHDL硬件描述语言编写程序;

- 利用软件仿真出结果;

总体设计

任务和要求:该数字系统完成对十字路口交通信号灯的控制,十字路口由一条东西方向的主干道(简称A道)和南北方向的支干道(简称B道)构成。 十字路口交通灯控制规则为:

(1) 初始状态为4 个方向的红灯全亮,时间1s。

(2) 东西方向绿灯亮,南北方向红灯亮。东西方向通车,时间30s。

(3) 东西方向黄灯亮,南北方向红灯亮,时间5s。

(4) 东西方向红灯亮,南北方向绿灯亮。南北方向通车,时间20s。

(5) 东西方向红灯亮,南,北方向黄灯亮,时间5s。

(6) 返回(2),继续运行。

(7) 如果发生紧急事件,例如救护车,警车通过,则按下单脉冲按钮,使得东,南,西,北四个方向红灯亮。紧急事件结束后,松开单脉冲按钮,将恢复到被打断的状态继续运行。

设计注意事项

-

时序约束:确保交通信号灯的时序满足实际应用的要求。这包括信号灯的切换时间、黄灯持续时间、绿灯和红灯的持续时间等。时序约束的正确定义对于FPGA设计非常重要,可以通过时序分析工具进行验证。

-

状态机设计:使用状态机来管理交通信号灯的状态转换。状态机的设计应考虑到所有可能的状态和状态之间的转换条件,以确保交通信号灯的行为符合预期。

-

灵活性:设计应具有一定的灵活性,以便根据实际情况进行调整。这可能包括考虑不同时间段的交通流量变化,或者根据交通流量感知实时调整信号灯的时序。

-

灯色控制:确保交通信号灯的灯色切换是可靠和准确的。这可能涉及到灯色切换的同步和防抖处理,以及确保在切换时不会出现任何短暂的混乱状态。

-

硬件资源利用:合理利用FPGA的硬件资源,尽量减少资源消耗,以便在同一个FPGA芯片上实现更多的功能模块。

-

异常处理:考虑交通信号灯可能遇到的异常情况,如断电、通信故障等,并设计相应的异常处理机制,以确保系统的可靠性和稳定性。

-

仿真和验证:在部署之前进行充分的仿真和验证工作,以确保设计的正确性和稳定性。这可以通过使用仿真工具和硬件验证平台来实现。

-

节能考虑:考虑到交通信号灯长时间运行的情况,设计应尽量节能,减少功耗,延长设备的使用寿命。

开发板实物图及端口设置

紧急按键按下,时间不走,松开,时间继续计时。

白天与黑夜模式,不按白天模式,按下黑夜模式。

由于板上的序号看不清,所以以实际操作为主

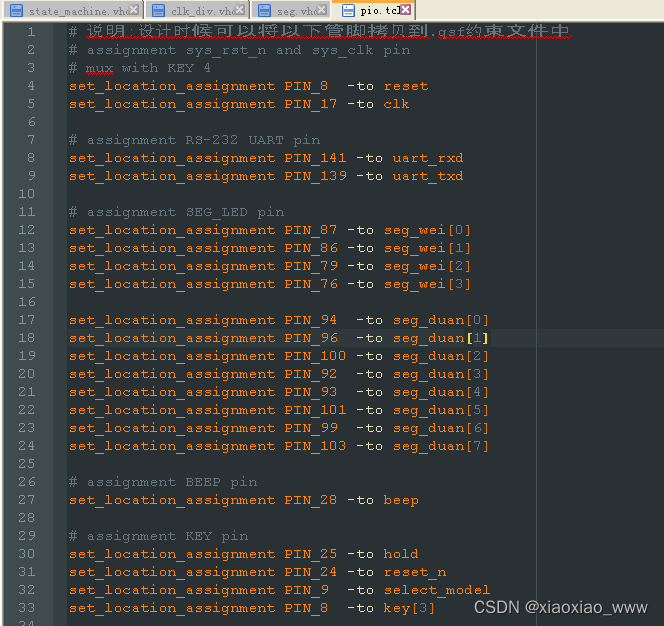

引脚配置如下

如需更改,按上面的更改!

备注:VHDL语言与Veriolg HDL的异同

Verilog HDL 和VHDL相同点:

-

用途:Verilog HDL和VHDL都用于硬件设计和验证。它们可以描述数字电路的结构、行为和时序。

-

抽象级别:两者都支持多种抽象级别,包括结构级、行为级和寄存器传输级等。这使得设计者可以根据需要选择最合适的抽象级别来描述电路。

-

并发性:Verilog HDL和VHDL都支持并发语句,可以描述多个硬件操作同时进行的情况。这使得它们适用于描述复杂的硬件系统。

-

模块化:两种语言都支持模块化设计,可以将电路分解为多个模块,并通过层次化的方式进行组合。这种模块化设计有助于提高设计的可维护性和可重用性。

-

仿真和综合:Verilog HDL和VHDL都可以用于进行仿真和综合。设计者可以使用仿真工具验证设计的正确性,并使用综合工具将设计转换为实际的硬件电路。

Verilog HDL 和VHDL不同点:

-

语法:Verilog HDL的语法更类似于C语言,更加紧凑和直观。VHDL的语法更加结构化和正式,更类似于Ada语言。

-

模块化:在Verilog HDL中,模块的声明和实例化比较简单,使用

module和instantiation进行定义。VHDL对模块的描述更加严谨和详细,使用entity、architecture和component等关键字。 -

并发语言特性:Verilog HDL更倾向于使用非阻塞赋值(non-blocking assignment),适合描述硬件并发行为。VHDL在并发描述方面更加灵活,使用过程(process)和信号赋值(signal assignment)等结构。

-

类型系统:VHDL拥有更为丰富的数据类型系统,包括标量(scalar)、数组(array)、记录(record)等,同时支持用户自定义类型。Verilog HDL的数据类型相对较简单,主要包括基本的整数、浮点数和向量等。