- 102 SVN 与 Git 的优缺点_svn和git的优缺点

- 2国内开源好用商城盘点—PHP_php开源电商平台

- 3随机森林分类模型(python案例代码)

- 4【数据结构】栈和队列的深度探索,从实现到应用详解

- 5macOS Sequoia 15 beta 2 (24A5279h) ISO、IPSW、PKG 下载 (iPhone Mirroring 现已支持)_macos sequoia beta2

- 6【AI大模型】如何在企业环境中部署GPT-3/GPT-4模型_企业部署gpt

- 7目标检测实战(二):YoloV4-Tiny训练、测试、评估完整步骤

- 8如何利用Kali Linux进行网站渗透测试:最常用工具详解_linux漏洞扫描常用的工具以及常用命令

- 9linux数据包注释,Linux网络子系统安全性模块代码详细分析之文件esp4.c中内部函数和核心代码注释...

- 10STM32-ADC_stm32 adc vref

DDR4 SDRAM - 2. 初始化、训练和校准_ddr初始化

赞

踩

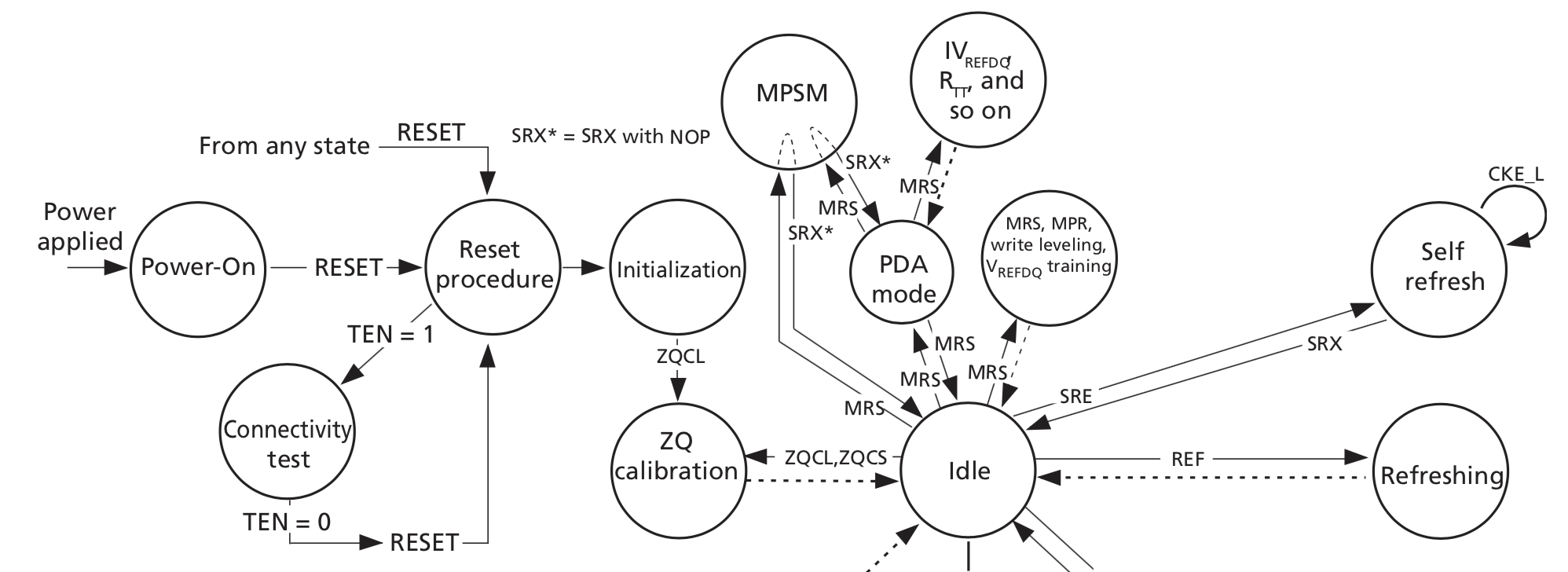

当带有DRAM子系统的设备上电后,在 DRAM 进入运行状态之前会发生许多事情。 以下来自JEDEC规范的状态机显示了DRAM从上电后的各种状态切换。

Figure 1: DDR4状态机

本质上,初始化过程包括 4 个不同的阶段:

• 上电和初始化

• ZQ校准

• Vref DQ 校准

• 读/写训练(又名记忆训练或初始校准)

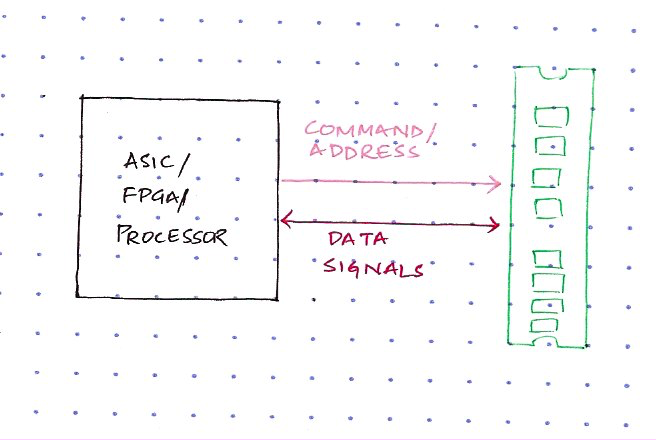

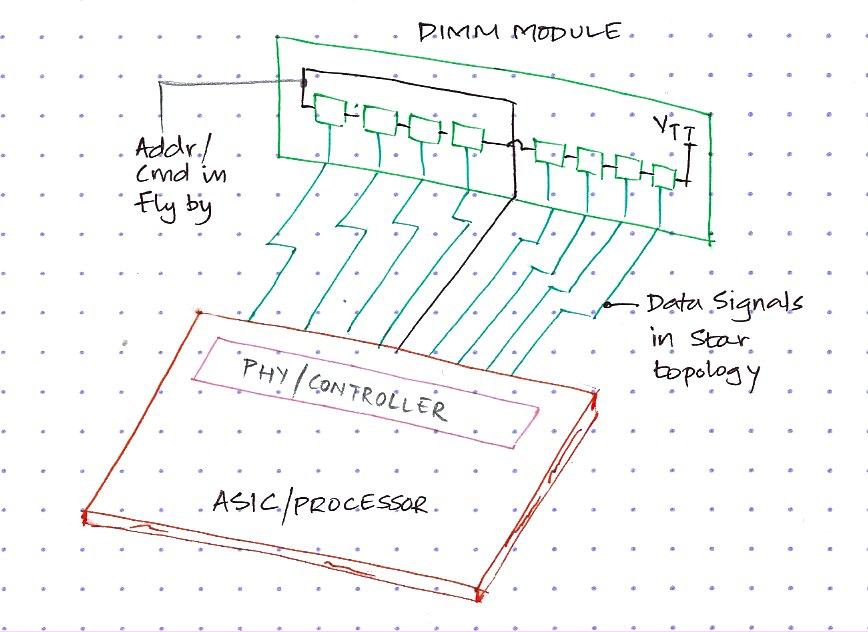

为了更好地理解以下部分,我们假设您有一个如下所示的系统 - 带有 1 个 DIMM 模块的 ASIC/FPGA/处理器。

Figure 2: 系统示例

初始化

Figure 3: 初始化阶段

上电和初始化是一个固定的、定义良好的步骤序列。。通常情况下,当系统上电后,ASIC/FPGA/处理器中的控制器被移出复位,它就会自动执行上电和初始化序列。这是控制器功能的超级简化版本。有关详细信息,请参阅 JESD79-49A规范 中的第 3.3 节。

• 1.为 DRAM 通电

• 2.取消置位 RESET 并激活 ClockEnable CKE

• 3.启用时钟 CK_t/CK_c

• 4.发出 MRS 命令并加载模式寄存器 [模式寄存器按特定顺序加载]

• 5.执行 ZQ 校准 [ZQCL]

• 6.将DRAM带入IDLE状态

此时,DIMM 模块上的 DRAM 了解它们必须以什么频率运行、CAS 延迟 (CL)、CAS 写入延迟 (CWL) 和其他一些时序参数是多少

→ 请查看关于DDR4计时参数的文章,以了解更多关于CL、CWL等的信息...

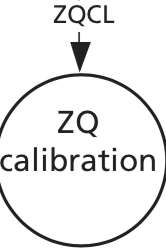

ZQ校准

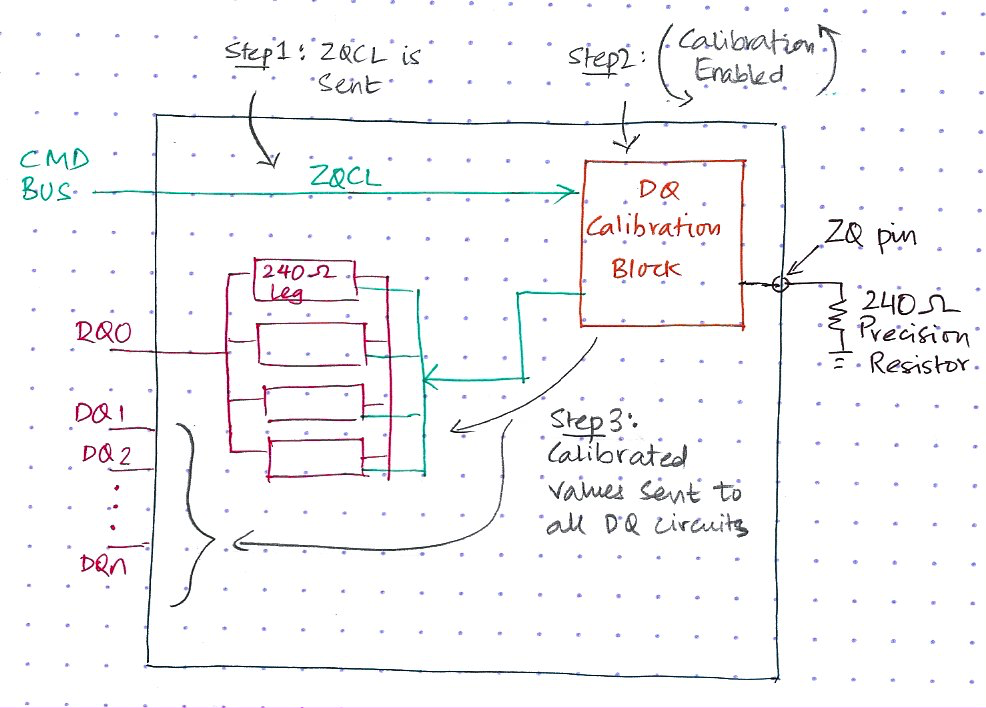

Figure 4: ZQCL

ZQ 校准与数据引脚 [DQ] 有关。要了解 ZQ 校准的作用以及为什么需要它,我们需要首先查看每个 DQ 引脚后面的电路。请记住,DQ 引脚是双向的。它负责在读取期间发回数据并在写入期间接收数据。

Figure 5: DQ 校准块

现在,如果您在 DRAM 内部查看,每个 DQ 引脚后面的电路都由一组并联的 240Ω 电阻支路组成,如图 4 所示。由于 CMOS 器件的性质,这些电阻从来都不是精确的240Ω。这些电阻从来都不是精确的240Ω。

为了将这些电阻精确地调整到 240Ω,每个 DRAM 都有

• 一个称为 DQ 校准控制块的特殊模块和

• 一个 ZQ 引脚,连接了一个外部精度 (+/- 1%) 240Ω 电阻。

这个外部精密电阻器是“参考”,它在所有温度下都保持在 240Ω。当在初始化期间发出 ZQCL 命令时,该 DQ 校准控制块被启用并产生一个调整值。然后将该值复制到每个 DQ 的内部电路。

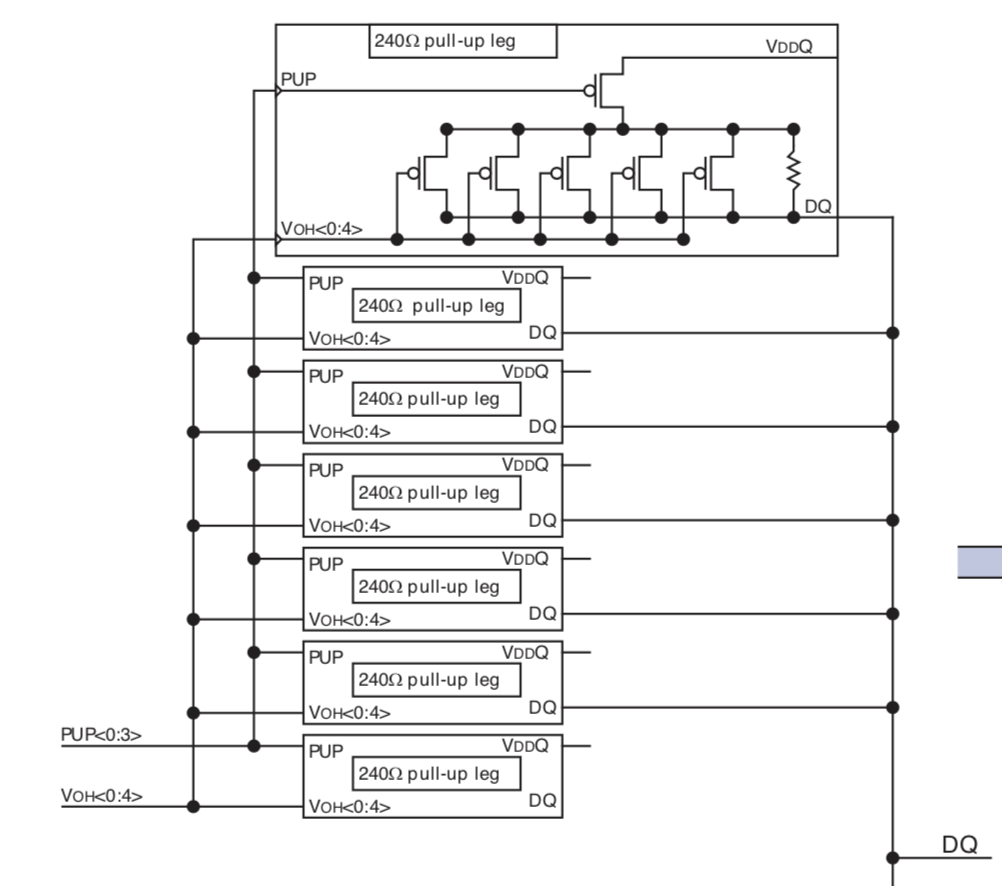

DQ 电路中的 240Ω 电阻器支路是一种称为“多晶硅电阻器”的电阻器,通常略大于 240Ω(多晶硅电阻是一种与 CMOS 技术兼容的电阻)。有一些p沟道器件与该多晶电阻并联,这样它就可以精确地调到240Ω。

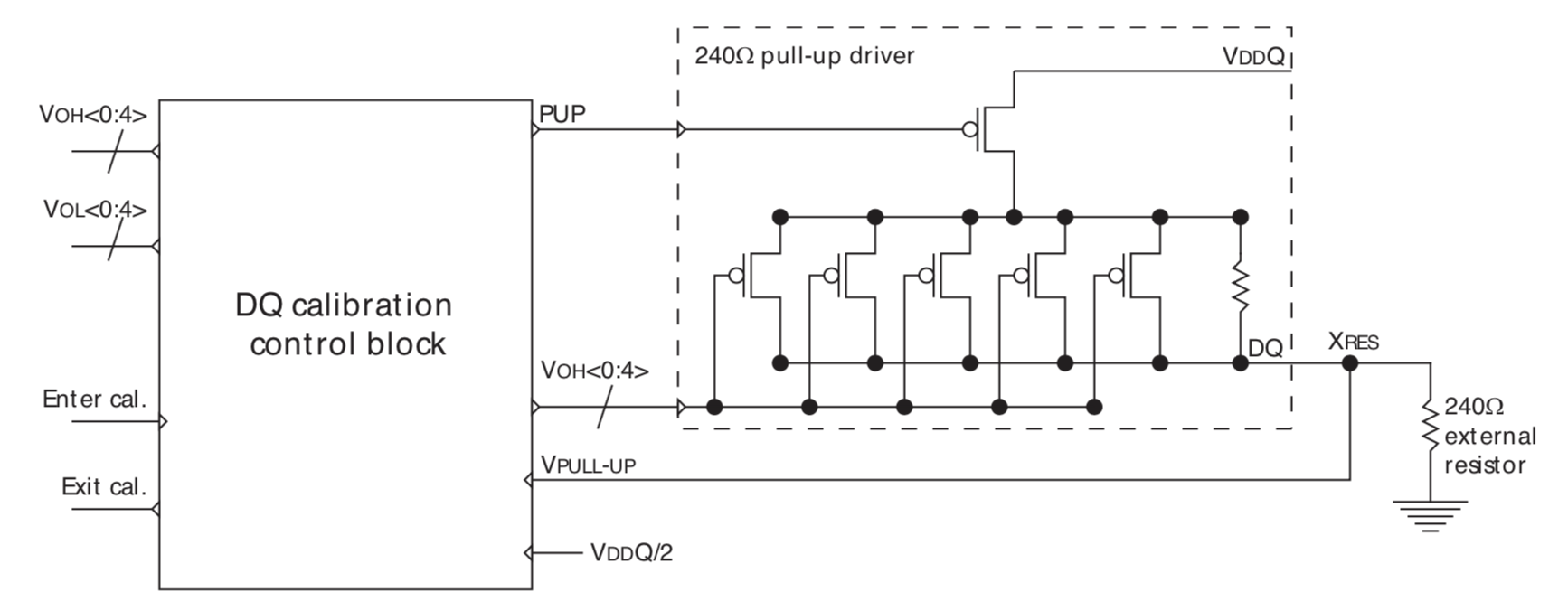

下图放大了 DQ 电路的一个 240Ω 支路,显示了 5 个连接到多晶电阻的 p 沟道器件。这些小晶体管是根据输入 VOH[0:4] 设置的

Figure 6: DQ 驱动器/接收器电路 [来源:Micron datasheet]

现在,连接到 DQ 校准控制块的电路本质上是一个电阻分压电路,其中一个电阻是多晶硅,另一个是精度 240Ω。当在初始化期间发出 ZQCL 命令时,该 DQ 校准控制块被启用,并且 DQ 校准控制块内的内部比较器使用 VOH[0:4] 调谐 p 沟道器件,直到电压恰好为 VDDq/2(经典电阻分压)。此时校准已完成,VOH 值已传输到所有 DQ 引脚。

Figure 7: DQ 校准块 [来源:Micron datasheet]

接下来,你可能会想,为什么DQ引脚首先要有这个240Ω电阻的并联网络!

拥有一组并联的 240Ω 电阻器可以让您调整驱动强度(用于 READ)和终端电阻(用于 WRITE)。每个PCB布局都是不同的,所以需要这种调整能力来改善信号的完整性,最大限度地提高信号的视距,并允许DRAM高速运行。

DRAM的信号驱动强度可以通过设置模式寄存器MR1[2:1]来控制。终端可以分别通过模式寄存器MR1、2和5中的RTT_NOM、RTT_WR和RTT_PARK的组合来控制。

Vref DQ 校准

Figure 7: Vref DQ 校准

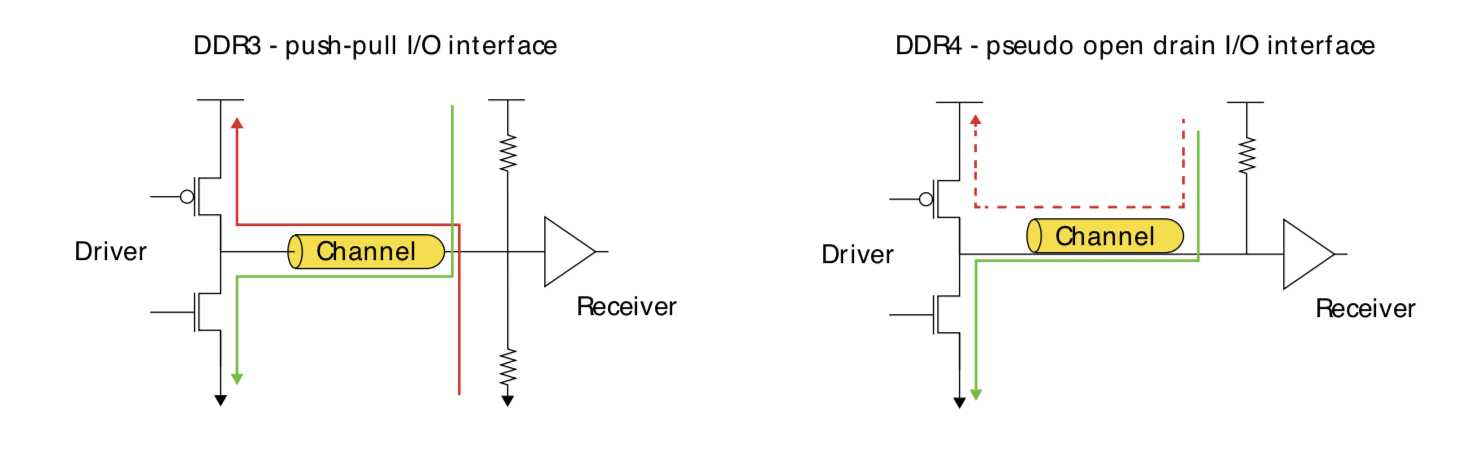

在 DDR4 中,数据线 [DQ] 的端接样式从 CTT(中心抽头端接,也称为 SSTL 系列螺柱端接逻辑)更改为 POD(伪开漏)。这样做是为了提高高速信号完整性并节省 IO 功率。这不是同类产品中的第一个,GDDR5(图形 DRAM)也使用 POD

Figure 9: SSTL in DDR3 vs POD in DDR4 [来源:Micron datasheet]

这意味着,在 DDR3 中,Vdd/2 用作电压参考来决定 [DQ] 信号是 0 还是 1。再看一下图 8 的左侧,接收器本质上是一个分压电路。

但在DDR4中,接收器上没有分压电路。相反,它有一个内部电压基准,用来决定数据线[DQ]上的信号是0还是1。这个电压基准被称为VrefDQ。VrefDQ可以使用模式寄存器MR6来设置,在VrefDQ校准阶段,它需要由内存控制器正确设置。

Read/Write 训练

至此,初始化过程完成,DRAM 处于空闲状态,但内存仍然无法运行。控制器和 PHY 必须执行一些更重要的步骤,然后才能可靠地将数据写入 DRAM 或从 DRAM 中读取。这个重要的阶段被称为读写训练(或内存训练或初始校准),控制器(或PHY)在此过程中。

• 1.运行算法以对齐DRAM的时钟[CK]和数据选通[DQS]。

• 2.运行算法并计算出正确的 DRAM 读写延迟。

• 3.读取数据眼的中心。

• 4.如果信号完整性不好并且无法可靠地写入或读取数据,则报告错误。

本节是关于状态机中的以下圆圈

Figure 10: read/wirte 训练状态

为什么需要read/write训练?

让我们仔细看看我们的示例系统。下图显示了数据信号和地址/命令信号如何在 ASIC/处理器和 DIMM 上的 DRAM 之间连接。

• Data 和 DataStrobe [DQ & DQS] 以星形拓扑连接到每个存储器,因为每个存储器连接到 72 条数据线的不同部分.

• DIMM 上的时钟、命令和地址线 [A、CK、CKE、WE、CSn] 使用称为 fly-by 路由拓扑的技术连接。这样做是因为 DIMM 上的所有 DRAM 共享相同的地址线,并且需要 fly-by 路由以实现更好的信号完整性和高速。

Figure 11: 详细示例系统

因此,从ASIC/处理器的角度来看,DIMM上的每个DRAM内存都位于不同的距离。或者从DIMM的角度来看,DIMM上每个DRAM的时钟和数据之间的偏移是不同的。

DRAM是一个相当愚蠢的设备。假设你打算进行WRITE操作,在初始化过程中,你要通过编程它的一个模式寄存器来告诉DRAM的CAS写入延迟是什么(CWL是DRAM输入端列地址和数据之间的时间延迟),并且你必须在任何时候都遵守这个时间参数。内存控制器需要考虑电路板走线延迟和fly-by路由延迟,并以正确的偏差启动地址和数据,以便地址和数据以它们之间的 CWL 延迟到达内存。

例如,如果你将CAS写延迟编程为9,一旦ASIC/uP启动列地址,它将需要在不同的时间启动不同的数据位,以便它们都在CWL为9时到达DRAM。

对于READ,也需要做与上述类似的事情。由于DIMM上的每个DRAM位于不同的距离,当发出READ时,DIMM上的每个DRAM将在不同的时间看到READ命令,随后每个DRAM的数据将在不同的时间到达ASIC/处理器。在初始校准期间,ASIC/Processor 找出每个DRAM的延迟,并相应地训练其内部电路,以便它在正确的时刻锁住来自不同DRAM的数据。

对于read/write训练,Controller/PHY IP 通常提供多种算法。最常见的是:

• 1. Write Leveling 写调平

• 2. MPR Pattern Write MPR 模式写入

• 3. Read Centering 读居中

• 4. Write Centering 写居中

上述所有的算法都是由内存控制器执行的,通常只需要你通过一个寄存器来启用/禁用单个算法,并在报告失败时采取措施。以下部分更详细地介绍了启用这些算法时控制器会做什么。

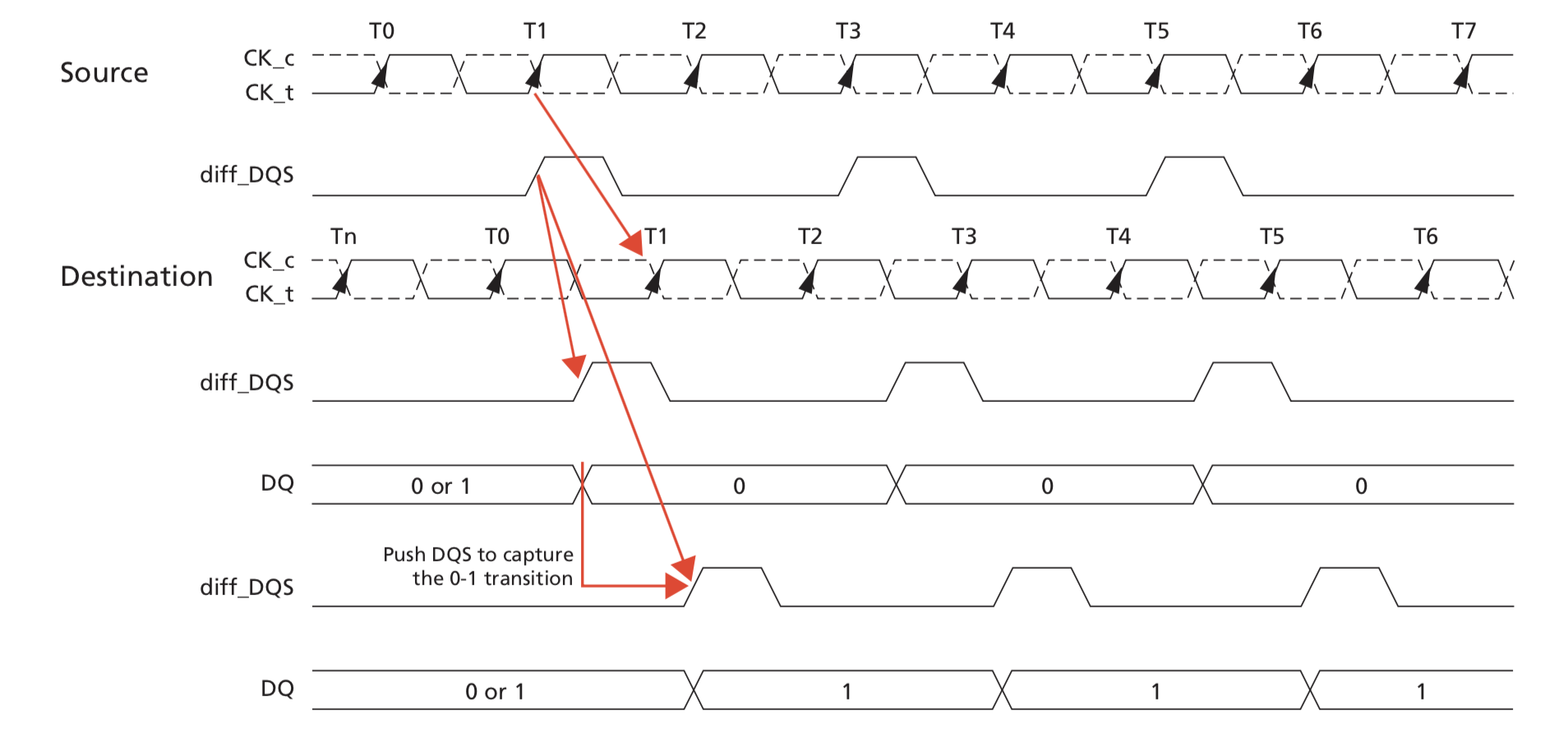

Write Leveling 写调平

写入 DRAM 时,不能违反的重要时序参数是 tDQSS。 tDQSS 是 DataStrobe (DQS) 相对于时钟 (CK) 的位置。 tDQSS 必须在规范中定义的 tDQSS(MIN) 和 tDQSS(MAX) 范围内。如果违反 tDQSS 并超出范围,则可能会将错误的数据写入内存.

由于 DIMM 上的每个 DRAM 的时钟到Data/DataStrobe 偏差都不同,因此内存控制器需要训练自己,以便它可以补偿这种偏差并在 DIMM 上的每个 DRAM 的输入处保持 tDQSS。

当你在控制器中启用 write-leveling 时,它会执行以下步骤:

• 1. 对MR1进行模式寄存器写入,将第7位设置为1,这将使DRAM进入write-leveling模式。在write-leveling模式下,当 DRAM 看到 DataStrobe (DQS) 时,它会使用它对时钟 (CK) 进行采样,并通过 DQ 总线将采样值返回给控制器。

• 2. 然后控制器发送一系列 DQS 脉冲。由于 DRAM 处于write-leveling模式,它使用 DQS 对 CK 的值进行采样,并通过 DQ 总线将该采样值(1 或 0)返回给控制器。

• 3. 然后控制器

•查看 DRAM 返回的 DQ 位的值

•要么增加或减少 DQS 延迟和

•一段时间后启动下一组 DQS 脉冲

• 4. RAM再次采样CK,并通过DQ总线返回采样值

• 5. 重复步骤 2 到 4,直到控制器看到 0 到 1 的转换。此时,控制器锁定 DQS 延迟设置,该DRAM设备就实现了write-leveling。

• 6. 然后为整个 DIMM 的每个 DQS 重复步骤 2 到 5,以完成wite-leveing过程

• 7. 通过将 0 写入 MR1[7],DRAM 最终退出write-leveling模式

下图显示了 write-leveling 的概念。

Figure 12: write-leveling

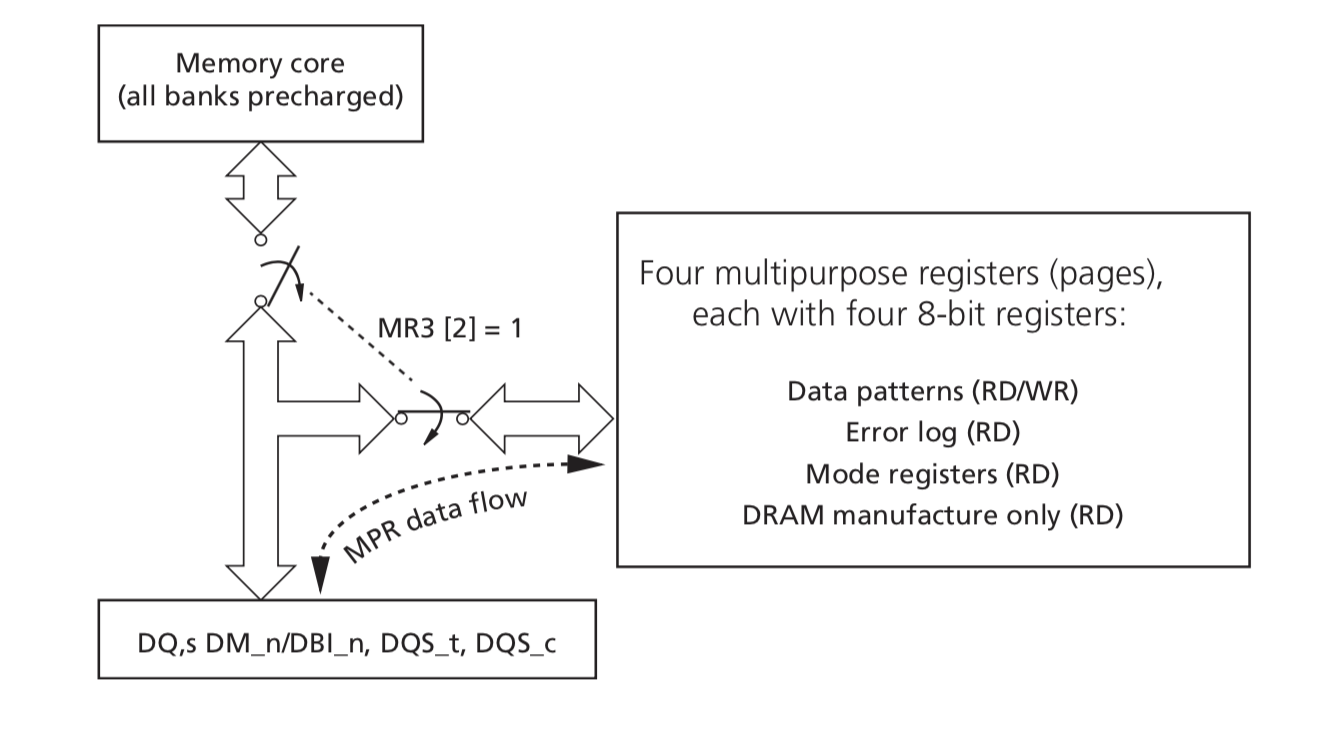

MPR 模式写入

MPR(多用途寄存器)模式写入并不完全是一种校准算法。它通常是在读取居中和写入居中之前执行的步骤。

DDR4 DRAM 包含四个 8 位可编程寄存器,称为 MPR 寄存器,用于 DQ 位训练(即读写居中)。通过设置模式寄存器 MR3[2] = 1 启用 MPR 访问模式。启用此模式后,发送到 DRAM 的 READ 和 WRITE 被转移到多用途寄存器而不是内存bank。

Figure 13: MPR read/write

Read Centering 读居中

读取居中的目的是训练控制器(或 PHY)中的内部读取捕获电路来捕获数据眼中心的数据。内存控制器(或 PHY):

• 1. 启用模式寄存器MR3中的第2位,使DRAM从多用途寄存器(MPR)而不是DRAM存储器中返回数据。

• 2. 然后启动一个连续的READ流。存储器返回在前一个 MPR 模式写入步骤中写入的模式。假设这种模式是交替的 1-0-1-0-...

• 3. 在读取过程中,内部读取捕获电路要么增加或减少内部读取延迟寄存器,以找到数据眼的左右边缘。

• 4. 当检测到眼图边缘时,读取延迟寄存器会被适当设置,以确保在眼图中心捕获数据。

• 5. 对每个 DQ 数据位重复上述步骤。

Write Centering 写居中

与读居中步骤类似,写居中的目的是为每个数据位设置写延迟,使写数据居中于 DRAM 设备上相应的写选通沿上。

在写入居中期间,PHY 连续执行以下 WRITE-READ-SHIFT-COMPARE 循环:

• 1. 启动连续的 WRITE 和 READ 流

• 2.逐渐改变数据位的写入延迟

• 3.将读回的数据与写入的数据进行比较

从上面的循环中,PHY可以确定它在什么写延迟范围内读回好的数据,因此它可以算出写数据眼的左边缘和写边缘。利用这个数据,DQ被集中到DQS上进行写入。

定期校准

在诸如网络交换机或路由器这样的设备中,在其运行过程中,电压和温度可能会发生变化。为了保持信号完整性和数据访问的可靠性,一些在初始化和读/写训练中训练的参数必须重新运行。内存控制器和PHY IPs通常提供以下两个定期校准过程。

• 1. 周期性 ZQ - 也称为 ZQ 校准短路 (ZQCS)。它用于定期运行 ZQ 校准以调整前面描述的 240Ω 电阻器。

• 2. 定期读居中 - 重新计算读取延迟和其他读取相关参数

启用定期校准是可选的,因为如果你知道你的设备将被部署在稳定的温度条件下,那么最初的ZQ校准和读/写训练就足够了。

通常,内存控制器或 PHY 允许您设置定时器并通过其寄存器启用定期校准。设置定时器后,每次定时器到期时都会运行定期校准。

总结

在使用DRAM之前,有4个步骤需要完成:

• 1. 上电和初始化

• 2. ZQ校准

• 3. Vref DQ 校准

• 4. Read/Write训练

一旦完成,系统就正式处于空闲状态并可以运行。根据设备部署的条件,您可能需要启用定期校准。