热门标签

热门文章

- 1关于转行产品经理的十大顾虑《上》_宋紫薇图

- 2Git切换分支(创建本地分支,远程分支,合并分支代码)_git切换branch

- 3六西格玛黑带考试试题|优思学院_在研究完改进措施后,决定进行试生产。试生产半月后,采集了100个数据。发现过程仍

- 4登录安全分析报告:创蓝云智注册

- 5Facebook术语表_加速投放缩略词

- 6Java Web应用开发课程大作业(电商品牌管理系统)_javaweb大作业

- 7中级工程师职称评定条件及申报资料,伴德诚

- 8应届生面试时如何破解没有工作经验的困局_应届毕业生面试,缺少经验该咋办

- 9克隆别人的项目并上传到自己的仓库_git克隆别人的项目上传到自己的仓库

- 10数据结构之——堆(Heap)_heap数据结构

当前位置: article > 正文

基于FPGA的任意进制计数器设计VHDL代码Quartus仿真_使用quartus实现000到999的随机数数码管

作者:笔触狂放9 | 2024-05-29 20:14:05

赞

踩

使用quartus实现000到999的随机数数码管

名称:基于FPGA的任意进制计数器设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

利用VHDL语言,实现0~9901任意进制8421BCD计数译码显示电路,并将计数器输出的8421BCD进行共阳数码管显示,要求

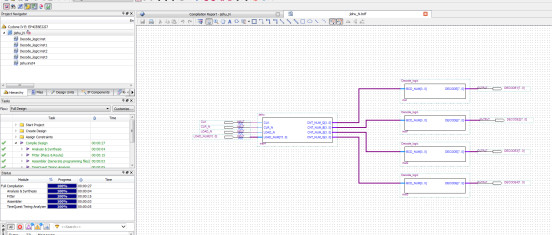

1、计数器具有同步置数功能、异步清零功能,用VHDL实现计数逻辑,并阐述设计原理,给出关键 block diagran设计框图。

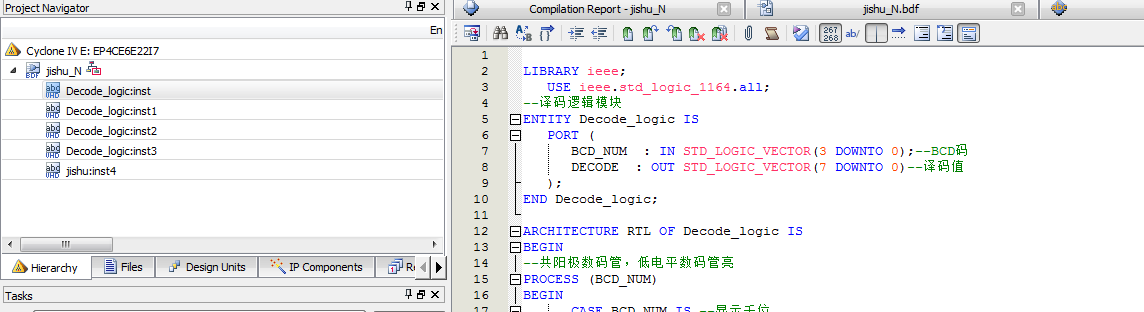

2、8421BCD码7段译码部分可以参见74LS48功能,用VHDL实现译码逻辑,并阐述设计原理,给出关键 blockdiagram设计框图。

3、译码输岀后驱动的数码管为共阳极数码管,阐述电路原理,给出相应编码方式。

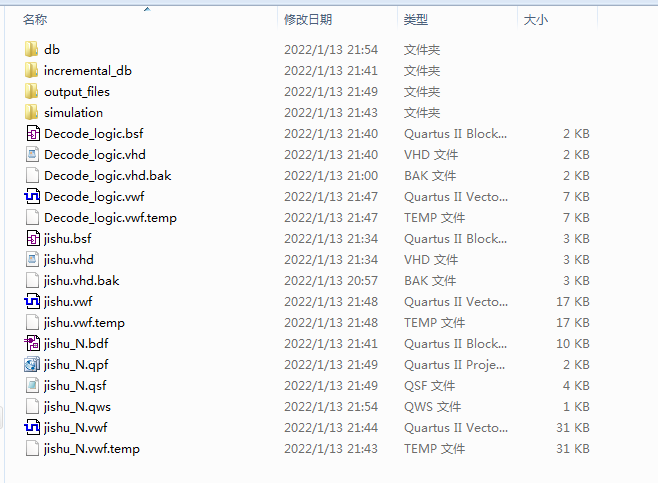

1. 工程文件

2. 程序文件

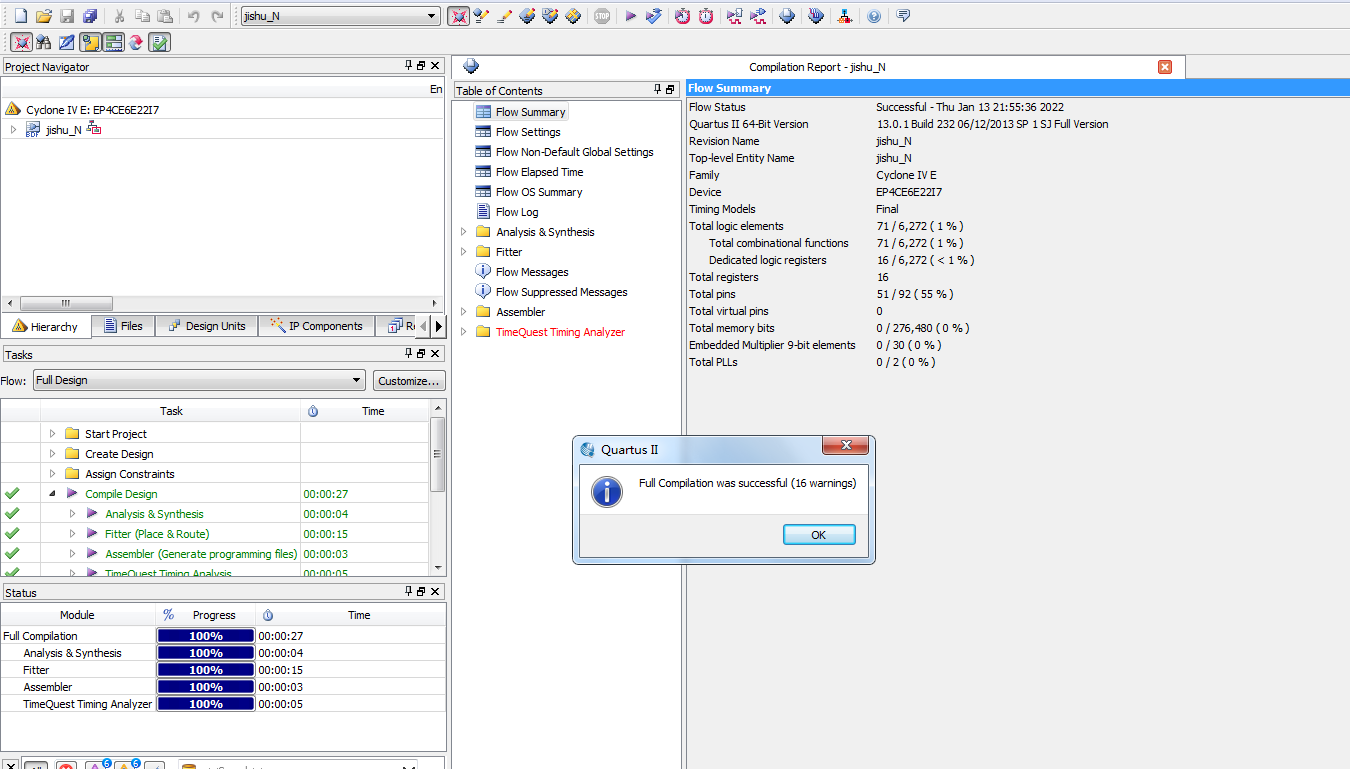

3. 程序编译

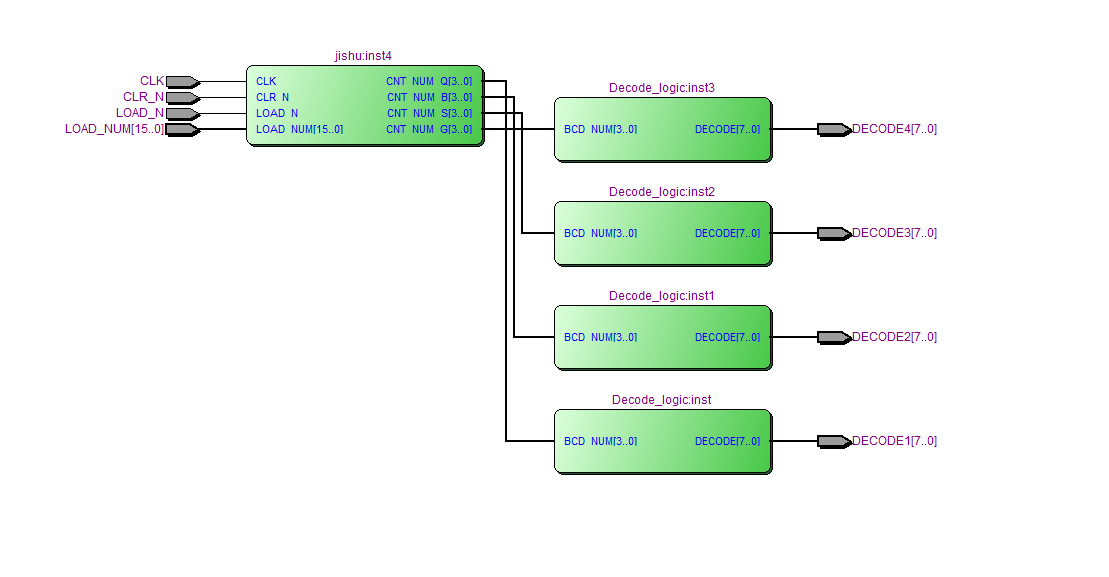

4. RTL图

5. 仿真图

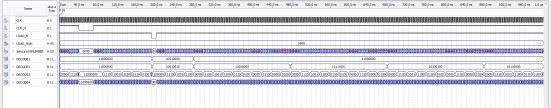

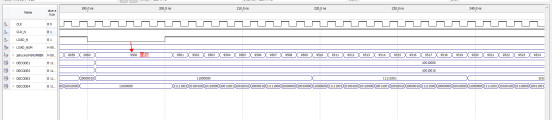

整体仿真图

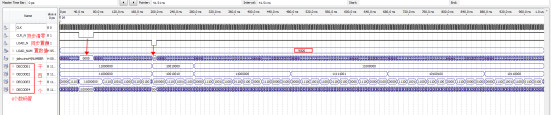

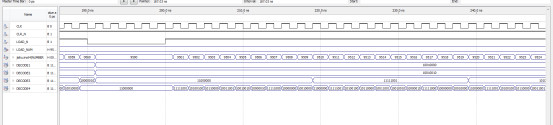

计数模块仿真图

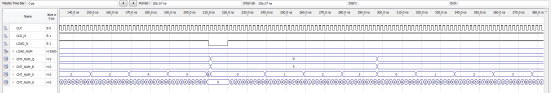

译码逻辑模块仿真图

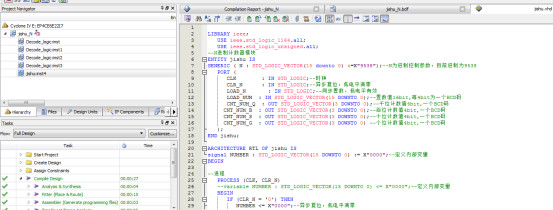

部分代码展示:

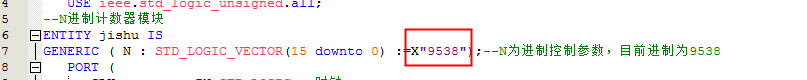

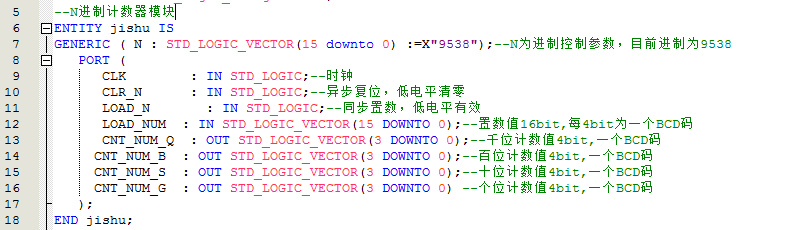

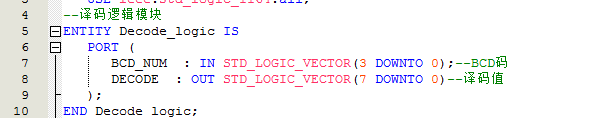

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --N进制计数器模块 ENTITY jishu IS GENERIC ( N : STD_LOGIC_VECTOR(15 downto 0) :=X"9538");--N为进制控制参数,目前进制为9538 PORT ( CLK : IN STD_LOGIC;--时钟 CLR_N : IN STD_LOGIC;--异步复位,低电平清零 LOAD_N : IN STD_LOGIC;--同步置数,低电平有效 LOAD_NUM : IN STD_LOGIC_VECTOR(15 DOWNTO 0);--置数值16bit,每4bit为一个BCD码 CNT_NUM_Q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--千位计数值4bit,一个BCD码 CNT_NUM_B : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--百位计数值4bit,一个BCD码 CNT_NUM_S : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--十位计数值4bit,一个BCD码 CNT_NUM_G : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --个位计数值4bit,一个BCD码 ); END jishu; ARCHITECTURE RTL OF jishu IS signal NUMBER : STD_LOGIC_VECTOR(15 DOWNTO 0) := X"0000";--定义内部变量 BEGIN --进程 PROCESS (CLK, CLR_N) --variable NUMBER : STD_LOGIC_VECTOR(15 DOWNTO 0) <= X"0000";--定义内部变量 BEGIN IF (CLR_N = '0') THEN NUMBER <= X"0000";--异步复位,低电平清零 ELSIF (CLK'EVENT AND CLK = '1') THEN IF (LOAD_N = '0') THEN--同步置数,低电平有效 NUMBER <= LOAD_NUM;--置数值 ELSIF (NUMBER >= N) THEN--是否计数到对应进制值 NUMBER <= X"0000"; --回到0000 ELSIF (NUMBER(11 DOWNTO 0) = X"999") THEN--计数到999 NUMBER(15 DOWNTO 12) <= NUMBER(15 DOWNTO 12) + X"1";--千位加1 NUMBER(11 DOWNTO 0) <= X"000";--回到000 ELSIF (NUMBER(7 DOWNTO 4) = X"9" AND NUMBER(3 DOWNTO 0) = X"9") THEN--计数到99 NUMBER(11 DOWNTO 8) <= NUMBER(11 DOWNTO 8) + X"1";--百位加1 NUMBER(7 DOWNTO 0) <= X"00";--回到00 ELSIF (NUMBER(3 DOWNTO 0) = X"9") THEN--计数到9 NUMBER(7 DOWNTO 4) <= NUMBER(7 DOWNTO 4) + X"1";--十位加1 NUMBER(3 DOWNTO 0) <= X"0";--个位回到0 ELSE NUMBER(3 DOWNTO 0) <= NUMBER(3 DOWNTO 0) + X"1";--个位加1 END IF;

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/笔触狂放9/article/detail/643787?site

推荐阅读

相关标签